SBAU361 December 2020 ADC3664

7 Test Pattern

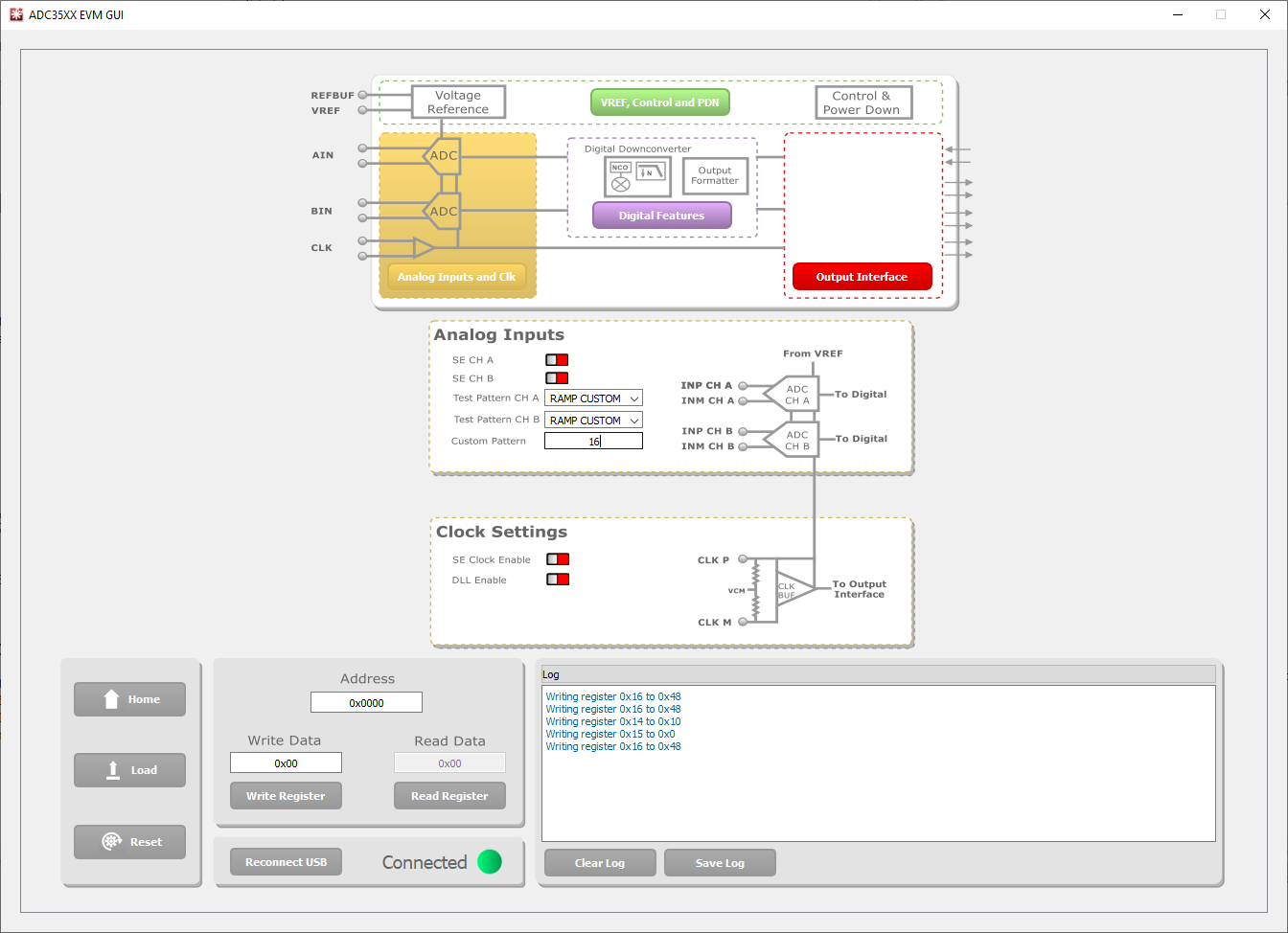

It is often useful to utilize test patterns to help verify the correct receipt of digital data at the microcontroller or FPGA. A ramp pattern can be enabled by following these steps:

- Click the yellow button "Analog Inputs and Clk".

- Next to "Test Pattern CHA", click the drop down menu, and select "RAMP CUSTOM". This can be done for "Test Pattern CHB" as well.

- In the field next to "Custom Pattern", enter the number "16".

- The digital ramp pattern is now

enabled on the ADC. The output of the ADC is now a 14 bit, incrementing ramp

pattern.

Figure 7-1 ADC35XXEVM GUI 1.0 Ramp

Pattern

Figure 7-1 ADC35XXEVM GUI 1.0 Ramp

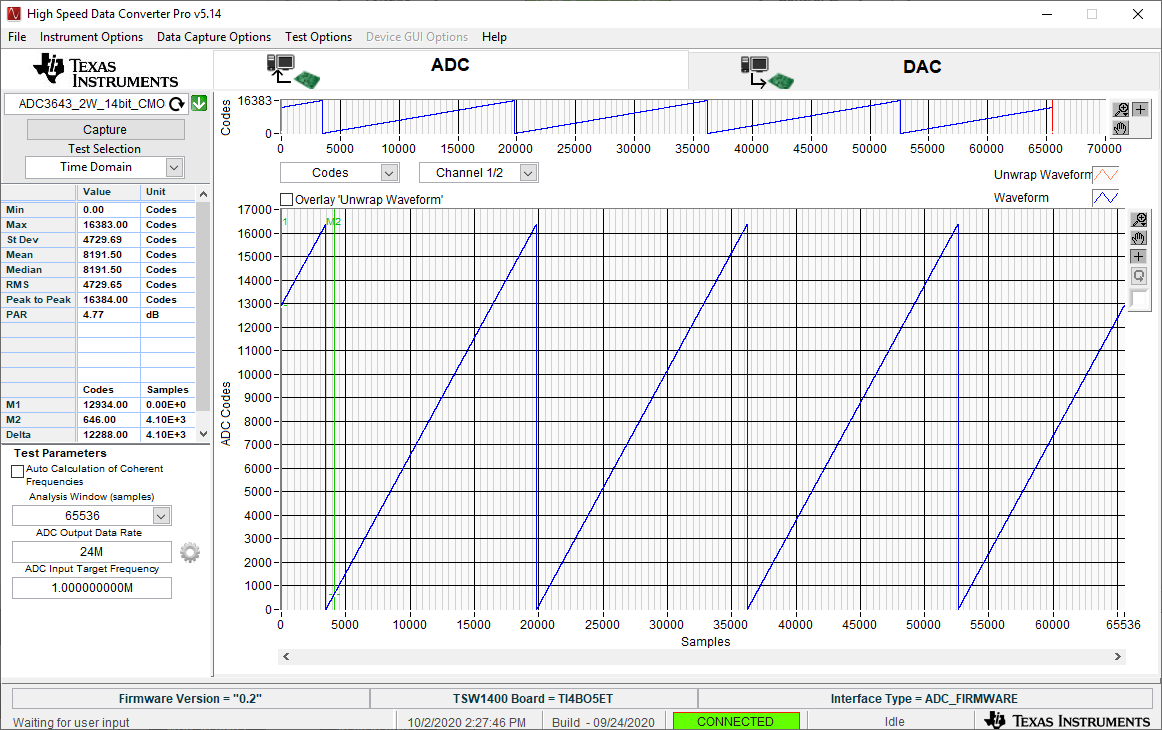

Pattern - In HSDC Pro,

the ramp pattern can now be seen when data is captured. These same steps apply to

any data output mode (Bypass, Real Decimation and Complex Decimation).

Figure 7-2 HSDC Pro Digital Ramp

Pattern

Figure 7-2 HSDC Pro Digital Ramp

Pattern