KOKT008 january 2023 TPS543B22 , TPS548A28 , TPS56121

5 D-CAP3 제어 아키텍처

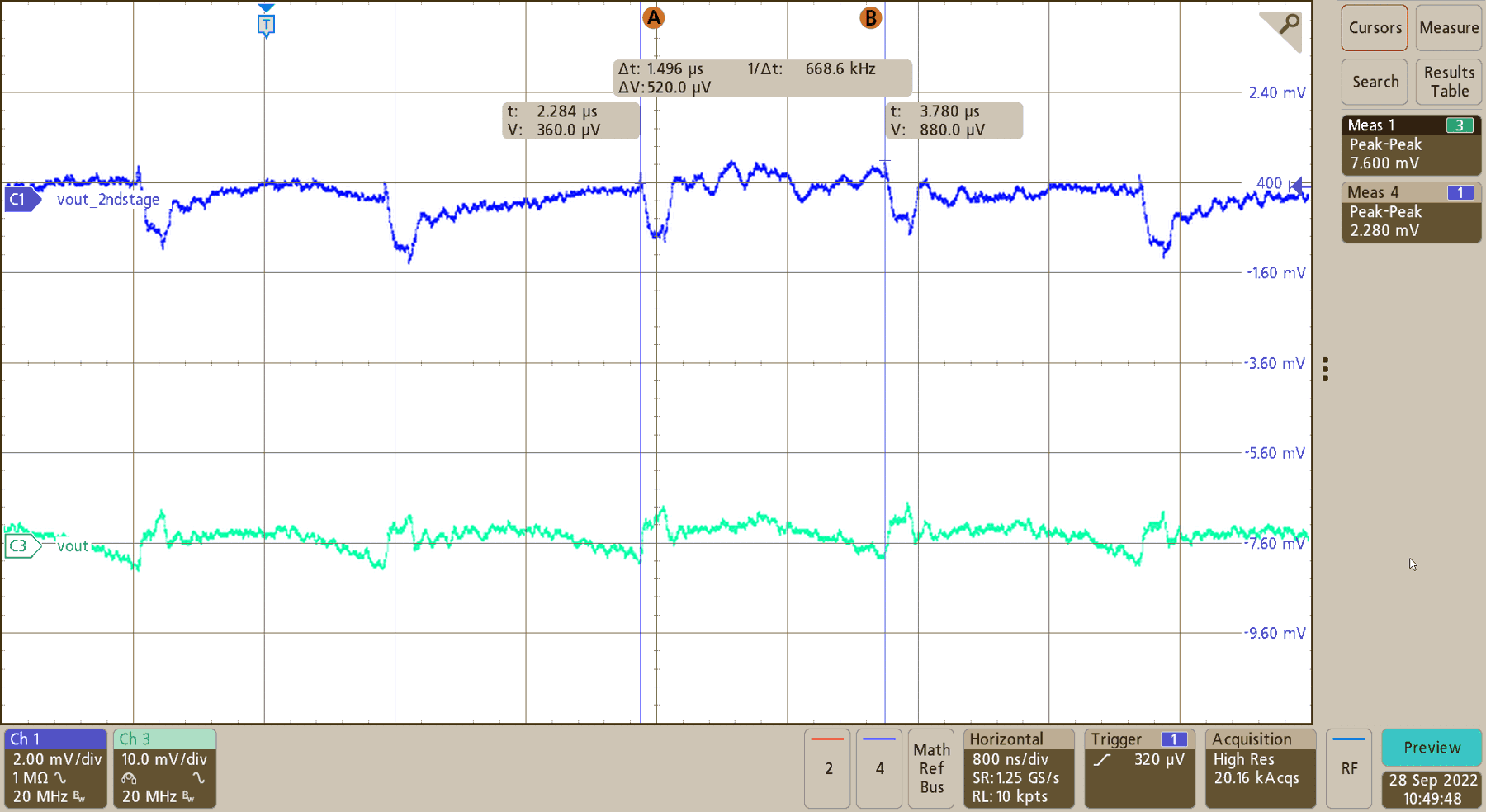

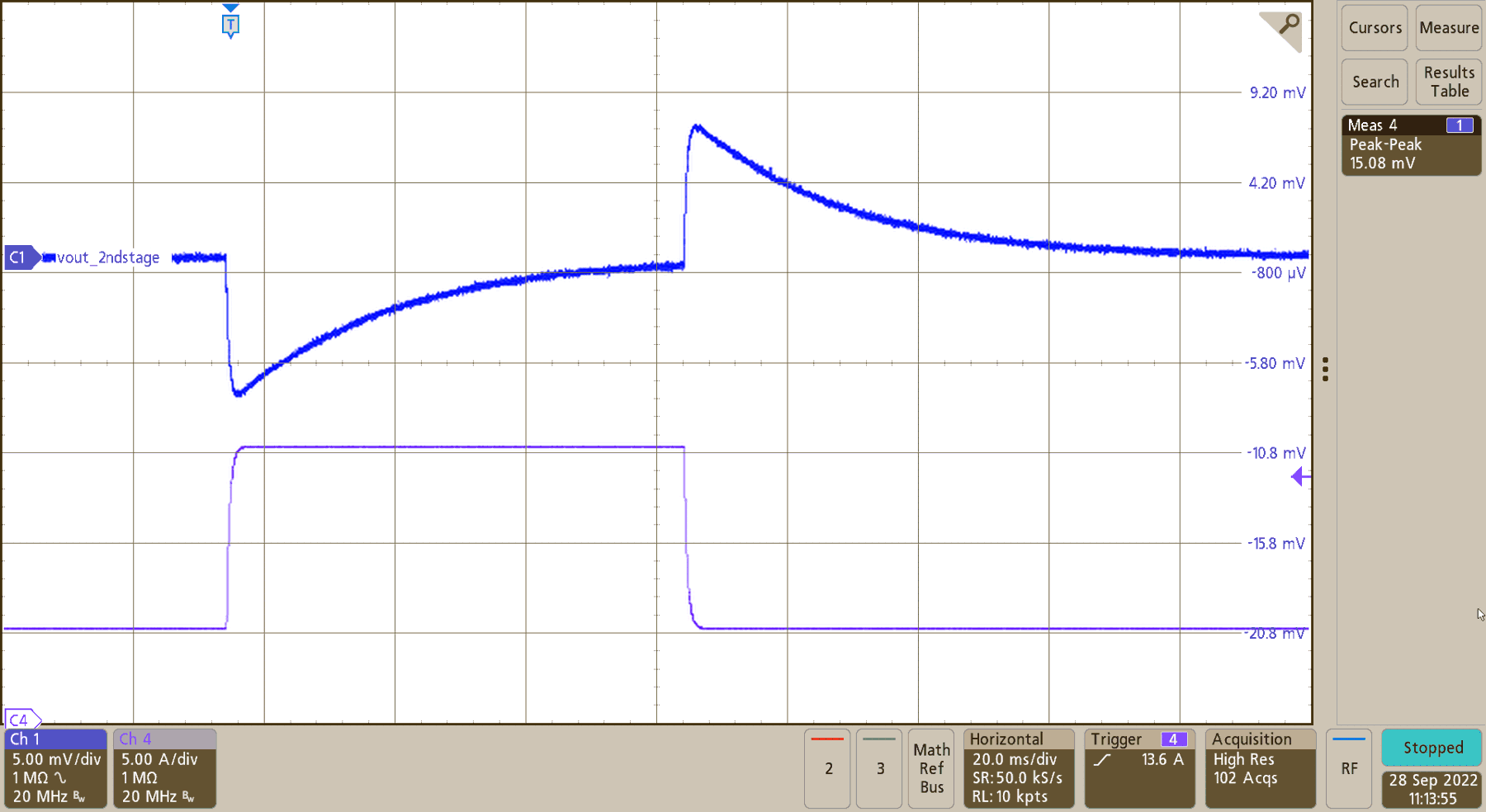

D-CAP3는 원샷 타이머를 사용해 입력 전압과 출력 전압에 비례하는 온타임 펄스를 생성합니다. 하강 피드백 전압이 레퍼런스 전압과 같으면 새로운 PWM 온펄스가 생성됩니다. 램프는 출력 인덕터에 의해 에뮬레이트됩니다. 내부 리플 주입 회로의 신호는 오프셋 전압이 제거된 콤퍼레이터로 직접 공급되어 커패시터의 ESR에서 출력 전압 리플의 필요성을 줄여줍니다. D-CAP3 및 기타 COT(고정 온타임) 컨버터의 한 가지 장점은 추가 루프 보상 회로가 필요하지 않는다는 것입니다. 하지만 장치가 이 기능을 지원하고 출력 전압 피드백 저항 분할기 네트워크에서 피드 포워드 커패시턴스를 추가하는 경우, 제어 루프에 조정 가능 램프로 조정하는 기능이 있을 수 있습니다. 추가 필터 없는 TPS548A28의 출력 전압 피크 투 피크 리플은 7.6mV입니다. 추가 필터를 적용한 상태에서 출력 전압 리플은 2.3mV(그림 4 그림 참조)입니다. 이 경우, TPS548A28 설계는 안정성을 보장하기 위해 조정할 필요가 없습니다. 그림 5은(는) 동일한 10A 부하 단계를 이전 컨버터로 했을 때 부하 과도 파형을 나타내며, 두 번째 단계 필터 구현 이후 출력 전압 파형에는 불안정성 징후가 전혀 보이지 않습니다.

그림 4 두 번째 단계 필터를 추가했을 때와 추가하지 않았을 때의 TPS548A28 출력 전압 리플.

그림 4 두 번째 단계 필터를 추가했을 때와 추가하지 않았을 때의 TPS548A28 출력 전압 리플. 그림 5 D-CAP3 제어를 사용했을 때 TPS548A28의 과도 응답.

그림 5 D-CAP3 제어를 사용했을 때 TPS548A28의 과도 응답.