KOKT008 january 2023 TPS543B22 , TPS548A28 , TPS56121

3 2차 단계 필터 설계하기

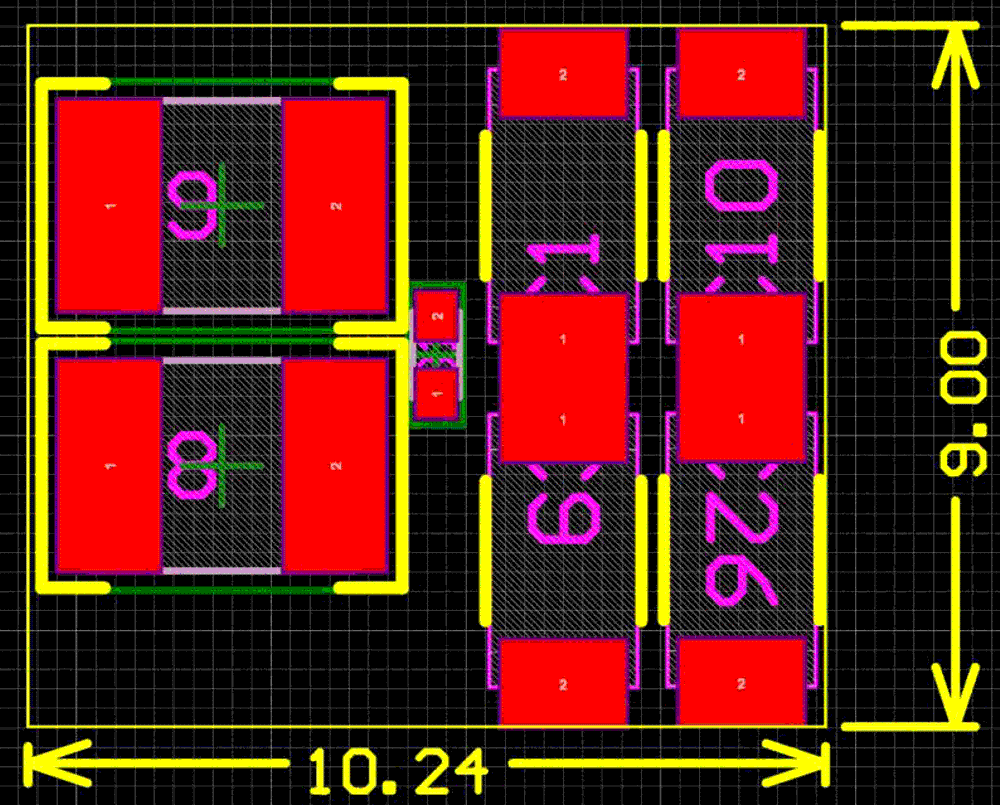

낮은 ESR(등가 직렬 저항) 세라믹 출력 커패시터를 사용하더라도 벅 컨버터의 인덕터 및 커패시터(LC) 출력 필터를 사용하여 낮은 출력 전압 리플을 달성하는 것은 실용적이지 않습니다. 설계자는 5mV 미만의 출력 리플을 달성하기 위해 2차 단계 LC 필터를 사용해야 할 가능성이 높습니다. 2차 단계 필터 설계 또는 리플 측정 기법에 관한 자세한 내용은 참고 자료 섹션을 참조하십시오. 2차 단계 필터의 인덕터 값은 방정식 1을(를) 사용해 계산하고 L2에 대해 풀 수 있습니다. 인덕터 L2는 2차 단계 인덕터, C1은 벅 컨버터의 1차 단계 출력 커패시터이며, C2는 2차 단계 커패시터 네트워크입니다. 세 가지 설계에서 모두 동일한 2차 단계 필터가 사용되어(표 1 참조) 92mm2 의 회로 기판 면적을 차지합니다(그림 1참조).

방정식 1.

표 1 컨버터 제어 아키텍처와 2차 단계 필터.

| 부품 번호 | 제어 아키텍처 | 스위칭 주파수 | 2차 단계 인덕턴스 | 2차 단계 커패시턴스 |

|---|---|---|---|---|

| TPS548A28 | D-CAP3 | 800 kHz | 2 x 0.68 µH | 4x 100 µF + 0.1 µF |

| TPS543B22 | ACM | 1000 kHz | 2 x 0.68 µH | 4x 100 µF + 0.1 µF |

| TPS56121 | 전압 모드 | 500 kHz | 2 x 0.68 µH | 4 x 100 µF + 0.1 µF |

그림 1 2차 단계 필터가 회로 기판에서 차지하는 면적 92mm2.

그림 1 2차 단계 필터가 회로 기판에서 차지하는 면적 92mm2.2차 단계 인덕터 값(L2)을 선택하고 부품 조립이 완료되면, 다음 단계는 안정성을 보장하기 위해 2차 단계 인덕턴스 및 커패시턴스를 추가하여 DC/DC 컨버터의 제어 루프를 재보상하는 것입니다. 중요한 것은 각 제어 아키텍처별로, 필요에 따라 2차 단계 필터를 추가한 후에 제어 루프를 재보상하는 고유한 기법이 있다는 점입니다. 각 제어 아키텍처별로 출력 전압 리플, 효율성 페널티 및 안정성을 평가하고 결과를 요약했습니다.