ZHCSUX9 February 2024 TMUXHS4446

PRODUCTION DATA

7.2.3 Application Curves

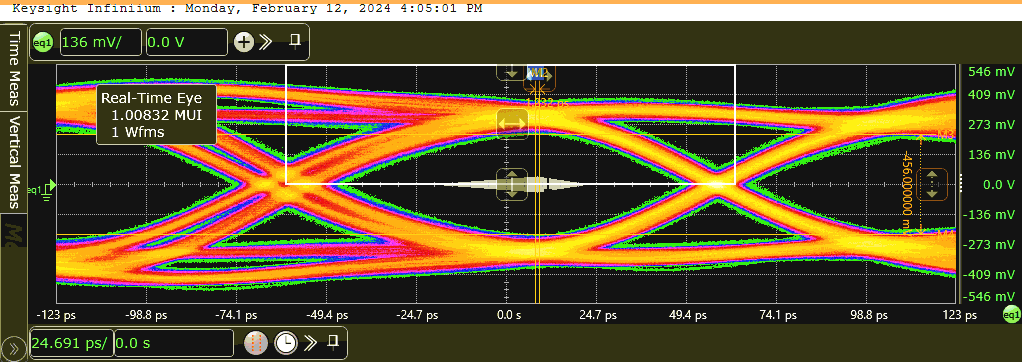

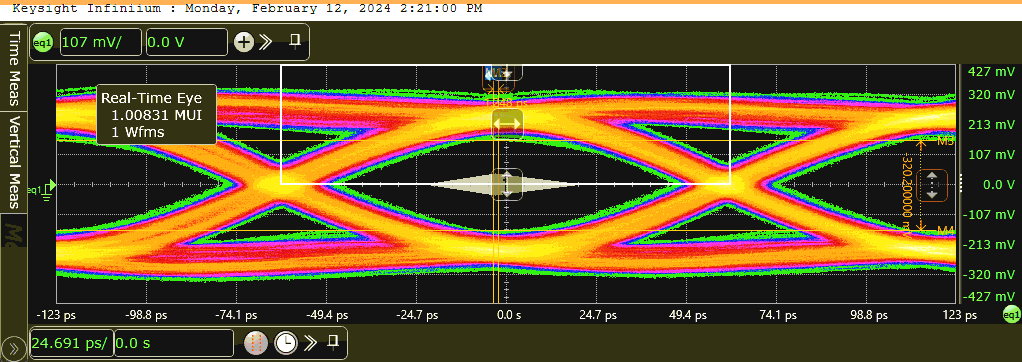

Figure 7-5 through Figure 7-8 illustrate DisplayPort 1.4 Tx compliance results at HBR3 8.1Gbps. Eye diagrams (in scope, no cable model) are compared from the baseline setup and from the same setup plus TMUXHS4446 board. The diagrams are for lane 0. Other lanes also result in to similar eye diagrams. Jitter degradation through TMUXHS4446 is minimal.

Figure 7-5 8.1Gbps DP Compliance Setup -

Baseline (no DUT)

Figure 7-5 8.1Gbps DP Compliance Setup -

Baseline (no DUT) Figure 7-7 8.1Gbps DP Compliance Eye Diagram -

Baseline Setup (no DUT)

Figure 7-7 8.1Gbps DP Compliance Eye Diagram -

Baseline Setup (no DUT) Figure 7-6 8.1Gbps DP Compliance Setup - with

TMUXHS4446

Figure 7-6 8.1Gbps DP Compliance Setup - with

TMUXHS4446  Figure 7-8 8.1Gbps DP Compliance Eye Diagram -

with TMUXHS4446

Figure 7-8 8.1Gbps DP Compliance Eye Diagram -

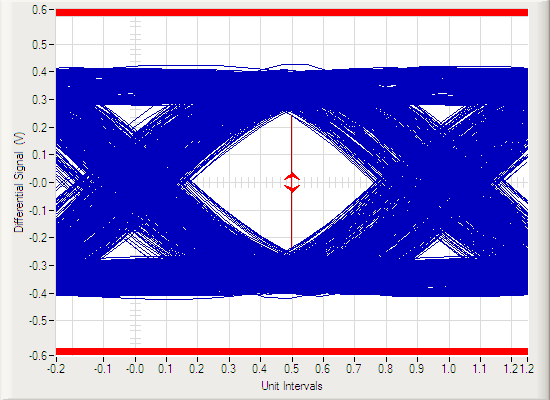

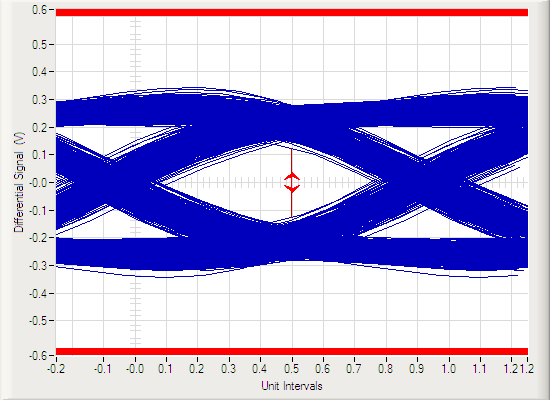

with TMUXHS4446Figure 7-9 through Figure 7-12 illustrate USB 3.x Gen2 Tx compliance results at 10Gbps. Eye diagrams (in scope, near end) are compared from the baseline setup and from the same setup plus TMUXHS4446 board. The diagrams are for lane 0. Other lanes also result in to similar eye diagrams. Jitter degradation through TMUXHS4446 is minimal.

Figure 7-9 10Gbps USB Compliance Setup - Baseline (no DUT)

Figure 7-9 10Gbps USB Compliance Setup - Baseline (no DUT) Figure 7-11 10Gbps USB Compliance Eye Diagram -

Baseline Setup (no DUT)

Figure 7-11 10Gbps USB Compliance Eye Diagram -

Baseline Setup (no DUT) Figure 7-10 10Gbps USB Compliance Setup - with

TMUXHS4446

Figure 7-10 10Gbps USB Compliance Setup - with

TMUXHS4446 Figure 7-12 10Gbps USB Compliance Eye Diagram -

with TMUXHS4446

Figure 7-12 10Gbps USB Compliance Eye Diagram -

with TMUXHS4446