ZHCSFR2B December 2016 – March 2018 LMR23630-Q1

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Product Portfolio

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Fixed-Frequency Peak-Current-Mode Control

- 8.3.2 Adjustable Frequency

- 8.3.3 Adjustable Output Voltage

- 8.3.4 Enable/Synchronization

- 8.3.5 VCC, UVLO

- 8.3.6 Minimum ON-time, Minimum OFF-time and Frequency Foldback at Dropout Conditions

- 8.3.7 Power Good (PGOOD)

- 8.3.8 Internal Compensation and CFF

- 8.3.9 Bootstrap Voltage (BOOT)

- 8.3.10 Overcurrent and Short-Circuit Protection

- 8.3.11 Thermal Shutdown

- 8.4 Device Functional Modes

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1 Design Requirements

- 9.2.2

Detailed Design Procedure

- 9.2.2.1 Custom Design With WEBENCH® Tools

- 9.2.2.2 Output Voltage Setpoint

- 9.2.2.3 Switching Frequency

- 9.2.2.4 Inductor Selection

- 9.2.2.5 Output Capacitor Selection

- 9.2.2.6 Feed-Forward Capacitor

- 9.2.2.7 Input Capacitor Selection

- 9.2.2.8 Bootstrap Capacitor Selection

- 9.2.2.9 VCC Capacitor Selection

- 9.2.2.10 UVLO Setpoint

- 9.2.3 Application Curves

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

订购信息

8.3.4 Enable/Synchronization

The voltage on the EN pin controls the ON or OFF operation of LMR23630-Q1. A voltage less than 1 V (typical) shuts the device down while a voltage higher than 1.6 V (typical) is required to start the regulator. The EN/SYNC pin is an input and cannot be left open or floating. The simplest way to enable the operation of the LMR23630-Q1 is to connect the EN to VIN. This allows self-start-up of the LMR23630-Q1 when VIN is within the operation range.

Many applications benefit from the employment of an enable divider RENT and RENB (Figure 16) to establish a precision system UVLO level for the converter. System UVLO can be used for supplies operating from utility power as well as battery power. It can be used for sequencing, ensuring reliable operation, or supply protection, such as a battery discharge level. An external logic signal can also be used to drive EN input for system sequencing and protection.

Figure 16. System UVLO by Enable Divider

Figure 16. System UVLO by Enable Divider

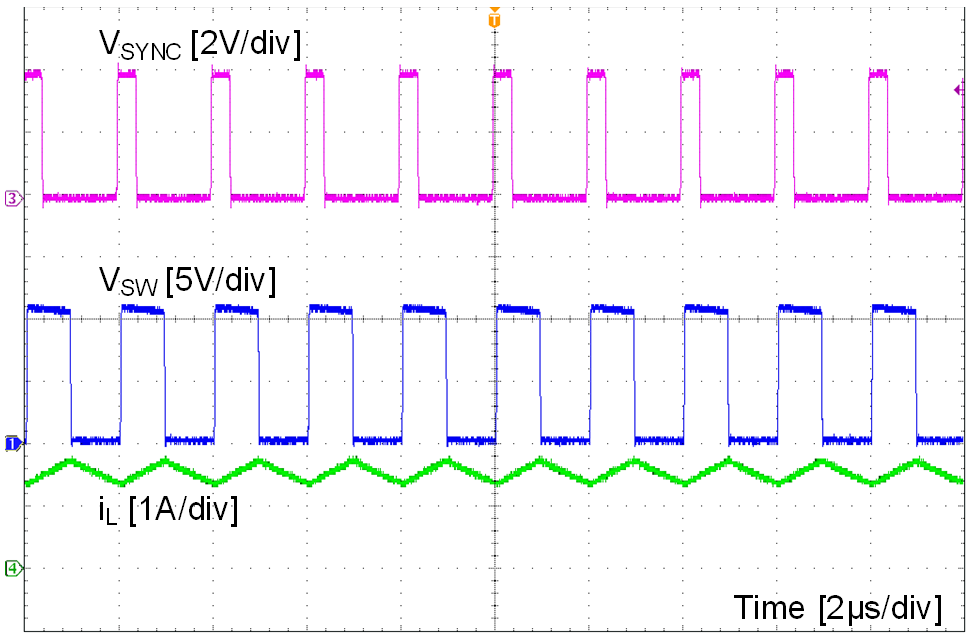

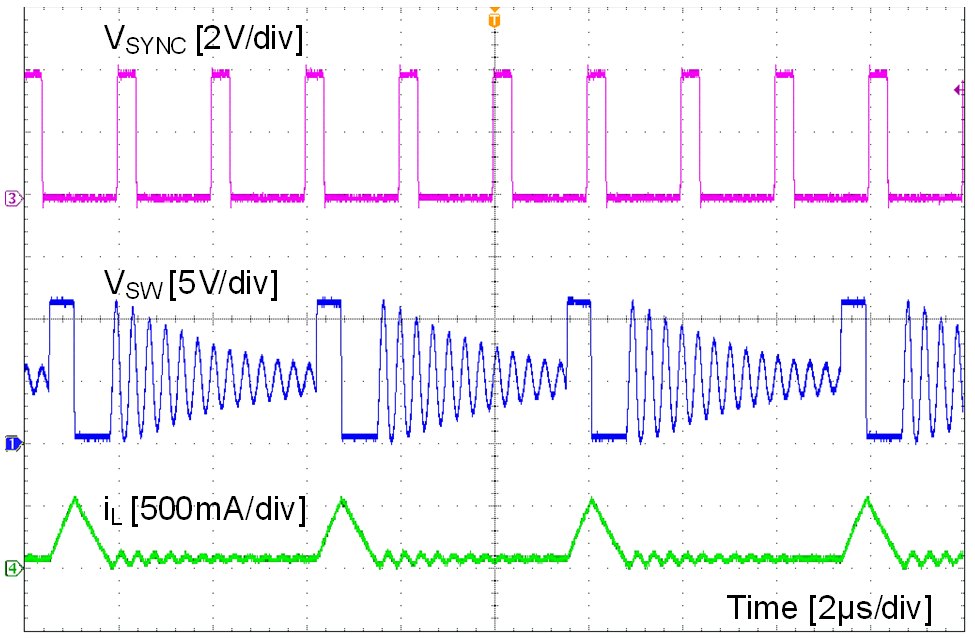

The EN pin also can be used to synchronize the internal oscillator to an external clock. The internal oscillator can be synchronized by AC coupling a positive edge into the EN pin. The AC coupled peak-to-peak voltage at the EN pin must exceed the SYNC amplitude threshold of 2.8 V (typical) to trip the internal synchronization pulse detector, and the minimum SYNC clock ON and OFF time must be longer than 100ns (typ). A 3.3 V or a higher amplitude pulse signal coupled through a 1 nF capacitor CSYNC is a good starting point. Keeping RENT // RENB (RENT parallel with RENB) in the 100-kΩ range is a good choice. RENT is required for this synchronization circuit, but RENB can be left unmounted if system UVLO is not needed. LMR23630-Q1 switching action can be synchronized to an external clock from 200 kHz to 2.2 MHz. Figure 18 and Figure 19 show the device synchronized to an external system clock.

Figure 17. Synchronize to External Clock

Figure 17. Synchronize to External Clock

Figure 18. Synchronizing in PWM Mode

Figure 18. Synchronizing in PWM Mode

Figure 19. Synchronizing in PFM Mode

Figure 19. Synchronizing in PFM Mode