ZHCUAE3A February 2019 – April 2021

6 EVM 设置和操作

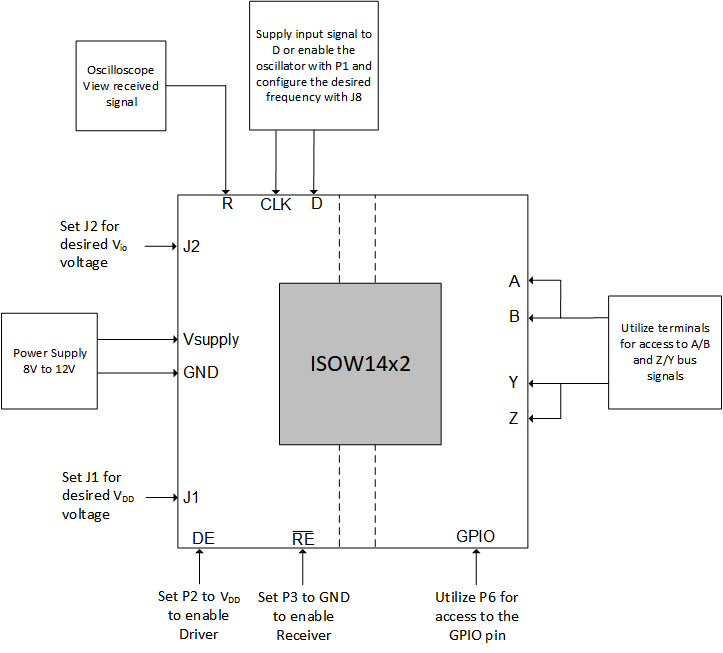

图 6-1 显示了具有评估器件性能所需的使用单个电源的 EVM 的基本设置。

使用器件数据表中给定范围内的电压。EVM 上的 LDO 将提供通过其跳线配置的 VDD。理想情况下,EVM 的电源电压应介于 8V 和 12V 之间。ISOW1412 将产生隔离式电源提供给 VISOOUT,该 VISOOUT 连接到 EVM 上的 VISOOIN。

该 EVM 具有板载振荡器器件,可用于向 ISOW1412 的 D 引脚提供时钟信号。振荡器通过跳线 P1 桥接到 D 输入,并可通过更改 J8 的配置将其配置为输出 12Mbps 或 500kbps。如需对 EVM 进行任何发射测试,建议使用板载振荡器。

EVM 上有两个 LDO,分别提供 VDD 和 VIO 电压。用户可以通过重新配置 J1 和 J2 上的跳线来更改 LDO 输出电压。J1 控制提供 VDD 的 LDO 的输出电压,可以是 3.3V 或 5V。J2 控制提供 VIO 的 LDO 的输出电压,可以是 1.8V、3.3V 或 5V。

J4 和 J3 分别是用于接入 A/B 和 Z/Y 总线线路的端子。这些引脚可用于连接其他 RS-485 器件。

A. 正常收发器运行需要激活驱动器和接收器部分。将接收器使能引脚 (RE) 设置为逻辑低电平,将驱动器使能引脚 (DE) 设置为逻辑高电平,以启用驱动器和接收器。

图 6-1 基本 EVM 设置表 6-1 显示了有关基本测试的跳线配置信息。

表 6-1 跳线配置

| 连接 | 标签 | 说明 |

|---|---|---|

| J1 | 3.3V 和 5V | 连接此跳线选择所需的 VDD 电压,可以是 3.3V 或 5V。 |

| J2 | 1.8V、3.3V、5V | 连接此跳线选择所需的 VIO 电压,可以是 1.8V、3.3V 或 5V。 |

J8 | J8 | 连接此跳线选择所需的振荡器开关频率。 |

P1 | VDD IO、VDD OSC | 连接此跳线加电并启用振荡器。 |

| P2 | VDD IO、DE、GND1 | 在中间引脚和 GND1 之间连接此跳线,将 DE 引脚连接到低电平。当 DE 引脚为低电平时,驱动器输入被禁用。在中间引脚和 VDD IO 之间连接此跳线,将 DE 引脚连接到高电平。当 DE 引脚为高电平时,驱动器输入被启用。将 DE 引脚连接到 VDD IO 进行全面运行测试。 |

P3 | VDD IO、RE、GND1 | 在中间引脚和 GND1 之间连接此跳线,将 RE 引脚连接到低电平。当 RE 引脚为低电平时,接收器被启用。将 RE 引脚连接到 GND1 进行全面运行测试。在中间引脚和 VDD IO 之间连接此跳线,将 RE 引脚连接到高电平。当 RE 引脚为高电平时,接收器被禁用。 |

P7 | VDD IO、EN、GND1 | 在中间引脚和 GND1 之间连接此跳线,禁用直流/直流转换器。使跳线保持断开或连接到 VDD IO,启用直流/直流转换器。 |