ZHCAEJ7A August 2024 – October 2024 DS90LVRA2 , DS90LVRA2-Q1 , SN65LVDS4

背景

低电压差分信号 (LVDS) 接口通常集成到数据处理平台(例如现场可编程门阵列 (FPGA))内部。这些平台采用尺寸较小的 CMOS 工艺进行开发,降低了内核电源和输入/输出 (I/O) 通道的电压要求。这些 I/O 要求由 LV(低电压)前缀指定的较低电压标准定义。例如,单端 5V CMOS 信号现在具有较低电压 (LVCMOS) 类型,例如 3.3V、2.5V、1.8V 和 1.2V。尺寸更小的工艺受到限制,无法支持整个 LVDS 标准,因此需要外部 LVDS 接收器解决方案。本应用简报重点介绍了 DS90LVRA2-Q1,这是一种支持低至 1.8V I/O 电压的外部 LVDS 接收器解决方案。

点对点 LVDS 拓扑

LVDS 是一种差分物理 (PHY) 层协议,仅使用毫瓦功耗即可提供千兆位的数据吞吐量。点对点 LVDS 应用包含 LVDS 驱动器,该驱动器在通过 100Ω 电阻器端接的总线介质上提供恒定的 3.5mA 驱动电流。LVDS 接收器根据总线终端上 ±350mV 的正或负电压摆幅确定高或低数据位。LVDS 驱动器可将 LVCMOS 或 LVTTL 单端输入转换为 LVDS 输出。LVDS 接收器将 LVDS 输入转换为单端 LVCMOS 或 LVTTL 输出。

图 1 点对点 LVDS 拓扑

图 1 点对点 LVDS 拓扑更低的 I/O 电压要求

较小工艺技术的开发已将数据采集平台的内核电源电压降至 2.5V、1.8V 和 1.2V。这些平台通常只发送和接收与电源电压匹配的信号。TI LVDS 产品系列中的大多数器件的运行电压为 3.3V,并且仅接受和输出 3.3V 单端信号。这意味着在没有电平转换器的情况下,这些器件的 I/O 通道不支持这些平台所需的较低电压信号传输要求。TI 应用简报如何使用 3.3V LVDS 驱动器/接收器 + 电平转换器支持 1.8V 信号 详细说明了如何实现这一点。本应用手册还提供了设计实现的实用技巧和注意事项。为了为任何应用选择合适的电平转换器,TI 逻辑指南 是另一个有用资源。

图 2 用以支持低压信号的 LVDS

接收器和电平转换器

图 2 用以支持低压信号的 LVDS

接收器和电平转换器例如,DS90LV028A 双通道 3.3V 接收器最多支持两个 LVDS 输入和两个单端 3.3V LVCMOS 输出。输出必须进行电平转换,以满足低功耗处理平台的较低 I/O 电压要求。一种选择是实施双通道电平转换器,例如 SN74AVC2T45-Q1。电平转换器会限制接收器的性能,例如信号传输速率等指标,因此在选择器件时必须考虑这一点。

借助 TI LVDS 接收器,无需再进行电平转换

电平转换器增加了设计复杂性并可能限制接收器性能。使用两个器件(驱动器或接收器以及电平转换器)和相关的分立式元件会在设计中占用更多的 PCB 面积,并且需要使用 3.3V 电源。

对于集成度更高的解决方案,德州仪器 (TI) 提供了 DS90LVRA2-Q1。该器件是一款以高达 600Mbps 的信号传输速率运行的双通道汽车级 LVDS 接收器。DS90LVRA2-Q1 提供了在 3.3V、2.5V 和 1.8V 电压下运行的灵活性,可将 LVCMOS 输出信号驱动至这些电压电平,因此无需使用单独的电平转换器器件来满足较低的电压输入信号规格。

图 3 DS90LVRA2-Q1 双通道 LVDS

接收器用于支持低压输出信号

图 3 DS90LVRA2-Q1 双通道 LVDS

接收器用于支持低压输出信号DS90LVRA2 是 DS90LVRA2-Q1 的非汽车级版本。该器件仅作为 1.8V LVDS 接收器运行,具有 1.8V LVCMOS 输出。

图 4 DS90LVRA2 双通道 LVDS 接收器用于支持

1.8V 输出信号

图 4 DS90LVRA2 双通道 LVDS 接收器用于支持

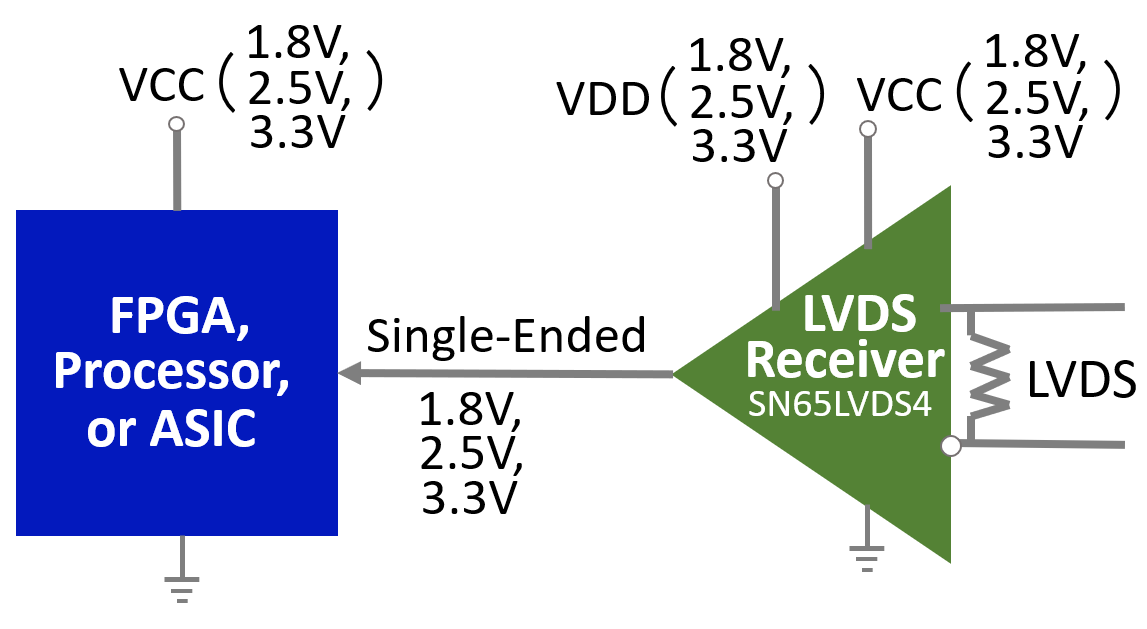

1.8V 输出信号SN65LVDS4 是一款非汽车级单通道 LVDS 接收器。它以高达 500Mbps 的信号传输速率运行。该器件可根据输出驱动电压引脚 (VDD) 驱动 3.3V LVTTL、2.5V LVCMOS 和 1.8V LVCMOS 输出,无需使用单独的电平转换器器件来满足较低电压输入信号规格。然而,SN65LVDS4 需要两个电压电源引脚(VCC 和 VDD),而 DS90LVRA2-Q1 和 DS90LVRA2 提供单个电压电源引脚的优势。

图 5 SN65LVDS4 单通道 LVDS

接收器用于支持低压输出信号

图 5 SN65LVDS4 单通道 LVDS

接收器用于支持低压输出信号TI LVDS 驱动器的较低电压解决方案

TI LVDS 产品系列目前不提供较低电压 LVDS 驱动器。建议将汽车级 DS90LV027AQ-Q1 双通道 3.3V LVDS 驱动器与 DS90LVRA2-Q1 配合使用。对于需要较低电压输入信号的应用,请参阅 TI 应用简报如何将 3.3V LVDS 缓冲器用作低压 LVDS 驱动器。在实现简单的偏置网络时,LVDS 驱动器不需要电平转换器。

外部 LVDS 接口的系统优势

1:优化 FPGA 性能

FPGA 通常具有内部集成的可编程 LVDS 接口。使用外部 LVDS 接收器进行设计可减轻接口的负担,这意味着不会牺牲 FPGA 的功耗和性能。TI 应用简报为低功耗 FPGA、处理器和 ASIC 设施启用 LVDS 链路 中重点介绍了这一点。

图 6 通过卸载 LVDS 接口优化 FPGA 性能

图 6 通过卸载 LVDS 接口优化 FPGA 性能2:设计灵活性和更低成本的 FPGA

尺寸更小的 CMOS 工艺是提供内部集成 LVDS 接收器可行性的限制因素,无法支持 LVDS 标准的整个共模电压 (VCM) 范围。该标准允许 ±1V 共模接地漂移,这意味着 VCM 高达 2.2V。此外,有可能发生较大接地漂移的系统设计还可从外部 LVDS 接口中进一步获益,该接口可提供高达 5V 的扩展共模范围电压。具有集成 LVDS 接口的 FPGA 通常更加昂贵。在某些设计中,外部 LVDS 接口可提供系统设计灵活性并降低复杂性和成本。

3:更低的功率预算

使用低功耗数据采集平台有助于优化功耗,从而允许使用更便宜、更可靠且更小的系统,并通过减少对风扇或散热器的需求来降低热设计复杂性。应用特定集成电路 (ASIC) 是具有固定逻辑源的不可编程逻辑器件,从而支持可预测的功耗,而现代 FPGA 需要三个独立的电源,并且总体功耗取决于设计。

TI 应用手册借助 TI Designs 加快 FPGA 电源设计 重点介绍了如何将电源管理集成电路 (PMIC) 用作集成电源解决方案。此链接提供了使用德州仪器 (TI) 处理器的电源解决方案的全面概述。该网站还包含与其他热门处理器和 FPGA(例如 Altera 和 Xilinx)兼容的电源解决方案。

结语

尺寸更小的 CMOS 工艺降低了内核和 I/O 电压要求,并限制了数据采集平台中内部集成 LVDS 接收解决方案的可行性。DS90LVRA2-Q1 双通道 LVDS 接收器是一种具有集成功能的外部解决方案,无需为需要低至 1.8V 输入的平台单独使用电平转换器件。此解决方案提高了设计灵活性,同时减少了元件数量,并支持许多几何尺寸更小的 CMOS 工艺的更低电压信号要求。DS90LVRA2 双通道 1.8V 接收器和 SN65LVDS4 单通道接收器具有类似的优势。

参考资料

- 德州仪器 (TI),如何使用 3.3V LVDS 驱动器/接收器和电平转换器支持 1.8V 信号 应用简报

- 德州仪器 (TI),如何将 3.3V LVDS 缓冲器用作低压 LVDS 驱动器 应用简报

- 德州仪器 (TI),为低功耗 FPGA、处理器和 ASIC 实施启用 LVDS 链路 应用简报

- 德州仪器 (TI),借助 TI Designs 加快 FPGA 电源设计 技术文章