ZHCAD19 august 2023 DS320PR1601 , DS320PR410 , DS320PR810 , SN75LVPE5412 , SN75LVPE5421

2.4.1 参数校准的详细说明

- 振幅或 VOD 校准:振幅校准是在 TP3 处使用混合时钟和低频模式以 32Gbps 来完成的。在这种情况下,必须使用 P1 至 P9 预设来确认 PCIe Gen5 合规性。

- RJ 校准在 TP3 处执行。P4 处使用 PCIe 校准模式以及 SigTest Phoenix 5.1.04 RJ_SJ_CAL 模板来分析 RJ。TP3 处的目标 RJ 为 0.5ps rms。

- SJ 校准与 RJ 相似,目标值为 1ps 至 5ps。

- 插入损耗校准在 TP2 处执行。图 2-7 和图 2-8 展示了信号路径内不同元件的损耗目标以及 CBB/CLB 和 ISI 损耗电路板设置。

- AIC DMI(差模干扰)在 TP2 处执行,TP2 处的总通道损耗为 31.8dB。Phoenix 使用 4.2dB 来表示 AIC 封装损耗。P4 预设和用 2.1GHz 信号调制的 DMI/CMI 模式用于在 TP2 处实现目标 5mV 至 30mV DMI。

- CMI 与 DMI 相同,也在 TP2 处执行。使用 120MHz CMI 来实现 150mV 的目标值。

- TX EQ 校准:BERT 根据噪声值进行校准。使用 P5/6/8/9 预设,以可在 TP2 处产生最佳眼图面积为依据,来选择最佳 CTLE 和预设。

- 插入损耗从 36dB 开始以 0.5dB 为步长递减,DMI 以 3mV 为增量递增,SJ 以 10mUI 为增量递增,SJ 以 10mV 为增量递增,而器件 CTLE 增益范围为 7 到 12,以实现最佳眼高 (EH) 和眼宽 (EW)。

表 2-3 中的 DS320PR1601 性能矩阵展示了使用刚刚讨论的 RX 均衡方法时各种前置通道和后置通道组合的器件性能。

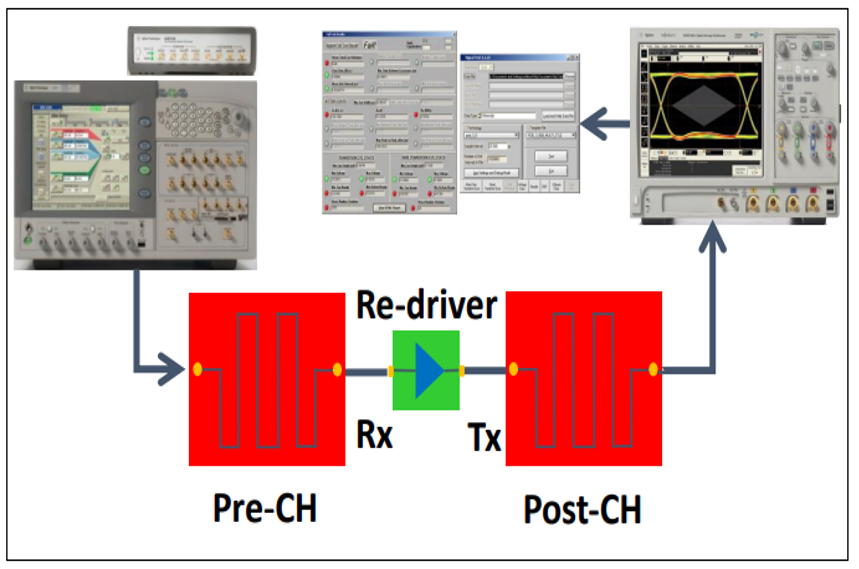

图 2-11 AIC 测试概述

图 2-11 AIC 测试概述表 2-3 展示了完成校准并在 AIC 模式下运行后,使用 PCIe Gen5 RX 均衡方法时各种前置通道和后置通道组合的器件性能

表 2-3 前置通道和后置通道损耗的器件性能

| 前置通道损耗 (dB) | 后置通道损耗 (dB) | EQ 指数/直流增益/预设 | 眼宽 (UI) | 眼高 (mV) |

|---|---|---|---|---|

| 10 | 32 | 2/L2/P6 | 0.39 | 35.74 |

| 14 | 26 | 2/L2/P6 | 0.41 | 46 |

| 14 | 32 | 7/L2/P6 | 0.35 | 36.83 |

| 18 | 22 | 2/L4/P6 | 0.4 | 72.5 |

| 18 | 26 | 3/L2/P6 | 0.4 | 48.21 |

| 22 | 18 | 1/L2/P6 | 0.44 | 67.7 |

| 22 | 22 | 3/L2/P6 | 0.39 | 40.91 |

| 22 | 26 | 7/L2/P6 | 0.43 | 48 |

| 26 | 18 | 3/L2/P5 | 0.37 | 33.1 |

| 26 | 22 | 4/L2/P6 | 0.4 | 39.7 |

| 26 | 26 | 4/L2/P6 | 0.36 | 28.4 |

| 29 | 18 | 4/L2/P6 | 0.35 | 39.7 |

| 29 | 22 | 4/L2/P6 | 0.34 | 29.59 |