TIDT357 November 2023

1.1 Power-On Sequence

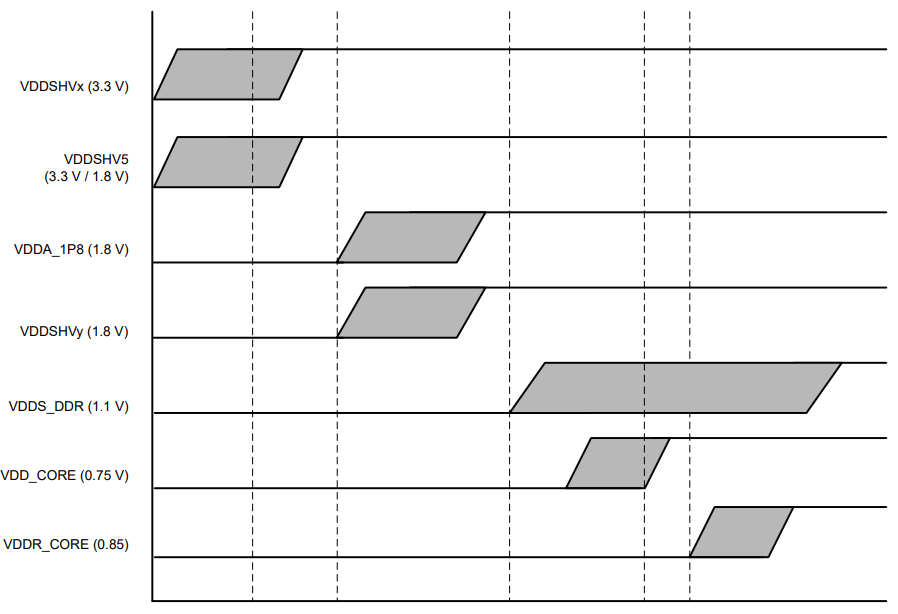

The AM62x-Q1 requires the different power rails to be ramped up in a certain sequence to provide reliable and fault-free operation. Figure 1-2 shows the power-on sequence of the power rails. Shaded regions in Figure 1-2 indicate that a particular rail is allowed to ramp up at any time within this region. The 3V3, VDDSHVx and VDDSHV5 rails are the first rails to be powered on. Next, the 1.8-V analog and digital rails are ramped up. This is followed by the 1.1-V DDR rail. By ramping up the 0.75 V, VDD_CORE before the 0.85 V, VDDR_CORE, sequence makes sure that the VDDR_CORE voltage never exceeds the VDD_CORE voltage by 180 mV. If VDD_CORE is operating at 0.85 V, both VDD_CORE and VDDR_CORE can be supplied by the same rail and there is no ramp up requirement between them. The 1.8 V, VPP is the eFuse programming supply, which is left floating (HiZ) or grounded during power-up or power-down sequences and during normal device operation. This supply is only sourced while programming.

For a detailed description of the power-on sequencing, see the power-up sequencing section of the AM62Ax Sitara™ Processors data sheet.

Figure 1-2 AM62x-Q1 Power-On

Sequence

Figure 1-2 AM62x-Q1 Power-On

Sequence