SLVAEQ2 April 2020 TPS2549-Q1 , TPS254900-Q1 , TPS254900A-Q1 , TPS2556-Q1 , TPS2557-Q1 , TPS2559-Q1 , TPS25830-Q1 , TPS25831-Q1 , TPS25832-Q1 , TPS25833-Q1 , TPS25840-Q1 , TPS25842-Q1

-

How to Pass MFi Overcurrent Protection Test With USB Charger and Switch Device

- Trademarks

- 1 The Instruction of MFi OCP Requirement

- 2 Test Standard and Requirements

- 3

The Solution to Pass MFi OCP Test

- 3.1 Solution 1: Increasing Current Limit Point Higher Than 1.6*Ia

- 3.2

Solution 2: Paralleling RC With Rlimit to Delay the Current Limit Response

- 3.2.1 For the 1.5A USB Port With External FET

- 3.2.2 For the 1.5A Port Without External FET

- 3.2.3 For 2.1A USB Port With External FET

- 3.2.4 For 2.1A USB Port Without External FET

- 3.2.5 For 2.4A USB Port With External FET

- 3.2.6 For 2.4A USB Port Without External FET

- 3.2.7 For 3A USB Port With External FET

- 3.2.8 For 3A USB Port Without FET

- 4 Summary

- 5 References

3.2 Solution 2: Paralleling RC With Rlimit to Delay the Current Limit Response

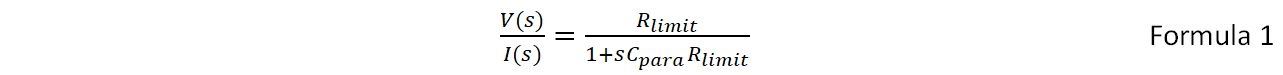

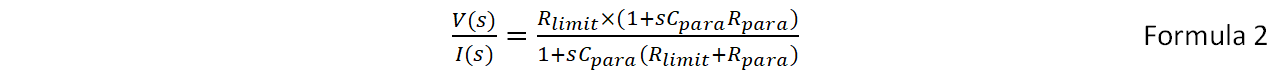

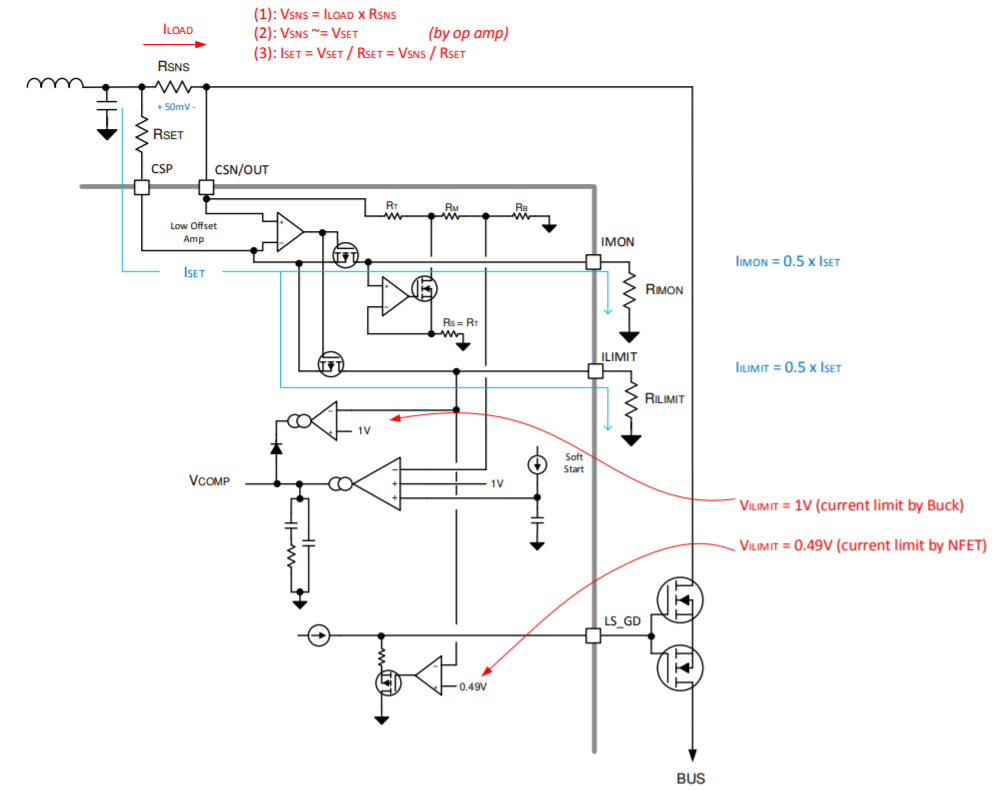

This solution just can apply to TPS2583x/4x-Q1. TPS2583x/4x-Q1 is based on the voltage of Rlimit to determine whether or not it is overcurrent, as shown in Figure 8. So if you can delay the voltage rise, you can delay the current limit response. Think of parallel capacitors with Rlimit to achieve the delay. However, the internal circuit of the ILIMIT pin is a current source circuit. If you just parallel a capacitor with Rlimit as shown in Figure 9, it will introduce a pole into the current limit circuit as shown in Equation 1. The attenuation of gain and phase by pole will affect the loop stability. In order to eliminate the effect of the pole, you can add a resistor in the series with the capacitor to add a zero, as shown in Figure 10. This resistor introduces an additional zero point to reduce the influence of the pole, as shown in Equation 2. In order to ensure that the positions of zero and pole are close, setting Rpara = Rlimit is recommended. From the test result to ensure delay 1 ms, 82 nF is a suitable value for Cpara. In this section, the response under certification load is tested when using external FET or no external FET.

Figure 9. Current Limit Function Diagrams

Figure 9. Current Limit Function Diagrams .png) Figure 10. Parallel RC Circuit

Figure 10. Parallel RC Circuit