SLOA140B April 2009 – November 2018 TRF7960 , TRF7960A , TRF7961 , TRF7962A , TRF7963A

1.6 Extra Dummy Bytes on RX

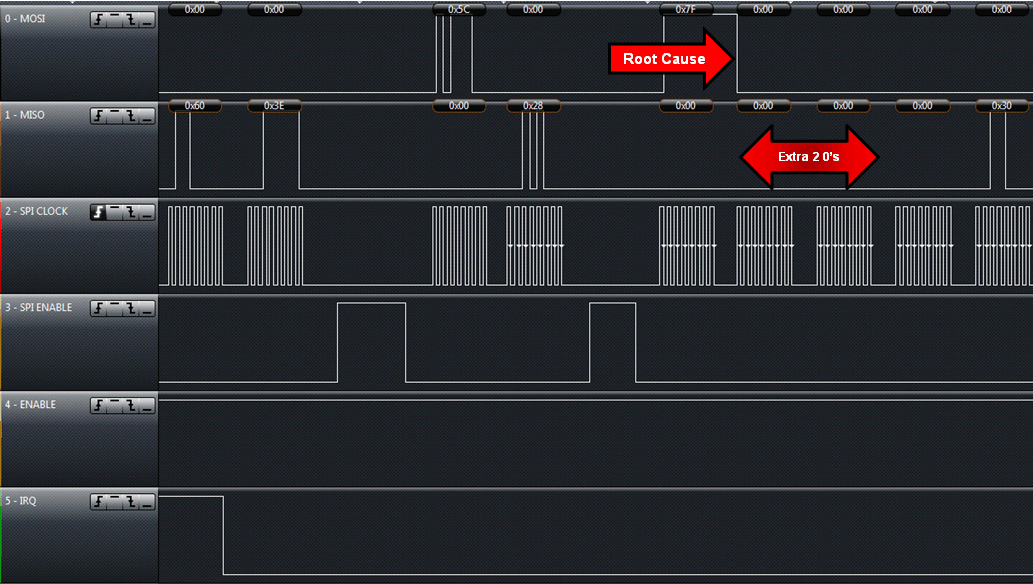

A specific condition can cause the TRF7960 to output two additional dummy bytes of data when reading the FIFO after an RX operation. This occurs when the MOSI line is left high after issuing the direct command to continuous read from the TRF7960 FIFO. The MOSI line can left high due to not properly resetting the SPI module while changing the SCLK polarity for the read operation. Figure 5 shows the root cause of this output.

Figure 5. Screenshot With Root Cause

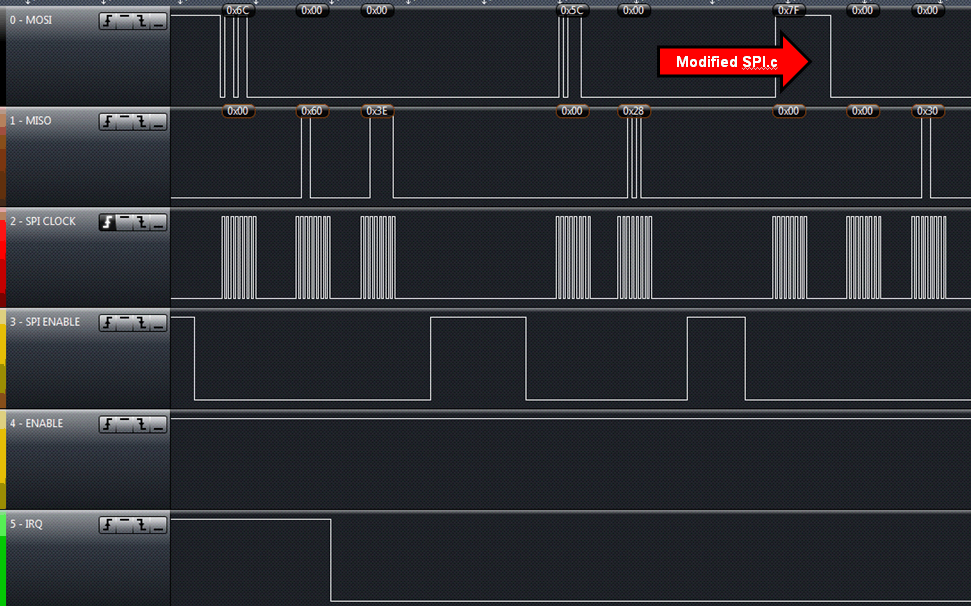

Figure 5. Screenshot With Root Cause To fix this, ensure the SPI module is properly reset in the MCU when toggling the SCLK polarity between read and write operations. This should force the MOSI line back low and resolve the issue. Figure 6 shows the updated firmware, and Figure 7 shows the signals after correction.

Figure 6. Screenshot of Adjusted Firmware

Figure 6. Screenshot of Adjusted Firmware  Figure 7. Screenshot With Issue Fixed

Figure 7. Screenshot With Issue Fixed