SLAZ268AB October 2012 – May 2021 MSP430F5324

- 1Functional Advisories

- 2Preprogrammed Software Advisories

- 3Debug Only Advisories

- 4Fixed by Compiler Advisories

- 5Nomenclature, Package Symbolization, and Revision Identification

-

6Advisory Descriptions

- 6.1 ADC25

- 6.2 ADC27

- 6.3 ADC29

- 6.4 ADC42

- 6.5 ADC69

- 6.6 BSL6

- 6.7 BSL7

- 6.8 COMP10

- 6.9 CPU21

- 6.10 CPU22

- 6.11 CPU23

- 6.12 CPU26

- 6.13 CPU27

- 6.14 CPU28

- 6.15 CPU29

- 6.16 CPU30

- 6.17 CPU31

- 6.18 CPU32

- 6.19 CPU33

- 6.20 CPU34

- 6.21 CPU35

- 6.22 CPU37

- 6.23 CPU39

- 6.24 CPU40

- 6.25 CPU47

- 6.26 DMA4

- 6.27 DMA7

- 6.28 DMA8

- 6.29 DMA10

- 6.30 EEM9

- 6.31 EEM11

- 6.32 EEM13

- 6.33 EEM14

- 6.34 EEM15

- 6.35 EEM16

- 6.36 EEM17

- 6.37 EEM19

- 6.38 EEM21

- 6.39 EEM23

- 6.40 FLASH33

- 6.41 FLASH34

- 6.42 FLASH35

- 6.43 FLASH37

- 6.44 JTAG20

- 6.45 JTAG26

- 6.46 JTAG27

- 6.47 LDO1

- 6.48 MPY1

- 6.49 PMAP1

- 6.50 PMM9

- 6.51 PMM10

- 6.52 PMM11

- 6.53 PMM12

- 6.54 PMM14

- 6.55 PMM15

- 6.56 PMM17

- 6.57 PMM18

- 6.58 PMM20

- 6.59 PORT15

- 6.60 PORT16

- 6.61 PORT19

- 6.62 PORT24

- 6.63 RTC3

- 6.64 RTC6

- 6.65 SYS10

- 6.66 SYS12

- 6.67 SYS14

- 6.68 SYS16

- 6.69 TAB23

- 6.70 USCI26

- 6.71 USCI30

- 6.72 USCI31

- 6.73 USCI34

- 6.74 USCI35

- 6.75 USCI39

- 6.76 USCI40

- 6.77 WDG4

- 7Revision History

6.65 SYS10

SYS Module

Category

Functional

Function

BSL entry sequence is subject to specific timing requirements

Description

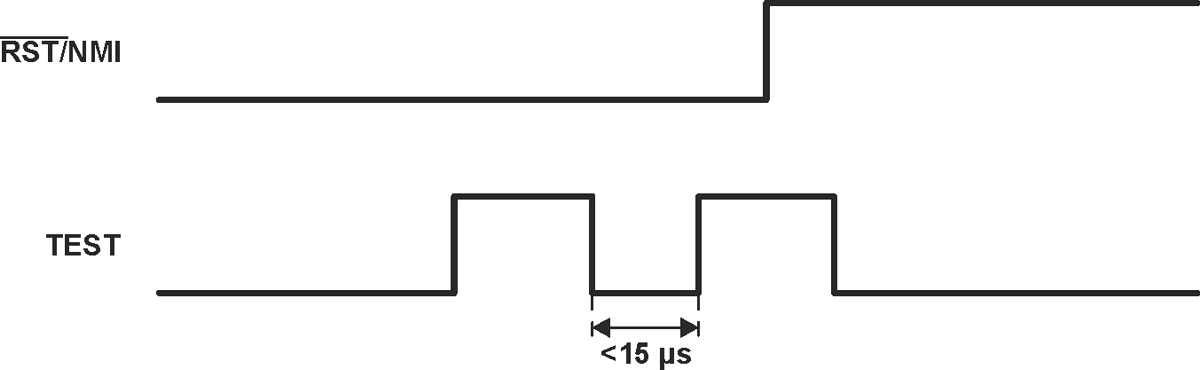

The BSL entry sequence requires that the low phase of the TEST/SBWTCK pin does not exceed 15us. This timing requirement is faster than most PC serial ports can provide, as shown in the following picture. If this requirement is not met, the entry sequence fails and the SYSBSLIND is not set.

Workaround

An external hardware solution is recommended to provide the appropriate BSL entry sequence. See http://processors.wiki.ti.com/index.php/BSL_(MSP430) for recommendations on available BSL hardware.