SLAZ184P October 2012 – May 2021 MSP430F249 , MSP430F249-EP

- 1Functional Advisories

- 2Preprogrammed Software Advisories

- 3Debug Only Advisories

- 4Fixed by Compiler Advisories

- 5Nomenclature, Package Symbolization, and Revision Identification

-

6Advisory Descriptions

- 6.1 ADC25

- 6.2 BCL12

- 6.3 BCL13

- 6.4 BCL15

- 6.5 COMP2

- 6.6 CPU19

- 6.7 FLASH19

- 6.8 FLASH24

- 6.9 FLASH25

- 6.10 FLASH27

- 6.11 FLASH36

- 6.12 JTAG23

- 6.13 PORT11

- 6.14 PORT12

- 6.15 TA12

- 6.16 TA16

- 6.17 TA21

- 6.18 TAB22

- 6.19 TB2

- 6.20 TB16

- 6.21 TB24

- 6.22 USCI20

- 6.23 USCI21

- 6.24 USCI22

- 6.25 USCI23

- 6.26 USCI24

- 6.27 USCI25

- 6.28 USCI26

- 6.29 USCI28

- 6.30 USCI30

- 6.31 USCI34

- 6.32 USCI35

- 6.33 USCI40

- 6.34 XOSC5

- 6.35 XOSC6

- 6.36 XOSC8

- 7Revision History

6.23 USCI21

USCI Module

Category

Functional

Function

UART IrDA receive filter

Description

The IrDA receive filter can be used to filter pulses with length UCAIRRXFL configured in UCAxIRRCTL register. If UCIRRXFE is set the IrDA receive decoder may filter out pulses longer than the configured filter length depending on frequency of BRCLK. This is resulting in framing errors or corrupted data on the receiver side.

Workaround

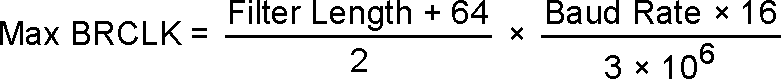

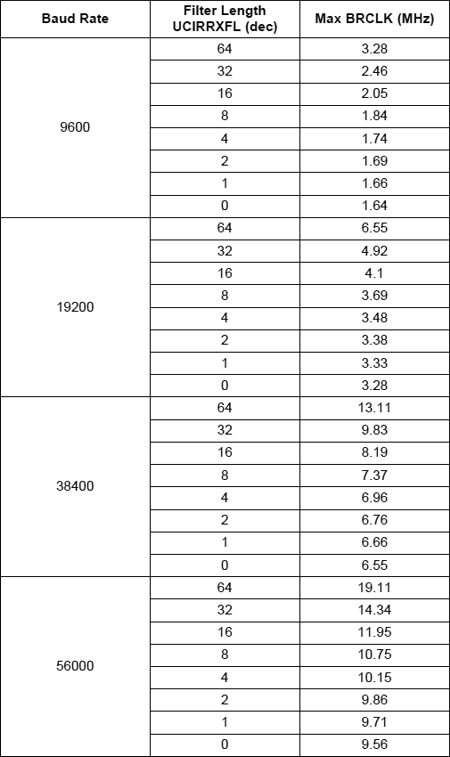

Depending on the used baud rate and the configured filter length a maximum frequency for BRCLK needs to be set to avoid this issue:

For baud rates equal and higher than 115.000 the maximum allowed BRCLK frequency is equal to the max specified system frequency.