SLAZ182P October 2012 – May 2021 MSP430F248

- 1Functional Advisories

- 2Preprogrammed Software Advisories

- 3Debug Only Advisories

- 4Fixed by Compiler Advisories

- 5Nomenclature, Package Symbolization, and Revision Identification

-

6Advisory Descriptions

- 6.1 ADC25

- 6.2 BCL12

- 6.3 BCL13

- 6.4 BCL15

- 6.5 COMP2

- 6.6 CPU19

- 6.7 FLASH19

- 6.8 FLASH24

- 6.9 FLASH25

- 6.10 FLASH27

- 6.11 FLASH36

- 6.12 JTAG23

- 6.13 PORT11

- 6.14 PORT12

- 6.15 TA12

- 6.16 TA16

- 6.17 TA21

- 6.18 TAB22

- 6.19 TB2

- 6.20 TB16

- 6.21 TB24

- 6.22 USCI20

- 6.23 USCI21

- 6.24 USCI22

- 6.25 USCI23

- 6.26 USCI24

- 6.27 USCI25

- 6.28 USCI26

- 6.29 USCI28

- 6.30 USCI30

- 6.31 USCI34

- 6.32 USCI35

- 6.33 USCI40

- 6.34 XOSC5

- 6.35 XOSC6

- 6.36 XOSC8

- 7Revision History

6.21 TB24

TB Module

Category

Functional

Function

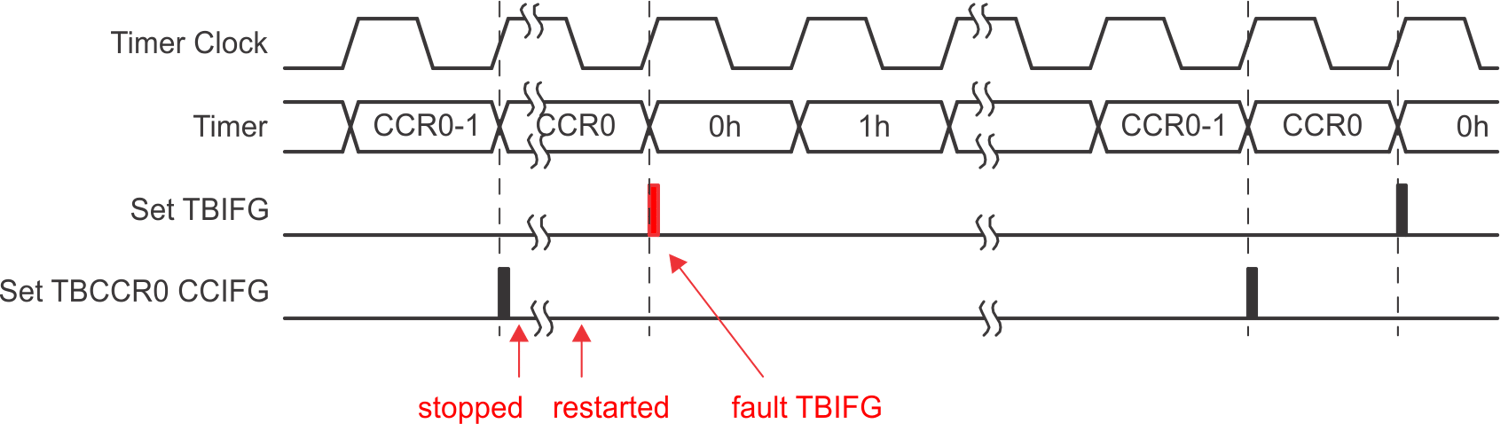

TBIFG Flag is erroneously set after Timer B restarts in Up Mode

Description

In Up Mode, the TBIFG flag should only be set when the timer resets from TBCCR0 to zero. However, if the Timer B is stopped at TBR = TBCCR0, then cleared (TBR=0) by setting the TBCLR bit, and finally restarted in Up Mode, the next rising edge of the TBCLK will erroneously set the TBIFG flag.

Workaround

None.