ZHCSCV8A September 2014 – October 2014 TUSB1210-Q1

PRODUCTION DATA.

- 1 特性

- 2 应用范围

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 Handling Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Analog I/O Electrical Characteristics

- 6.6 Digital I/O Electrical Characteristics

- 6.7 Digital IO Pins (Non-ULPI)

- 6.8 PHY Electrical Characteristics

- 6.9 Pullup/Pulldown Resistors

- 6.10 OTG Electrical Characteristics

- 6.11 Power Characteristics

- 6.12 Switching Characteristics

- 6.13 Timing Requirements

- 6.14 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5

Register Map

- 7.5.1 VENDOR_ID_LO

- 7.5.2 VENDOR_ID_HI

- 7.5.3 PRODUCT_ID_LO

- 7.5.4 PRODUCT_ID_HI

- 7.5.5 FUNC_CTRL

- 7.5.6 FUNC_CTRL_SET

- 7.5.7 FUNC_CTRL_CLR

- 7.5.8 IFC_CTRL

- 7.5.9 IFC_CTRL_SET

- 7.5.10 IFC_CTRL_CLR

- 7.5.11 OTG_CTRL

- 7.5.12 OTG_CTRL_SET

- 7.5.13 OTG_CTRL_CLR

- 7.5.14 USB_INT_EN_RISE

- 7.5.15 USB_INT_EN_RISE_SET

- 7.5.16 USB_INT_EN_RISE_CLR

- 7.5.17 USB_INT_EN_FALL

- 7.5.18 USB_INT_EN_FALL_SET

- 7.5.19 USB_INT_EN_FALL_CLR

- 7.5.20 USB_INT_STS

- 7.5.21 USB_INT_LATCH

- 7.5.22 DEBUG

- 7.5.23 SCRATCH_REG

- 7.5.24 SCRATCH_REG_SET

- 7.5.25 SCRATCH_REG_CLR

- 7.5.26 VENDOR_SPECIFIC1

- 7.5.27 VENDOR_SPECIFIC1_SET

- 7.5.28 VENDOR_SPECIFIC1_CLR

- 7.5.29 VENDOR_SPECIFIC2

- 7.5.30 VENDOR_SPECIFIC2_SET

- 7.5.31 VENDOR_SPECIFIC2_CLR

- 7.5.32 VENDOR_SPECIFIC1_STS

- 7.5.33 VENDOR_SPECIFIC1_LATCH

- 7.5.34 VENDOR_SPECIFIC3

- 7.5.35 VENDOR_SPECIFIC3_SET

- 7.5.36 VENDOR_SPECIFIC3_CLR

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械封装和可订购信息

1 特性

- 具有符合 AEC-Q100 标准的以下结果:

- 温度等级 3:-40°C 至 85°C

- 人体模型 (HBM) 静电放电 (ESD) 分类等级 1C

- 充电器件模型 (CDM) ESD 分类等级 C4B

- USB2.0 物理层 (PHY) 收发器芯片,可通过 ULPI 12 引脚接口连接 USB 控制器,其完全符合:

- 通用串行总线规范 2.0 版

- USB 2.0 规范移动附录 1.3 版

- UTMI+ 低引脚接口 (ULPI) 规范 1.1 版

- DP/DM 线路外部组件补偿(专利号 US7965100 B1)

- 连接主机、外设和 OTG 器件内核的接口;针对便携式器件或具有内置 USB OTG 器件内核的系统 ASIC 进行了优化

- 完整的 USB OTG 物理前端支持主机协商协议 (HNP) 与会话请求协议 (SRP)

- ULPI 接口:

- I/O 接口 (1.8V) 针对无端接 50 Ω 线路阻抗进行了优化

- ULPI 时钟引脚 (60 MHz) 可同时支持输入和输出时钟配置

- 符合 ULPI 标准的完全可编程寄存器集

- 采用 32 引脚四方扁平无引线

[QFN (RHB)] 封装

2 应用范围

- 移动电话

- 平板电脑设备

- 台式机

- 便携式计算机

- 视频游戏控制台

- 便携式音乐播放器

3 说明

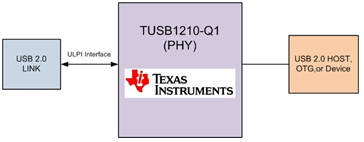

TUSB1210-Q1 是一款 USB2.0 收发器芯片,可通过 ULPI 接口连接 USB 控制器。 支持所有 USB2.0 数据速率(高速 480Mbps、全速 12Mbps 以及低速 1.5Mbps),且兼容主机和外设模式。 此外,该器件还支持 UART 模式及原有 ULPI 串行模式。

TUSB1210-Q1 还支持 USB2.0 规范相关的 OTG(1.3 版)可选附件,包括主机协商协议 (HNP) 和会话请求协议 (SRP)。

发送器中的 DP/DM 外部组件补偿可对串联阻抗中的变化进行补偿,以匹配数据线路阻抗和接收器输入端阻抗,限制数据反射,从而改善眼图。

器件信息(1)

| 部件号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| TUSB1210-Q1 | 超薄四方扁平无引线 (VQFN) (32) | 5.00mm x 5.00mm |

- 要了解所有可用封装,请见数据表末尾的可订购产品附录。

4 修订历史记录

Changes from * Revision (September 2014) to A Revision

- 已更改特性列表Go

- 删除了说明部分“TUSB1210-Q1 还支持 OTG(1.3 版)..”之后的 5 个段落Go

- 已更改图图Go

- Added VIL and VIH to the Recommended Operating Conditions table Go

- Changed the Thermal Information table Go

- Changed the Digital I/O Electrical Characteristics table Go

- Digital IO Electrical Characteristics sections to the Switching CharacteristicsGo

- Added the Typical Characteristics sectionGo

- Added 5 new paragraphs to the Overview sectionGo