ZHCSO92A october 2022 – june 2023 TPS3436-Q1

PRODUCTION DATA

9.2.1.2.3 计算 WDO 上拉电阻

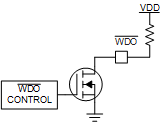

TPS3436-Q1 使用开漏配置来实现 WDO 电路,如图 9-2 所示。当 FET 关断时,电阻器会将晶体管的漏极拉至 VDD,当 FET 导通时,FET 会尝试将漏极拉至接地端,从而形成有效的电阻分压器。选择该分压器中的电阻器时必须能够确保 VOL 低于其最大值。为了选择合适的上拉电阻器,需要牢记三个关键规格:上拉电压 (VPU)、建议的最大 WDO 引脚电流 (IRST) 和 VOL。最大 VOL 为 0.3V,这意味着形成的有效电阻分压器必须能够使复位引脚上的电压低于 0.3V,并使 IRST 在 VDD ≥ 3V 时保持在 2mA 以下,而在 VDD = 1.5V 时保持在 500μA 以下。对于此示例,当 VPU = VDD = 1.5V 时,选择的电阻器必须能够将 IRST 保持在 500μA 以下,因为这个值是允许的最大消耗电流。为确保满足这一规格,此处选择了一个 10kΩ 的上拉电阻值,当 WDO 置位时,该电阻器的最大灌电流为 180μA。

图 9-2 开漏 RESET 配置

图 9-2 开漏 RESET 配置