SLVSBP3C December 2012 – May 2015 TPD5S116

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Simplified Schematic

- 5 Revision History

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics

- 7.6 Voltage Level Shifter, SCL, SDA Lines

- 7.7 Voltage Level Shifter, CEC Line

- 7.8 Voltage Level Shifter, HPD Line

- 7.9 EN

- 7.10 Utility Pin

- 7.11 I/O Capacitances

- 7.12 Dynamic Load Characteristics

- 7.13 SCL, SDA Lines, VCCA = 1.2 V

- 7.14 CEC Line, VCCA = 1.2 V

- 7.15 HPD Line, VCCA = 1.2 V

- 7.16 SCL, SDA Lines, VCCA = 1.5 V

- 7.17 CEC Line, VCCA = 1.5 V

- 7.18 HPD Line, VCCA = 1.5 V

- 7.19 SCL, SDA Lines, VCCA = 1.8 V

- 7.20 CEC Line, VCCA = 1.8 V

- 7.21 HPD Line, VCCA = 1.8 V

- 7.22 SCL, SDA Lines, VCCA = 2.5 V

- 7.23 CEC Line, VCCA = 2.5 V

- 7.24 HPD Line, VCCA = 2.5 V

- 7.25 SCL, SDA Lines, VCCA = 3.3 V

- 7.26 CEC Line, VCCA = 3.3 V

- 7.27 HPD Line, VCCA = 3.3 V

- 7.28 SCL, SDA Lines, VCCA = 5 V

- 7.29 CEC Line, VCCA = 5 V

- 7.30 HPD Line, VCCA = 5 V

- 7.31 Typical Characteristics

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 IEC 61000-4-2 Level 4 ESD Protection

- 8.3.2 Conforms to HDMI Control and 5VOUT Compliance Tests Without External Components

- 8.3.3 Auto-direction Sensing I2C Level Shifter with One-Shot Circuit to Drive Long HDMI Cable (750-pF Load)

- 8.3.4 Back Drive Protection

- 8.3.5 55-mA Load Switch with Short Circuit Protection

- 8.3.6 Hot Plug Detect Module with Pull Down Resistor

- 8.3.7 Integrated Pull-up and Pull-down Resistors per HDMI Specification

- 8.3.8 Utility Pin ESD Protection for Ethernet and Audio Return

- 8.3.9 DDC/CEC LEVEL SHIFT Circuit Operation

- 8.3.10 DDC/CEC Level Shifter Operational Notes For VCCA = 1.8V

- 8.3.11 Rise-Time Accelerators

- 8.3.12 Noise Considerations

- 8.3.13 HDMI Compliance

- 8.4 Device Functional Modes

- 9 Applications and Implementations

- 10Power Supply Requirements

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

7 Specifications

7.1 Absolute Maximum Ratings(1)

over operating free-air temperature range (unless otherwise noted)| MIN | MAX | UNIT | ||||

|---|---|---|---|---|---|---|

| VCCA | Supply voltage range | –0.3 | 6 | V | ||

| 5V_SYS | Supply voltage range | –0.3 | 6 | V | ||

| VI | Input voltage range(2) | SCL_SYS, SDA_SYS, CEC_SYS, EN | –0.3 | 6 | V | |

| SCL_CON, SDA_CON, CEC_CON, HPD_CON | –0.3 | 6 | ||||

| VO | Voltage range applied to any output in the high-impedance or power-off state(2)(3) | SCL_SYS, SDA_SYS, CEC_SYS, HPD_SYS | –0.3 | 6 | V | |

| SCL_CON, SDA_CON, CEC_CON, HPD_CON | –0.3 | 6 | ||||

| VO | Voltage range applied to any output in the high or low state(2)(3) | SCL_SYS, SDA_SYS, CEC_SYS,HPD_SYS | –0.3 | VCCA + 0.5 | V | |

| SCL_CON, SDA_CON, CEC_CON | –0.3 | 5V_SYS + 0.5 | ||||

| IIK | Input clamp current | VI < 0 | –50 | mA | ||

| IOK | Output clamp current | VO < 0 | –50 | mA | ||

| Continuous current through 5V_SYS, or GND | ±100 | mA | ||||

| Tstg | Storage temperature range | –65 | 150 | °C | ||

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

(2) The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

(3) The package thermal impedance is calculated in accordance with JESD 51-7.

7.2 ESD Ratings

| VALUE | UNIT | ||||

|---|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | All pins | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | |||||

| IEC 61000-4-2 Contact Discharge | Pins SCL_CON, SDA_CON, CEC_CON, HPD_CON, 5V_CON, UTI_CON | ±15000 | |||

| IEC 61000-4-2 Air-gap ESD | |||||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as 2000 V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as 2000 V may actually have higher performance.

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| VCCA | Supply Voltage | 1.1 | 5.5 | V | ||||

| 5V_SYS | Supply Voltage | 4.5 | 5.5 | V | ||||

| VIH | High-level input voltage | SCL_SYS, SDA_SYS, | VCCA = 1.1 V to 5.5 V | 0.7 × VCCA | VCCA | V | ||

| CEC_SYS, | VCCA = 1.1 V to 5.5 V | 0.7 × VCCA | VCCA | V | ||||

| EN | VCCA = 1.1 V to 5.5 V | 1 | VCCA | V | ||||

| SCL_CON, SDA_CON, | 5V_ SYS = 5.5 V | 0.7 × 5V_SYS | 5V_SYS | V | ||||

| CEC_CON | 5V_ SYS = 5.5 V | 0.7 ×V3P3 | V3P3 | |||||

| HPD_CON | 5V_ SYS = 5.5 V | 2 | 5V_SYS | |||||

| VIL | Low-level input voltage | SCL_SYS, SDA_SYS, | VCCA = 1.1 V to 5.5 V | –0.5 | 0.082 × VCCA | V | ||

| CEC_SYS, | VCCA = 1.1 V to 5.5 V | –0.5 | 0.082 × VCCA | V | ||||

| EN | VCCA = 1.1 V to 5.5 V | –0.5 | 0.4 | V | ||||

| SCL_CON, SDA_CON, | 5V_ SYS = 5.5 V | –0.5 | 0.3 × 5V_SYS | V | ||||

| CEC_CON | 5V_ SYS = 5.5 V | –0.5 | 0.3 × V3P3 | V | ||||

| HPD_CON | 5V_ SYS = 5.5 V | 0 | 0.8 | V | ||||

| VILC | (contention) Low-level input voltage | SCL_SYS, SDA_SYS, CEC_SYS | VCCA = 1.1 V to 5.5 V | –0.5 | 0.0524 × VCCA | V | ||

| VOL – VILC | Delta between VOL and VILC | SCL_SYS, SDA_SYS, CEC_SYS | VCCA = 1.8 V | 0.1 × VCCA | mV | |||

| TA | Operating free-air temperature | –40 | 85 | °C | ||||

7.4 Thermal Information

| THERMAL METRIC(1) | TPDSS116 | UNIT | |

|---|---|---|---|

| YFF (DSBGA) | |||

| 12 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 79.6 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 0.6 | °C/W |

| RθJB | Junction-to-board thermal resistance | 13 | °C/W |

| ψJT | Junction-to-top characterization parameter | 2.4 | °C/W |

| ψJB | Junction-to-board characterization parameter | 13 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

7.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted) and VCCA = 1.1 V to 5.5 V and 5V_SYS = 5.5 V. Typical values measured at VCCA = 1.8 V and 5V_SYS = 5 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| Supply Current | ||||||||

| ICC5V | Disabled | 5V_SYS =5V, 5V_CON =Open EN = GND, HPD_CON = GND | 2 | 10 | µA | |||

| Load Switch active | 5V_SYS =5V, 5V_CON =Open EN = VCCA, HPD_CON = GND | 30 | 50 | µA | ||||

| Active | 5V_SYS =5V, 5V_CON =Open EN = VCCA, HPD_CON = 5V | 125 | 200 | µA | ||||

| Load Switch | ||||||||

| VREV | Reverse voltage comparator trip point | 5V_SYS=4V, 5V_CON > 5V_SYS | 100 | mV | ||||

| IOFF | Leakage Current | 5V_CON = 0V, 5V_SYS = 5 V , EN = GND, HPD_CON = GND Measured at 5V_SYS pin. | 1 | 5 | µA | |||

| 5V_CON = 0V, 5V_SYS= 5 V , EN = GND, HPD_CON = 5 V Measured at 5V_SYS pin | 1 | 5 | µA | |||||

| 5V_CON = 5V, 5V_SYS = 0 V , EN = GND, HPD_CON = GND Measured at 5V_CON pin. | 1 | 5 | µA | |||||

| 5V_CON = 5V, 5V_SYS = 0 V EN = GND, HPD_CON = 5 V Measured at 5V_CON pin. | 1 | 5 | µA | |||||

| 5V_CON = 5V, 5V_SYS = 0 V, EN=VCCA, HPD_CON = GND Measured at 5V_CON pin. | 1 | 5 | µA | |||||

| 5V_CON = 5 V, 5V_SYS = 0 V, EN = VCCA, HPD_CON = 5 V Measured at 5V_CON pin. | 1 | 5 | µA | |||||

| ISC | Short circuit current at 5V_CON | 5V_SYS = 5 V, 5V_CON = GND | 110 | 140 | 170 | mA | ||

| TDEGLITCH | Deglitch time against false short | 5V_SYS = 5 V , EN = VCCA, Short 5V_CON | 3 | µs | ||||

| UVLO | Under voltage lockout rising | 5V_SYS = 0 V to 5 V, RL = 100 Ω, CL = 1 µF | 2.85 | V | ||||

| UVLO_HYS | Under voltage lockout falling hysteresis | 5V_SYS = 5 V to 0 V, RL = 100 Ω, CL = 1 µF | 200 | mV | ||||

| VDROP | 5V_OUT output voltage drop | 5V_SYS = 5 V, I5V_OUT = 55 mA | 38.5 | 55 | mV | |||

| IRUSH | Inrush Current | 5V_SYS = 5 V, RL = 100 Ω, Cin=10uF, C = 1 µF | 140 | mA | ||||

| TON | Turn on Time, EN to 5V_CON | 5V_SYS = 5 V, RL = 100 Ω, Cin=10uF, C = 1 µF | 92.3 | µs | ||||

| TOFF | Turn off Time, EN to 5V_CON | 5V_SYS = 5 V, RL = 100 Ω, Cin=10uF, C = 1 µF | 5 | µs | ||||

| TSHUT | Thermal Shutdown | Shutdown threshold, TRIP(1) | 166 | °C | ||||

| HYST(2) | 23 | |||||||

(1) The TPD5S116 turns off after the device temperature reaches the TRIP temperature.

(2) Once the thermal shut-down circuit turns off the load switch, the switch turns on again after the device junction temperature cools down to a temperature equals to or less than TRIP-HYST.

7.6 Voltage Level Shifter, SCL, SDA Lines

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | VCCA | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|---|

| VOH_SYS | IOH = –10 µA | VI = VIH | 0.8 × VCCA | VCCA + 0.02 | V | ||||

| VOL_SYS | IOL = 10 µA | VI = VIL | 0.17 × VCCA | V | |||||

| VOH_CON | IOH = –10 µA | VI = VIH | 0.8 x 5V_SYS | 5V_SYS+ 0.02 | V | ||||

| VOL_CON | IOH = 3 mA | VI = VIL | 0.3 | 0.4 | V | ||||

| ΔVT Hysteresis at the SDx_IN (VT+ - VT-) | 40 | mV | |||||||

| ΔVT Hysteresis at the SDx_OUT (VT+ - VT-) | 400 | mV | |||||||

| RPU (Internal pull-up) | SCL_SYS, SDA_SYS | Pull-up connected to VCCA rail | 5 | kΩ | |||||

| SCL_CON, SDA_CON | Pull-up connected to 5V rail | 1.75 | |||||||

| IPULLUPAC Transient Boosted Pull-up Current (rise-time accelerator) | SCL_CON, SDA_CON | Pull-up connected to 5V rail | 13 | mA | |||||

| Ioff | SYS Port | VCCA = 0V, VI or VO = 0 to 3.6 V | 0 V | ±5 | µA | ||||

| CON Port | 5V_CON=0V, VI or VO = 0 to 5.5 V | 0 V | ±5 | ||||||

| IOZ | SYS Port | VI = VCCI or GND | ±5 | ||||||

7.7 Voltage Level Shifter, CEC Line

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | VCCA | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|---|

| VOH_SYS | IOH = –10 µA | VI = VIH | 0.8 × VCCA | VCCA + 0.02 | V | ||||

| VOL_SYS | IOL = 10 µA | VI = VIL | 0.17 × VCCA | V | |||||

| VOH_CON | IOH = –10 µA | VI = VIH | 0.8 x V3P3 | V | |||||

| VOL_CON | IOH = 3 mA | VI = VIL | 0.3 | 0.4 | V | ||||

| ΔVT Hysteresis at the CEC_SYS (VT+ - VT-) | 30 | mV | |||||||

| ΔVT Hysteresis at the CEC_CON (VT+ - VT-) | 283 | mV | |||||||

| RPU (Internal pull-up) | CEC_SYS | Pull-up connected to VCCA rail | 5 | kΩ | |||||

| CEC_CON | Pull-up connected to 3.3V rail | 22 | 26 | 30 | kΩ | ||||

| RPD (Internal pull-down) | CEC_CON | Pull-down connected connector-side | 10 | MΩ | |||||

| Ioff | SYS Port | VCCA = 0V, VI or VO = 0 to 3.6 V | 0 V | ±5 | µA | ||||

| CON Port | 5V_CON=0V, VI or VO = 0 to 5.5 V | 0 V | ±1.8 | ||||||

| IOZ | SYS Port | VI = VCCI or GND | ±5 | ||||||

7.8 Voltage Level Shifter, HPD Line

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | VCCA | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|---|

| VOH_SYS | IOH = 1 mA | VI = VIH | 1.2 V to 5.0 V | VCCA × 0.7 | V | ||||

| VOH_SYS_1P1 | IOH = 100 µA | VI = VIH | 1.1 V | VCCA × 0.7 | V | ||||

| VOL_SYS | IOL = 3 µA | VI = VIL | 1.2 V to 5.0 V | 0.4 | V | ||||

| VOL_SYS_1P1 | IOL = 3 mA | VI = VIL | 1.1 V | 0.68 | V | ||||

| ΔVT Hysteresis at the CEC_CON (VT+ - VT-) | 1.2 V to 5.0 V | 500 | mV | ||||||

| RPD_IN (Input internal pull-down resistor) | Pull-down connected to GND | 60 | 100 | 140 | kΩ | ||||

| RPD_OUT (Output internal pull-down resistor) | Pull-down connected to GND | 60 | 100 | 140 | kΩ | ||||

| TFILT | Glitch Filter Duration | HPD_CON = 5 V, EN = VCCA, Short HPD_SYS | 10 | µs | |||||

7.9 EN

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | VCCA | MIN | TYP | MAX | UNIT |

|---|---|---|---|---|---|---|

| RPD EN (Internal pull-down resistor) | Pull-down connected to GND | 1.8 V | 470 | kΩ |

7.10 Utility Pin

over operating free-air temperature range (unless otherwise noted)| PARAMETER | DESCRIPTION | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---|---|---|---|---|---|---|

| VRWM | Reverse stand-off voltage | 6 | V | |||

| VCLAMP | Clamp voltage with ESD strike | IPP = 1 A, tp = 8/20 μSec, from I/O to GND(1) | 8 | V | ||

| IPP = 5 A, tp = 8/20 μSec, , from I/O to GND(1) | 10 | |||||

| RDYN | Dynamic resistance | UTI pin to GND Pin(2) | 0.33 | Ω | ||

| CUTI | Line capacitance | VIO=0V, f=1GHz, I/O to GND | 5.5 | pF | ||

| VBR | Break-down voltage | IIO = 1mA | 7 | V | ||

| ILEAK | Leakage current | VIO = 3V | 1 | 10 | nA |

(1) Non-repetitive current pulse 8/20us exponentially decaying waveform according to IEC 61000-4-5

(2) Extraction of RDYN using least squares fit of TLP characteristics between I=10A and I=20A

7.11 I/O Capacitances

over recommended operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITONS | SUPPLY & EN SIGNAL | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|---|

| CI | EN | VBIAS = VCCA/2, f = 1 MHz, 30 mV p-p AC signal | 8 | 9 | pF | ||

| CI | HPD_CON | VBIAS = 0 V – 5 V , f = 1 MHz, 30 mV p-p AC signal | 7 | 7.5 | pF | ||

| CIO | SYS port | VBIAS = 1.8 V, f = 1 MHz, 30 mV p-p AC signal | 6.5 | 9.5 | pF | ||

| CON port | VBIAS = 2.5 V, f = 1 MHz, 30 mV p-p AC signal | 15 | 20 | pF | |||

| SCL_CON, SDA_CON | VBIAS = 2.5V, f = 100 kHz, 3.5 V p-p AC signal | VCCA= 3.6 V, 5V_SYS = 5 V, EN = HPD_CON = 0 V | 17 | pF | |||

| CEC_CON | VBIAS = 1.65 V, f = 100 kHz, 2.5 V p-p AC signal | VCCA= 3.6 V, 5V_SYS = 5 V, EN=HPD_CON = 0 V | 13 | pF | |||

| CEC_CON | VBIAS = 1.65 V, f = 100 kHz, 2.5 V p-p AC signal | VCCA= 0 V 5V_SYS = 0 V EN = HPD_CON = 0 V | 12 | pF | |||

7.12 Dynamic Load Characteristics

Propagation delays measured from 50% threshold to 50% threshold, Rise time measured from 30% to 70% threshold, Fall time measured from 70% to 30% threshold| PARAMETER | TEST CONDITION | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| CL | Bus Load Capacitance (connector-side) | 750 | pF | |||

| Bus Load Capacitance (System Side) | 30 | |||||

7.13 SCL, SDA Lines, VCCA = 1.2 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 1.2 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | DDC Channels Enabled | 316 | ns | |||

| CON to SYS | DDC Channels Enabled | 286 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | DDC Channels Enabled | 489 | ns | |||

| CON to SYS | DDC Channels Enabled | 199 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | DDC Channels Enabled | 110 | ns | |||

| TFALL | CON Port Fall Time | CON Port | DDC Channels Enabled | 82 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | DDC Channels Enabled | 229 | ns | |||

| TRISE | CON Port Rise Time | CON Port | DDC Channels Enabled | 86 | ns | |||

| FMAX | Maximum Switching Frequency | DDC Channels Enabled | 400 | kHz | ||||

7.14 CEC Line, VCCA = 1.2 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 1.2 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | CEC Channels Enabled | 436 | ns | |||

| CON to SYS | CEC Channels Enabled | 97 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | CEC Channels Enabled | 13.8 | µs | |||

| CON to SYS | CEC Channels Enabled | 319 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 37 | ns | |||

| TFALL | CON Port Fall Time | CON Port | CEC Channels Enabled | 114 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 234 | ns | |||

| TRISE | CON Port Rise Time | CON Port | CEC Channels Enabled | 16.6 | µs | |||

7.15 HPD Line, VCCA = 1.2 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 1.2 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | CON to SYS | CEC Channels Enabled | 10.1 | µs | |||

| TPLH | Propagation Delay | CON to SYS | CEC Channels Enabled | 9.7 | µs | |||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 14 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 18 | ns | |||

7.16 SCL, SDA Lines, VCCA = 1.5 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 1.5 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | DDC Channels Enabled | 297 | ns | |||

| CON to SYS | DDC Channels Enabled | 224 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | DDC Channels Enabled | 473 | ns | |||

| CON to SYS | DDC Channels Enabled | 193 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | DDC Channels Enabled | 87 | ns | |||

| TFALL | CON Port Fall Time | CON Port | DDC Channels Enabled | 82 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | DDC Channels Enabled | 226 | ns | |||

| TRISE | CON Port Rise Time | CON Port | DDC Channels Enabled | 86 | ns | |||

| FMAX | Maximum Switching Frequency | DDC Channels Enabled | 400 | kHz | ||||

7.17 CEC Line, VCCA = 1.5 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 1.5 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | CEC Channels Enabled | 419 | ns | |||

| CON to SYS | CEC Channels Enabled | 102 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | CEC Channels Enabled | 13.7 | µs | |||

| CON to SYS | CEC Channels Enabled | 314 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 39 | ns | |||

| TFALL | CON Port Fall Time | CON Port | CEC Channels Enabled | 115 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 230 | ns | |||

| TRISE | CON Port Rise Time | CON Port | CEC Channels Enabled | 16.6 | µs | |||

7.18 HPD Line, VCCA = 1.5 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 1.5 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | CON to SYS | CEC Channels Enabled | 10.1 | µs | |||

| TPLH | Propagation Delay | CON to SYS | CEC Channels Enabled | 9.7 | µs | |||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 8 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 9.5 | ns | |||

7.19 SCL, SDA Lines, VCCA = 1.8 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 1.8 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | DDC Channels Enabled | 292 | ns | |||

| CON to SYS | DDC Channels Enabled | 192 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | DDC Channels Enabled | 466 | ns | |||

| CON to SYS | DDC Channels Enabled | 190 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | DDC Channels Enabled | 75 | ns | |||

| TFALL | CON Port Fall Time | CON Port | DDC Channels Enabled | 82 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | DDC Channels Enabled | 224 | ns | |||

| TRISE | CON Port Rise Time | CON Port | DDC Channels Enabled | 86 | ns | |||

| FMAX | Maximum Switching Frequency | DDC Channels Enabled | 400 | kHz | ||||

7.20 CEC Line, VCCA = 1.8 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 1.8 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | CEC Channels Enabled | 417 | ns | |||

| CON to SYS | CEC Channels Enabled | 108 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | CEC Channels Enabled | 13.7 | µs | |||

| CON to SYS | CEC Channels Enabled | 312 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 41 | ns | |||

| TFALL | CON Port Fall Time | CON Port | CEC Channels Enabled | 114 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 228 | ns | |||

| TRISE | CON Port Rise Time | CON Port | CEC Channels Enabled | 16.6 | µs | |||

7.21 HPD Line, VCCA = 1.8 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5V; VCCA = 1.8 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | CON to SYS | CEC Channels Enabled | 10.1 | µs | |||

| TPLH | Propagation Delay | CON to SYS | CEC Channels Enabled | 9.7 | µs | |||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 5.5 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 7 | ns | |||

7.22 SCL, SDA Lines, VCCA = 2.5 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 2.5 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | DDC Channels Enabled | 291 | ns | |||

| CON to SYS | DDC Channels Enabled | 154 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | DDC Channels Enabled | 455 | ns | |||

| CON to SYS | DDC Channels Enabled | 186 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | DDC Channels Enabled | 64 | ns | |||

| TFALL | CON Port Fall Time | CON Port | DDC Channels Enabled | 82 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | DDC Channels Enabled | 221 | ns | |||

| TRISE | CON Port Rise Time | CON Port | DDC Channels Enabled | 86 | ns | |||

| FMAX | Maximum Switching Frequency | DDC Channels Enabled | 400 | kHz | ||||

7.23 CEC Line, VCCA = 2.5 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 2.5 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | CEC Channels Enabled | 421 | ns | |||

| CON to SYS | CEC Channels Enabled | 122 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | CEC Channels Enabled | 13.7 | µs | |||

| CON to SYS | CEC Channels Enabled | 311 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 49 | ns | |||

| TFALL | CON Port Fall Time | CON Port | CEC Channels Enabled | 114 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 225 | ns | |||

| TRISE | CON Port Rise Time | CON Port | CEC Channels Enabled | 16.6 | µs | |||

7.24 HPD Line, VCCA = 2.5 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 2.5 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | CON to SYS | CEC Channels Enabled | 10.1 | µs | |||

| TPLH | Propagation Delay | CON to SYS | CEC Channels Enabled | 9.7 | µs | |||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 4 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 5 | ns | |||

7.25 SCL, SDA Lines, VCCA = 3.3 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 3.3 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | DDC Channels Enabled | 292 | ns | |||

| CON to SYS | DDC Channels Enabled | 133 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | DDC Channels Enabled | 449 | ns | |||

| CON to SYS | DDC Channels Enabled | 184 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | DDC Channels Enabled | 57 | ns | |||

| TFALL | CON Port Fall Time | CON Port | DDC Channels Enabled | 82 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | DDC Channels Enabled | 218 | ns | |||

| TRISE | CON Port Rise Time | CON Port | DDC Channels Enabled | 86 | ns | |||

| FMAX | Maximum Switching Frequency | DDC Channels Enabled | 400 | kHz | ||||

7.26 CEC Line, VCCA = 3.3 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 3.3 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | CEC Channels Enabled | 428 | ns | |||

| CON to SYS | CEC Channels Enabled | 138 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | CEC Channels Enabled | 13.7 | µs | |||

| CON to SYS | CEC Channels Enabled | 309 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 59 | ns | |||

| TFALL | CON Port Fall Time | CON Port | CEC Channels Enabled | 114 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 223 | ns | |||

| TRISE | CON Port Rise Time | CON Port | CEC Channels Enabled | 16.6 | µs | |||

7.27 HPD Line, VCCA = 3.3 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 3.3 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | CON to SYS | CEC Channels Enabled | 10.1 | µs | |||

| TPLH | Propagation Delay | CON to SYS | CEC Channels Enabled | 9.7 | µs | |||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 3 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 3.5 | ns | |||

7.28 SCL, SDA Lines, VCCA = 5 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 5 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | DDC Channels Enabled | 298 | ns | |||

| CON to SYS | DDC Channels Enabled | 113 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | DDC Channels Enabled | 442 | ns | |||

| CON to SYS | DDC Channels Enabled | 182 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | DDC Channels Enabled | 52 | ns | |||

| TFALL | CON Port Fall Time | CON Port | DDC Channels Enabled | 82 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | DDC Channels Enabled | 217 | ns | |||

| TRISE | CON Port Rise Time | CON Port | DDC Channels Enabled | 86 | ns | |||

| FMAX | Maximum Switching Frequency | DDC Channels Enabled | 400 | kHz | ||||

7.29 CEC Line, VCCA = 5 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 5 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | SYS to CON | CEC Channels Enabled | 446 | ns | |||

| CON to SYS | CEC Channels Enabled | 169 | ns | |||||

| TPLH | Propagation Delay | SYS to CON | CEC Channels Enabled | 13.7 | µs | |||

| CON to SYS | CEC Channels Enabled | 306 | ns | |||||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 82 | ns | |||

| TFALL | CON Port Fall Time | CON Port | CEC Channels Enabled | 114 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 221 | ns | |||

| TRISE | CON Port Rise Time | CON Port | CEC Channels Enabled | 16.6 | µs | |||

7.30 HPD Line, VCCA = 5 V

over operating free-air temperature range (unless otherwise noted) and 5V_CON = 5 V; VCCA = 5 V| PARAMETER | PINS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| TPHL | Propagation Delay | CON to SYS | CEC Channels Enabled | 10.1 | µs | |||

| TPLH | Propagation Delay | CON to SYS | CEC Channels Enabled | 9.7 | µs | |||

| TFALL | SYS Port Fall Time | SYS Port | CEC Channels Enabled | 2.5 | ns | |||

| TRISE | SYS Port Rise Time | SYS Port | CEC Channels Enabled | 2.5 | ns | |||

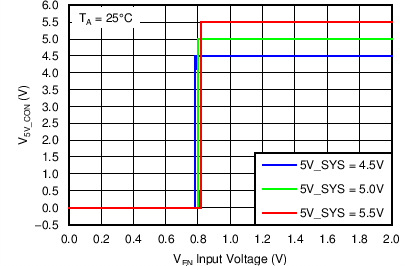

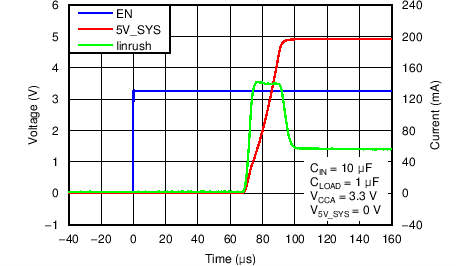

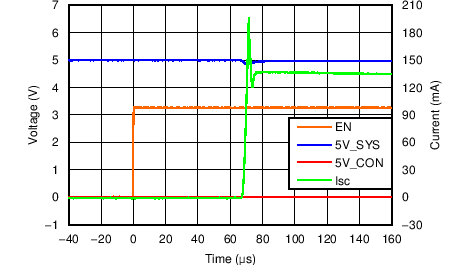

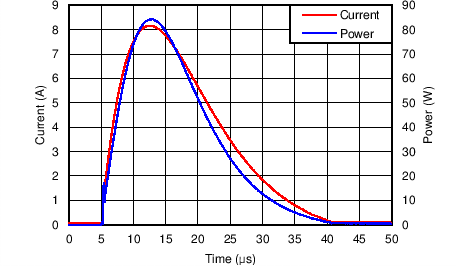

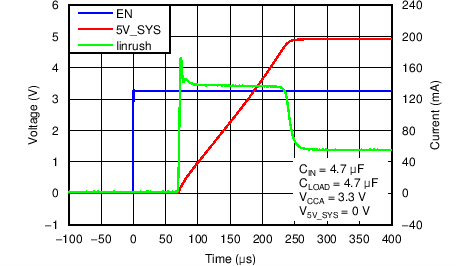

7.31 Typical Characteristics

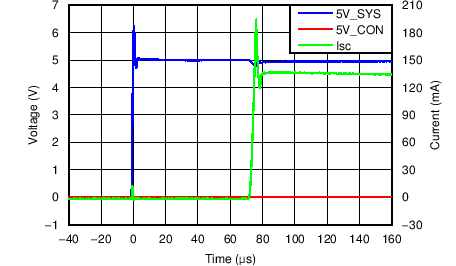

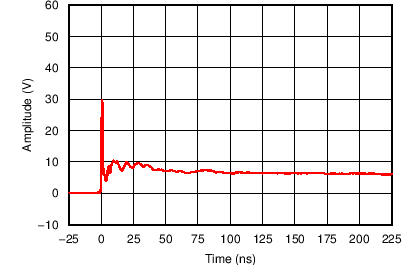

At TA = 25°C, unless otherwise noted. Figure 1. Power up to Short Circuit

Figure 1. Power up to Short Circuit

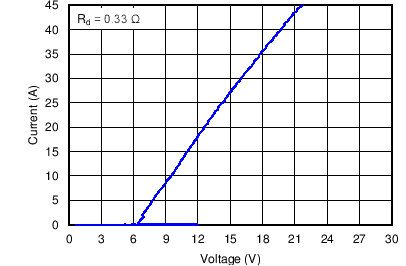

Figure 3. Utility Pin TLP Curve

Figure 3. Utility Pin TLP Curve

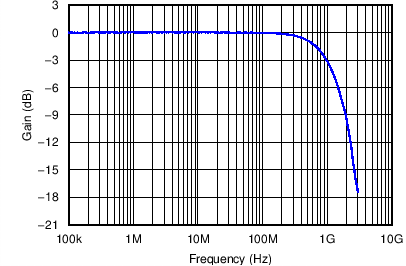

Figure 5. Utility Pin Insertion Loss

Figure 5. Utility Pin Insertion Loss

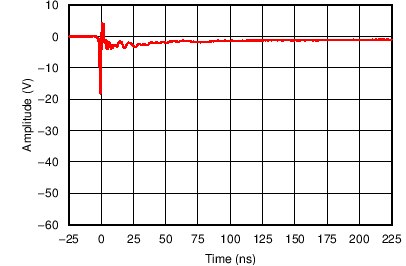

Figure 7. Utility Pin, -8kv IEC Voltage Clamp Waveform

Figure 7. Utility Pin, -8kv IEC Voltage Clamp Waveform

Figure 9. EN VTH

Figure 9. EN VTH

Figure 11. I5V_SYS vs. Temperature

Figure 11. I5V_SYS vs. Temperature

Figure 13. IINRUSH Waveform

Figure 13. IINRUSH Waveform

Figure 2. Enable to Short Circuit

Figure 2. Enable to Short Circuit

Figure 4. Utility Pin Surge Curves

Figure 4. Utility Pin Surge Curves

Figure 6. Utility Pin, +8kv IEC Voltage Clamp Waveform

Figure 6. Utility Pin, +8kv IEC Voltage Clamp Waveform

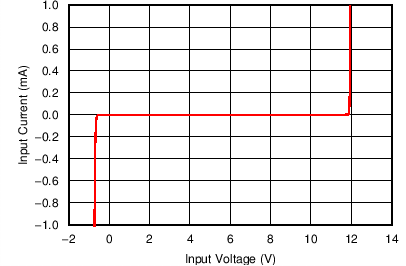

Figure 8. Utility Pin IV Curve

Figure 8. Utility Pin IV Curve

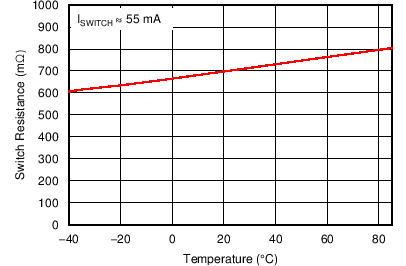

Figure 10. RDS for ISWITCH

Figure 10. RDS for ISWITCH

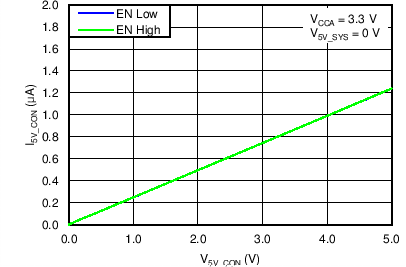

Figure 12. Reverse Switch Current

Figure 12. Reverse Switch Current

Figure 14. IINRUSH Waveform

Figure 14. IINRUSH Waveform