ZHCSBD2B September 2013 – January 2015 TPA3131D2 , TPA3132D2

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Gain Setting and Master and Slave

- 7.3.2 Input Impedance

- 7.3.3 Start-up/Shutdown Operation

- 7.3.4 PLIMIT Operation

- 7.3.5 GVDD Supply

- 7.3.6 BSPx and BSNx Capacitors

- 7.3.7 Differential Inputs

- 7.3.8 Device Protection System

- 7.3.9 DC Detect Protection

- 7.3.10 Short-Circuit Protection and Automatic Recovery Feature

- 7.3.11 Thermal Protection

- 7.3.12 Efficiency: LC Filter Required with the Traditional Class-D Modulation Scheme

- 7.3.13 Ferrite Bead Filter Considerations

- 7.3.14 When to Use an Output Filter for EMI Suppression

- 7.3.15 AM Avoidance EMI Reduction

- 7.4 Device Functional Modes

- 8 Applications and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

8 Applications and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

This section describes a typical stereo speaker application with differential inputs. The amplifier gain is set to

26 dB and the output PWM is set to 400 kHz.

8.2 Typical Application

Figure 29. Typical Application Schematic

Figure 29. Typical Application Schematic

8.2.1 Design Requirements

| DESIGN PARAMETERS | EXAMPLE VALUE |

|---|---|

| Input voltage range PVCC | 4.5 V to 26 V |

| PWM output frequencies | 400 kHz, 500 kHz, 600 kHz, 1 MHz or 1.2 MHz |

| Maximum output power | 25 Wx2 (TPA3132D2) or 4 Wx2 (TPA3131D2) |

8.2.2 Detailed Design Procedure

The TPA31xxD2 is a very flexible and easy to use Class D amplifier; therefore the design process is straightforward. Before beginning the design, gather the following information regarding the audio system.

- PVCC rail planned for the design

- Speaker or load impedance

- Maximum output power requirement

- Desired PWM frequency

8.2.2.1 Select the PWM Frequency

Set the PWM frequency by using AM0, AM1 and AM2 pins.

8.2.2.2 Select the Amplifier Gain and Master/Slave Mode

In order to select the amplifier gain setting, the designer must determine the maximum power target and the speaker impedance. Once these parameters have been determined, calculate the required output voltage swing which delivers the maximum output power.

Choose the lowest analog gain setting that corresponds to produce an output voltage swing greater than the required output swing for maximum power. The analog gain and master/slave mode can be set by selecting the voltage divider resistors (R1 and R2) on the Gain/SLV pin.

8.2.2.3 Select Input Capacitance

Select the bulk capacitors at the PVCC inputs for proper voltage margin and adequate capacitance to support the power requirements. In practice, with a well-designed power supply, two 100-μF, 50-V capacitors should be sufficient. One capacitor should be placed near the PVCC inputs at each side of the device. PVCC capacitors should be a low ESR type because they are being used in a high-speed switching application.

8.2.2.4 Select Decoupling Capacitors

Good quality decoupling capacitors need to be added at each of the PVCC inputs to provide good reliability, good audio performance, and to meet regulatory requirements. X5R or better ratings should be used in this application. Consider temperature, ripple current, and voltage overshoots when selecting decoupling capacitors. Also, these decoupling capacitors should be located near the PVCC and GND connections to the device in order to minimize series inductances.

8.2.2.5 Select Bootstrap Capacitors

Each of the outputs require bootstrap capacitors to provide gate drive for the high-side output FETs. For this design, use 0.22-μF, 25-V capacitors of X5R quality or better.

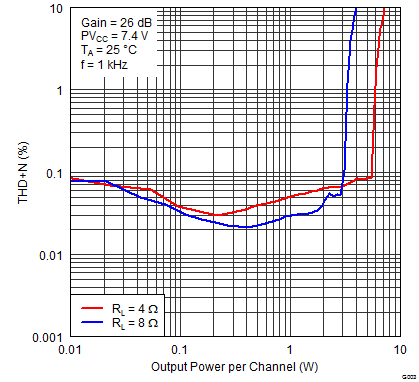

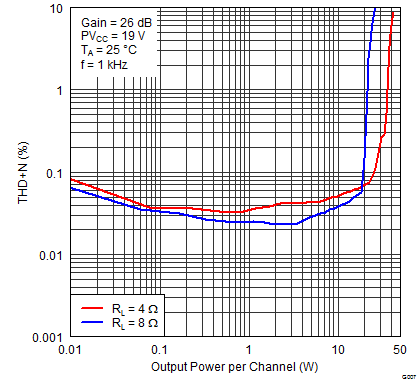

8.2.3 Application Curves

Figure 30. Total Harmonic Distortion + Noise (BTL) vs Output Power

Figure 30. Total Harmonic Distortion + Noise (BTL) vs Output Power

Figure 31. Total Harmonic Distortion + Noise (BTL) vs Output Power

Figure 31. Total Harmonic Distortion + Noise (BTL) vs Output Power