ZHCSQL1 May 2022 DP83TC813R-Q1 , DP83TC813S-Q1

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4

Device Functional Modes

- 8.4.1 Power Down

- 8.4.2 Reset

- 8.4.3 Standby

- 8.4.4 Normal

- 8.4.5 Sleep Ack

- 8.4.6 Sleep Request

- 8.4.7 Sleep Fail

- 8.4.8 Sleep

- 8.4.9 Wake-Up

- 8.4.10 TC10 System Example

- 8.4.11 Media Dependent Interface

- 8.4.12 MAC Interfaces

- 8.4.13 Serial Management Interface

- 8.4.14 Direct Register Access

- 8.4.15 Extended Register Space Access

- 8.4.16 Write Address Operation

- 8.4.17 Read Address Operation

- 8.4.18 Write Operation (No Post Increment)

- 8.4.19 Read Operation (No Post Increment)

- 8.4.20 Write Operation (Post Increment)

- 8.4.21 Read Operation (Post Increment)

- 8.5 Programming

- 8.6 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

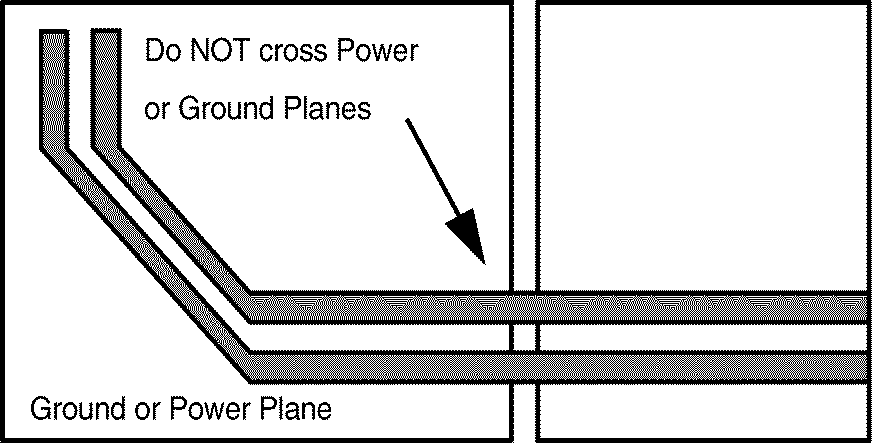

11.1.2 Return Path

A general best practice is to have a solid return path beneath all signal traces. This return path can be a continuous ground or DC power plane. Reducing the width of the return path can potentially affect the impedance of the signal trace. This effect is more prominent when the width of the return path is comparable to the width of the signal trace. Breaks in return path between the signal traces must be avoided at all cost. A signal crossing a split plane may cause unpredictable return path currents and could impact signal quality and result in emissions issues.

Figure 11-2 Power and Ground Plane Breaks

Figure 11-2 Power and Ground Plane Breaks