ZHCSDS2E November 2014 – February 2021 DLPC3439

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Power Electrical Characteristics

- 6.6 Pin Electrical Characteristics

- 6.7 Internal Pullup and Pulldown Electrical Characteristics

- 6.8 DMD Sub-LVDS Interface Electrical Characteristics

- 6.9 DMD Low-Speed Interface Electrical Characteristics

- 6.10 System Oscillator Timing Requirements

- 6.11 Power Supply and Reset Timing Requirements

- 6.12 Parallel Interface Frame Timing Requirements

- 6.13 Parallel Interface General Timing Requirements

- 6.14 Flash Interface Timing Requirements

- 6.15 Other Timing Requirements

- 6.16 DMD Sub-LVDS Interface Switching Characteristics

- 6.17 DMD Parking Switching Characteristics

- 6.18 Chipset Component Usage Specification

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5 Programming

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

3 说明

DLPC3439 数字控制器是 DLP4710 (.47 1080p) 芯片组的一部分,为 DLP4710 数字微镜器件 (DMD) 的可靠运行提供支持。DLPC3439 控制器在系统电子设备与 DMD 之间提供一个方便的多功能接口,从而实现小外形尺寸的低功耗高分辨率全高清显示屏。

访问 TI DLP®Pico™ 显示技术入门页面,并查看编程人员指南了解详情。

该芯片组提供现成的资源,可帮助用户加快设计周期。这些资源包括可直接用于生产环境的光学模块、光学模块制造商和设计公司。

器件信息(1)

| 器件型号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| DLPC3439 | NFBGA (201) | 13.00 × 13.00mm2 |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

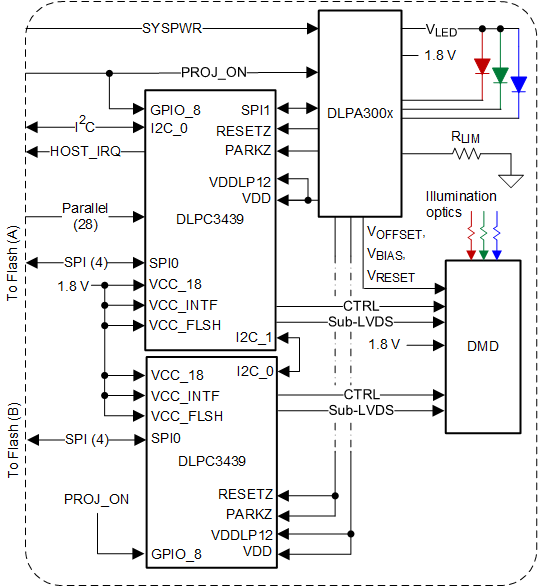

典型简化系统图

典型简化系统图