ZHCU410B December 2017 – November 2022

2.4.2 用于控制 VCC1 的 STO_1 信号流路径

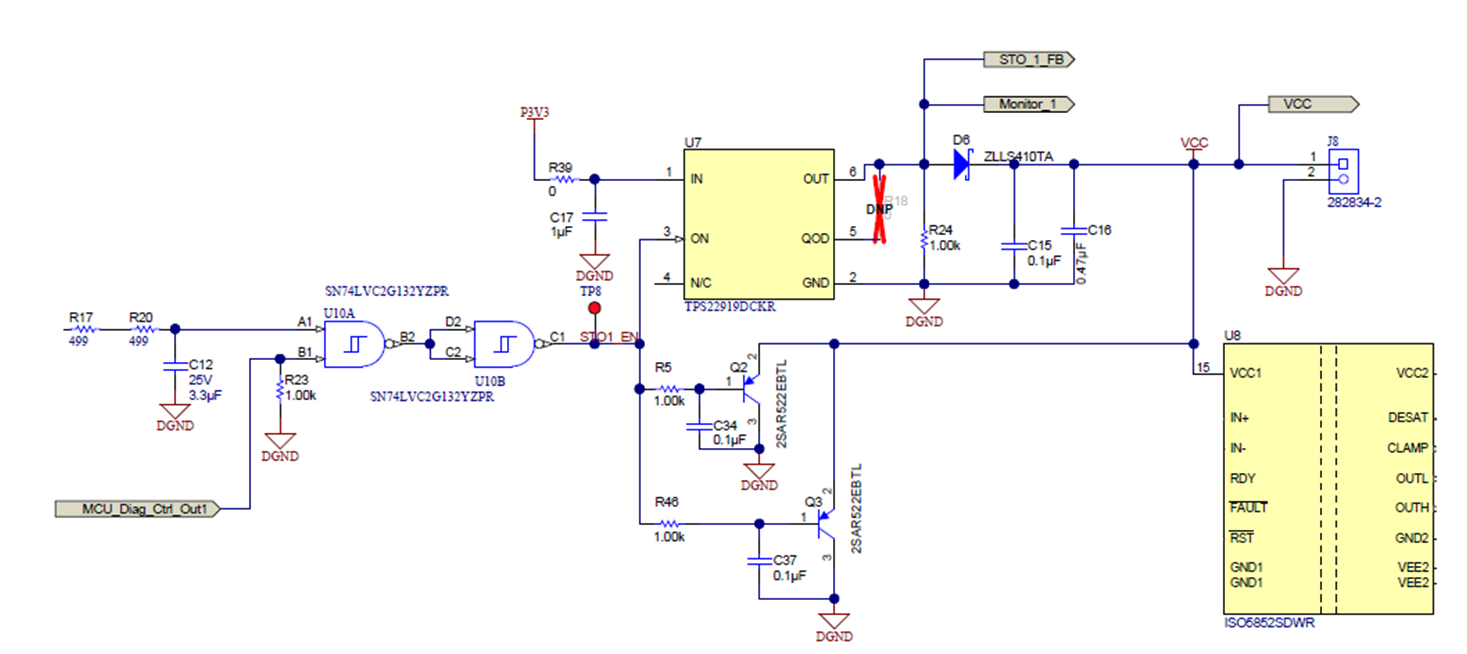

TPS22919 是一款小型、超低泄漏电流、单通道负载开关。图 2-11 显示了 TPS22860 的原理图设计。

图 2-11 TPS22919 原理图

图 2-11 TPS22919 原理图器件电源为 3.3V 并假定电源具备故障保护功能且能够保持在 ±20% 容差范围内。若要限制输入电源的压降(由开关导通时流入放电负载电容器的瞬态浪涌电流引起),应在 VIN 和 GND 引脚之间放置一个 1 µF 的陶瓷电容器。

ON 引脚与标准 GPIO 逻辑阈值兼容,用于通过信号 STO1_EN 控制开关的状态。QOD 引脚会保持开路,并且在 ON 引脚处于逻辑低电平时,输出将保持浮动。

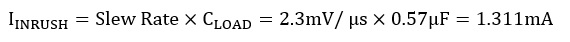

可使用Equation5 来计算给定电容和压摆率条件下导通期间的浪涌电流。

Equation5.

开关的输出端连接至栅极驱动器 3.3V 电源的初级侧 (VCC)。在 STO_1 激活时,双冗余 PNP 双极结晶体管 Q2 和 Q3 会主动将逻辑侧栅极驱动电源 VCC 钳制至 GND。这可防止 VCC 电源的反向偏置流过 CMOS 输入栅极驱动器 ISO5852S(或 ISO5452),以防 PWM 信号仍处于高电平有效 (3V3) 状态。