KOKA018B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

3.1 디지털 전원 공급 장치

장치에는 다음과 같은 5가지 리셋 수준이 있습니다.

- POR(파워 온 리셋)

- BOR(브라운 아웃 리셋)

- BOOTRST(부팅 리셋)

- SYSRST(시스템 리셋)

- CPURST(CPU 리셋)

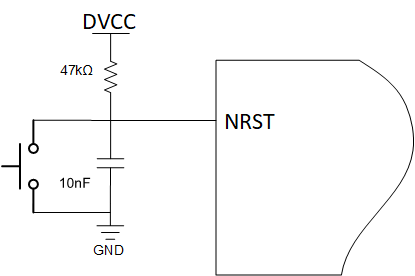

콜드 스타트 후 NRST 핀이 NRST 모드로 구성됩니다. 장치가 성공적으로 부팅되려면 NRST 핀이 높아야 합니다. NRST에는 내부 풀업 저항이 없습니다. 장치를 시작하려면 외부 회로(DVCC에 대한 풀업 저항 또는 리셋 제어 회로)가 NRST를 적극적으로 높여야 합니다. 수동 리셋을 위해 커패시터와 열기 버튼이 필요합니다(그림 3-1 참조). 장치가 시작된 후 NRST에서 지속 시간이 1초 미만인 낮은 펄스는 BOOTRST를 트리거합니다. NRST의 낮은 펄스가 1초보다 길면 POR이 트리거됩니다.

그림 3-1 NRST 권장 회로

그림 3-1 NRST 권장 회로