ZHCSR97K april 1998 – february 2023 SN74LV574A

PRODMIX

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 Timing Requirements, VCC = 2.5 V ± 0.2 V

- 6.7 Timing Requirements, VCC = 3.3 V ± 0.3 V

- 6.8 Timing Requirements, VCC = 5 V ± 0.5 V

- 6.9 Switching Characteristics, VCC = 2.5 V ± 0.2 V

- 6.10 Switching Characteristics, VCC = 3.3 V ± 0.3 V

- 6.11 Switching Characteristics, VCC = 5 V ± 0.5 V

- 6.12 Noise Characteristics

- 6.13 Operating Characteristics

- 6.14 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

封装选项

请参考 PDF 数据表获取器件具体的封装图。

机械数据 (封装 | 引脚)

- DGV|20

- DB|20

- NS|20

- PW|20

- DW|20

- RGY|20

散热焊盘机械数据 (封装 | 引脚)

- RGY|20

订购信息

3 说明

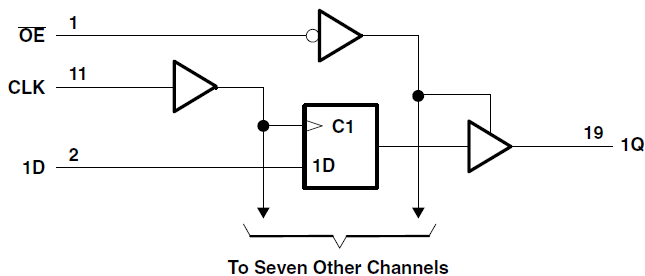

'LV574A 器件是八路边沿触发 D 类触发器,旨在于 2V 至 5.5V VCC 下运行。

这些器件具有专门设计用于驱动高容性或较低阻抗负载的三态输出。这些器件特别适用于实现缓冲寄存器、I/O 端口、双向总线驱动器和工作寄存器。

在时钟 (CLK) 输入发生正转换时,Q 输出被设置为在数据 (D) 输入端设置的逻辑电平。

封装信息(1)

| 器件型号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| SN74LV574A | DB (SSOP, 16) | 6.2mm × 5.3mm |

| DGV (TVSOP, 16) | 3.6mm × 4.4mm | |

| DW(SOIC,16) | 10.3mm × 7.5mm | |

| NS(SOP,16) | 10.3mm × 5.3mm | |

| PW (TSSOP, 16) | 5mm × 4.4mm | |

| RGY(VQFN,16) | 4mm × 3.5mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

逻辑图(正逻辑)

逻辑图(正逻辑)