ZHCSF03 March 2016 CDCM6208V2G

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 简化电路原理图

- 5 修订历史记录

- 6 说明 (续)

- 7 Pin Configuration and Functions

-

8 Specifications

- 8.1 Absolute Maximum Ratings

- 8.2 ESD Ratings

- 8.3 Recommended Operating Conditions

- 8.4 Thermal Information, Airflow = 0 LFM

- 8.5 Thermal Information, Airflow = 150 LFM

- 8.6 Thermal Information, Airflow = 250 LFM

- 8.7 Thermal Information, Airflow = 500 LFM

- 8.8 Single Ended Input Characteristics

- 8.9 Single Ended Input Characteristics (PRI_REF, SEC_REF)

- 8.10 Differential Input Characteristics (PRI_REF, SEC_REF)

- 8.11 Crystal Input Characteristics (SEC_REF)

- 8.12 Single Ended Output Characteristics (STATUS1, STATUS0, SDO, SDA)

- 8.13 PLL Characteristics

- 8.14 LVCMOS Output Characteristics

- 8.15 LVPECL (High-Swing CML) Output Characteristics

- 8.16 CML Output Characteristics

- 8.17 LVDS (Low-Power CML) Output Characteristics

- 8.18 HCSL Output Characteristics

- 8.19 Output Skew and Sync to Output Propagation Delay Characteristics

- 8.20 Device Individual Block Current Consumption

- 8.21 Worst Case Current Consumption

- 8.22 I2C TIMING

- 8.23 SPI Timing Requirements

- 8.24 Typical Characteristics

- 9 Parameter Measurement Information

- 10Detailed Description

-

11Application and Implementation

- 11.1 Application Information

- 11.2

Typical Applications

- 11.2.1

Design Requirements

- 11.2.1.1 Device Block-level Description

- 11.2.1.2 Device Configuration Control

- 11.2.1.3 Configuring the RESETN Pin

- 11.2.1.4 Preventing False Output Frequencies in SPI/I2C Mode at Startup:

- 11.2.1.5 Power Down

- 11.2.1.6 Device Power Up Timing:

- 11.2.1.7 Input Mux and Smart Input Mux

- 11.2.1.8 Universal INPUT Buffer (PRI_REF, SEC_REF)

- 11.2.1.9 VCO Calibration

- 11.2.1.10 Reference Divider (R)

- 11.2.1.11 Input Divider (M)

- 11.2.1.12 Feedback Divider (N)

- 11.2.1.13 Prescaler Dividers (PS_A, PS_B)

- 11.2.1.14 Phase Frequency Detector (PFD)

- 11.2.1.15 Charge Pump (CP)

- 11.2.1.16

Programmable Loop Filter

- 11.2.1.16.1 Loop Filter Component Selection

- 11.2.1.16.2 Device Output Signaling

- 11.2.1.16.3 Integer Output Divider (IO)

- 11.2.1.16.4 Fractional Output Divider (FOD)

- 11.2.1.16.5 Output Synchronization

- 11.2.1.16.6 Output MUX on Y4 and Y5

- 11.2.1.16.7 Staggered CLK Output Powerup for Power Sequencing of a DSP

- 11.2.2 Detailed Design Procedure

- 11.2.3 Application Performance Plots

- 11.2.1

Design Requirements

- 12Power Supply Recommendations

- 13Layout

- 14器件和文档支持

- 15机械、封装和可订购信息

13 Layout

13.1 Layout Guidelines

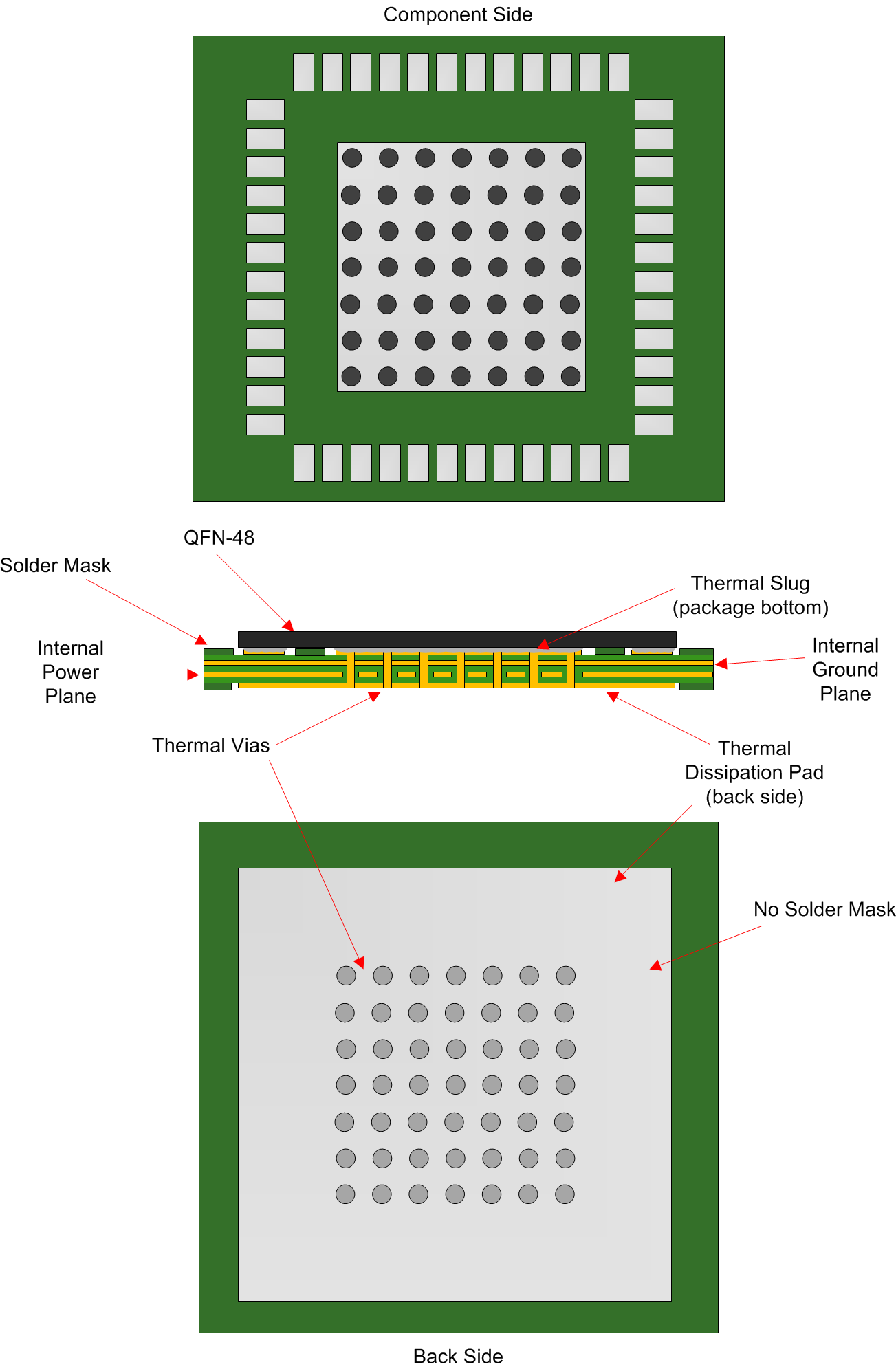

Employing the thermally enhanced printed circuit board layout shown in Figure 58 insures good thermal performance of the solution. Observing good thermal layout practices enables the thermal pad on the backside of the QFN-48 package to provide a good thermal path between the die contained within the package and the ambient air. This thermal pad also serves as the ground connection the device; therefore, a low inductance connection to the ground plane is essential.

13.2 Layout Example

Figure 58 shows a layout optimized for good thermal performance and a good power supply connection as well. The 7×7 filled via pattern facilitates both considerations.

Figure 58. Recommended PCB layout of CDCM6208

Figure 58. Recommended PCB layout of CDCM6208

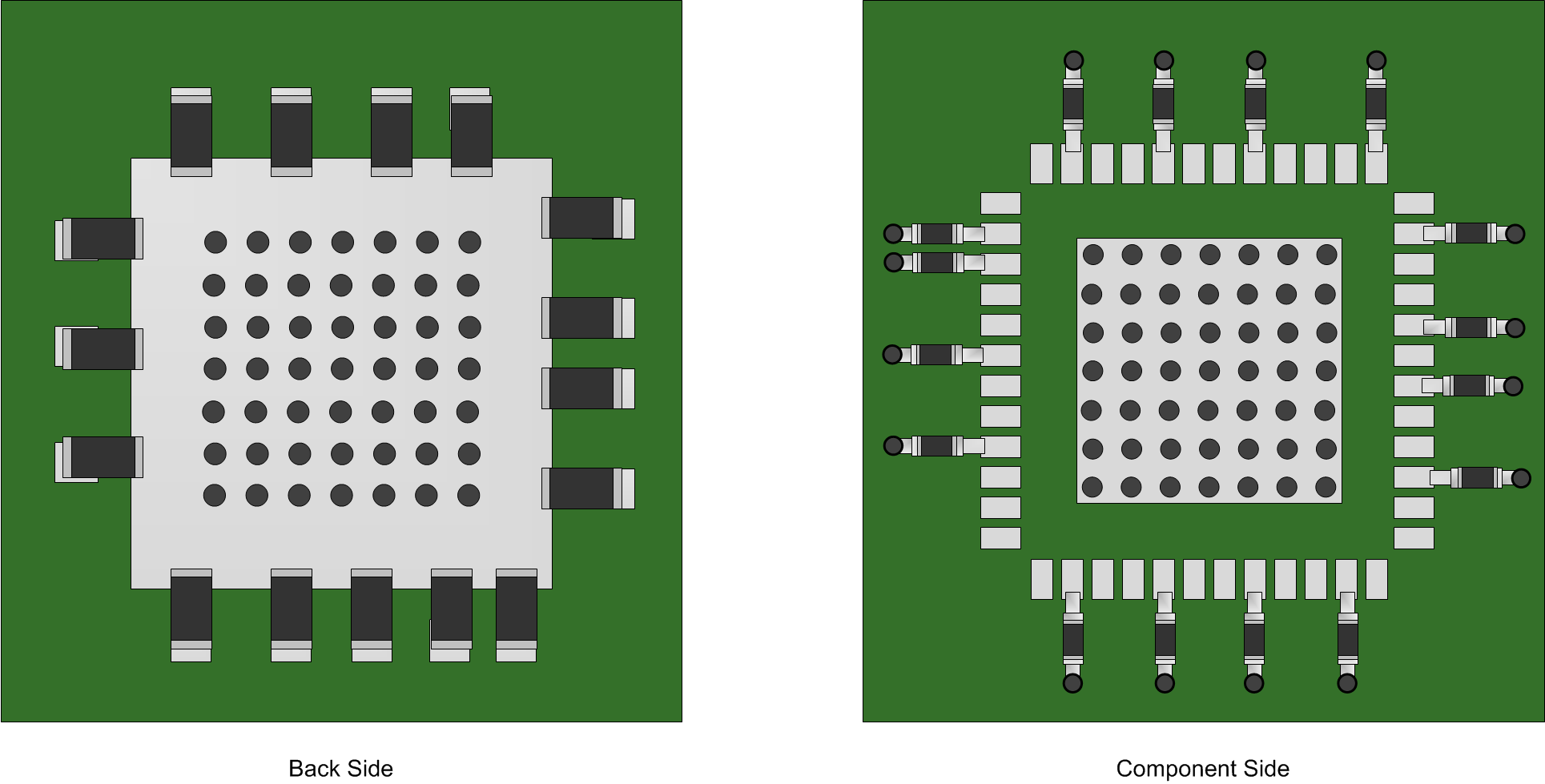

Figure 59 shows two conceptual layouts detailing recommended placement of power supply bypass capacitors. If the capacitors are mounted on the back side, 0402 components can be employed; however, soldering to the Thermal Dissipation Pad can be difficult. For component side mounting, use 0201 body size capacitors to facilitate signal routing. Keep the connections between the bypass capacitors and the power supply on the device as short as possible. Ground the other side of the capacitor using a low impedance connection to the ground plane.

Figure 59. PCB Conceptual Layouts

Figure 59. PCB Conceptual Layouts

13.2.1 Reference Schematic

Figure 60. Schematic Page 1

Figure 60. Schematic Page 1

Figure 61. Schematic Page 2

Figure 61. Schematic Page 2

Figure 62. Schematic Page 3

Figure 62. Schematic Page 3

Figure 63. Schematic Page 4

Figure 63. Schematic Page 4