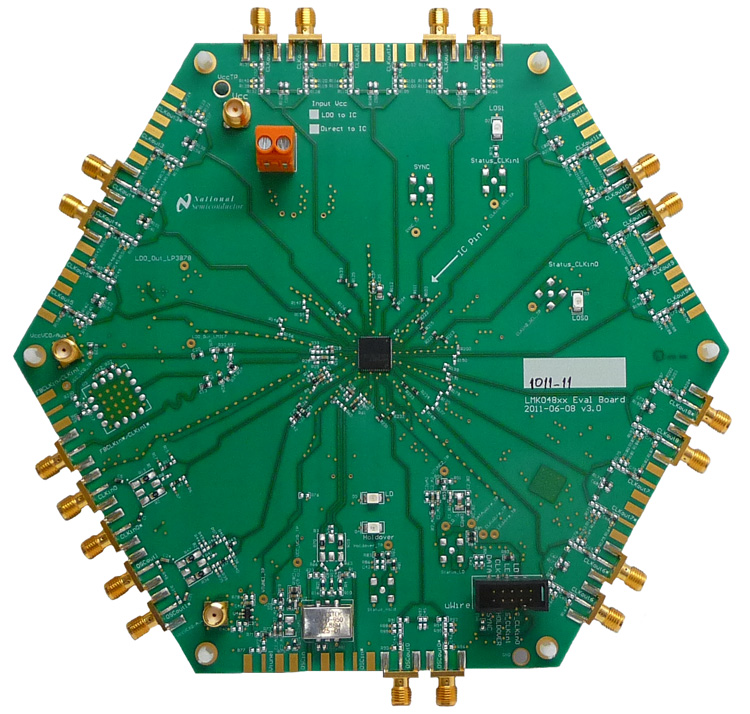

LMK04816BEVAL 的特性

- 多模式:双 PLL、单 PLL 和时钟分配

- 双环路 PLLatinum PLL 架构

- PLL1

- 输入时钟丢失时采用保持模式

- 自动或手动触发/恢复

- PLL2

- 集成低噪声 (VCO)

- 3 个带有 LOS 的冗余输入时钟

- 自动和手动切换模式

- 50% 占空比输出分频,1 至 1045(偶数和奇数

- LVPECL、LVDS 或 LVCMOS 可编程输出

- 精密数字延迟,固定或动态可调

- 25 ps 步长模拟延迟控制

- 13 路差分输出。多达 26 个单端。

- 多达 6 个 VCXO/晶振缓冲输出

- 0 延迟模式

LMK04816BEVAL 的说明

LMK04816 是业界性能卓越的时钟调节器,具有优异的时钟抖动消除、时钟发生和分配功能,其先进的功能可满足下一代系统要求。借助双环路 PLLatinum™ 架构,可利用低噪声 VCXO 模块实现 111fs rms 抖动(12kHz 至 20MHz),也可采用低成本外部晶振及变容二极管实现低于 200fs 的 rms 抖动(12kHz 至 20MHz)。

双环架构由两个高性能锁相环 (PLL)、一个低噪声晶体振荡器电路以及一个高性能压控振荡器 (VCO) 构成。第一个 PLL (PLL1) 具有低噪声抖动消除器功能,而第二个 PLL (PLL2) 执行时钟生成。PLL1 可配置为与外部 VCXO 模块配合使用,或与具有外部可调晶体和变容二极管的集成式晶体振荡器配合使用。当环路带宽较窄时,PLL1 使用 VCXO 模块或可调晶体的优异近端相位噪声(偏移低于 50kHz)清理输入时钟。PLL1 的输出将用作 PLL2 的清理输入参考,以锁定集成式 VCO。可对 PLL2 的环路带宽进行优化以清理远端相位噪声(偏移高于 50 kHz),集成式 VCO 优于 VCXO 模块或 PLL1 中使用的可调晶体。