ZHCT556 July 2024 SN65DSI83 , SN65DSI84 , SN65DSI85

摘要

随着系统级芯片 (SoC) 和显示屏技术的不断进步,两者间视频信号的兼容性成为设计挑战。为解决这一问题,视频信号桥接芯片(Bridge)应运而生,它们作为中介,将 SoC 或图形处理单元 (GPU) 产生的视频信号转换为显示屏所能接收的格式,确保信号的顺利传输与显示。 TI 作为世界领先的半导体器件公司,其产品 SN65DSI8x 系列桥接芯片不仅解决了现代电子设备中信号转换的难题,更为设计者提供了构建高质量显示系统的有力工具。 本文总结了SN65DSI8x 系列选型方法,软件使用指南,有助于工程师更高效地设计出更具竞争力的显示产品。

SN65DSI8x的分类

SN65DSI8x 包含 SN65DSI83,SN65DSI84, SN65DSI85 三个不同的型号,SN65DSI83-Q1, SN65DSI84-Q1, SN65DSI85-Q1 为对应的车规版本。

三者主要特点如下:

SN65DSI83:

- 单通道 MIPI DSI 输入,单通道 LVDS 输出

- 输入 DSI 时钟:40 - 500 MHz; LVDS 输出时钟范围:25–154 MHz

- DSI 支持最多4个通道,每个通道 1 Gbps

SN65DSI84:

- 单通道 MIPI DSI 输入,双通道 LVDS 输出

- 输入 DSI 时钟:40 - 500 MHz; 每个 LVDS 输出时钟范围:25–154 MHz

- DSI 支持最多 4 个通道,每个通道 1 Gbps

SN65DSI85:

- 双通道 MIPI DSI 输入,双通道 LVDS 输出

- 输入 DSI 时钟:40 - 500 MHz; 每个 LVDS 输出时钟范围:25–154 MHz

- 两个 DSI 通道,每个 DSI 通道支持最多 4 个通道,每个通道 1 Gbps;

三者主要区别如图 1所示:

图 1 SN65DSI83/84/85 区别

图 1 SN65DSI83/84/85 区别根据应用场景选择对应的 SN65DSI8x 型号

应用1:SN65DSI83 单通道输入,单通道输出 Single-channel DSI to Single-channel LVDS

选型前,需要了解屏幕的具体参数信息,以应用1屏幕参数示例,其屏幕刷新率为60Hz 所示的屏幕参数为例,先确认屏幕分辨率和Blanking等信息。

图 2 应用1屏幕参数示例,其屏幕刷新率为60Hz

图 2 应用1屏幕参数示例,其屏幕刷新率为60Hz根据屏幕参数,能够计算出输出的 LVDS LCK。根据应用1屏幕参数示例,其屏幕刷新率为60Hz 的参数可以计算出 LVDS CLK = Htotal × Vtotal × 60 = 51.2MHz,如果没有 Total 值可以用公式(1),Blanking 取 20%,建议能够拿到完整的 blanking 信息,这样计算才准确。而 SN65DSI83 的输出时钟频率范围是 25-154 MHz, 所以满足 SN65DSI83 的输出要求。

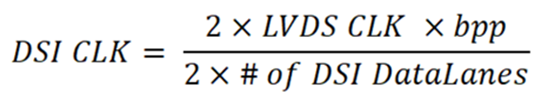

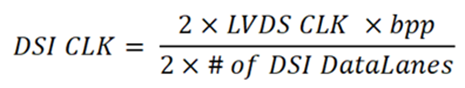

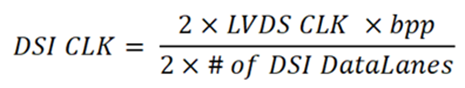

对应的输入要求呢, SN65DSI83-Q1为单通道输出, bpp 取 24,需要用到公式(2):

假设 LVDS CLK 频率为之前提供的 51.2 MHz,同时假设屏幕是 24 bpp(使用 4个 LVDS数据通道)并且 SN65DSI83上的所有 4个 DSI 数据通道都将被使用。将这些数据代入公式,我们得到 DSI CLK 频率为 153.6 MHz。SN65DSI83支持的 DSI CLK 输入范围是 40-500 MHz,所以输入也满足 SN65DSI83 要求。

应用2:SN65DSI84单通道输入,双通道输出 Single-channel DSI to dual-channel LVDS

单通道输入双 LVDS 显示的应用场景时,选择 SN65DSI84 桥接芯片。基于按照应用2屏幕参数示例,其屏幕刷新率为60Hz给的屏幕参数来计算,对于双 LVDS 显示器,这种情况下,显示器有两组 LVDS 时钟。如果需要的频率是 45.3 MHz.

图 3 应用2屏幕参数示例,其屏幕刷新率为60Hz

图 3 应用2屏幕参数示例,其屏幕刷新率为60Hz在 DSI 到双通道 LVDS 的应用场景下,DSI CLK 频率的计算与单通道应用不同,因为当涉及到双通道 LVDS时,DSI CLK 需要同时支持两个 LVDS CLK 的需求,DSI CLK 需要参考公式(3)。带入应用2屏幕参数示例,其屏幕刷新率为60Hz的参数进行计算,得到 DSI 时钟频率大约是 271.8 MHz。SN65DSI84 支持的 DSI 时钟频率范围是 40 MHz 到 500 MHz,所以 271.8 MHz 在这个范围内符合芯片要求。

应用3:SN65DSI85 双通道输入,双通道输出 Dual-channel DSI to dual-channel LVDS

图 4 应用3屏幕参数示例,其屏幕刷新率为60Hz(同应用2)

图 4 应用3屏幕参数示例,其屏幕刷新率为60Hz(同应用2)使用与单通道 DSI 到双通道 LVDS 部分相同的情况相同,都涉及到双 LVDS 显示屏,但是输入部分变成双 DSI,这时就要选择 SN65DSI85,且 SN65DSI85 的两个时钟每一个都能支持 25 - 154 MHz 范围内的频率。由于现在有两个 LVDS 时钟,DSI CLK 频率的计算公式将与单通道 DSI 转双通道 LVDS 部分的公式相同,参考公式(4),计算得出 DSI CLK 为 135.9 MHz。

通过 DSI-TUNER 生产对应配置代码

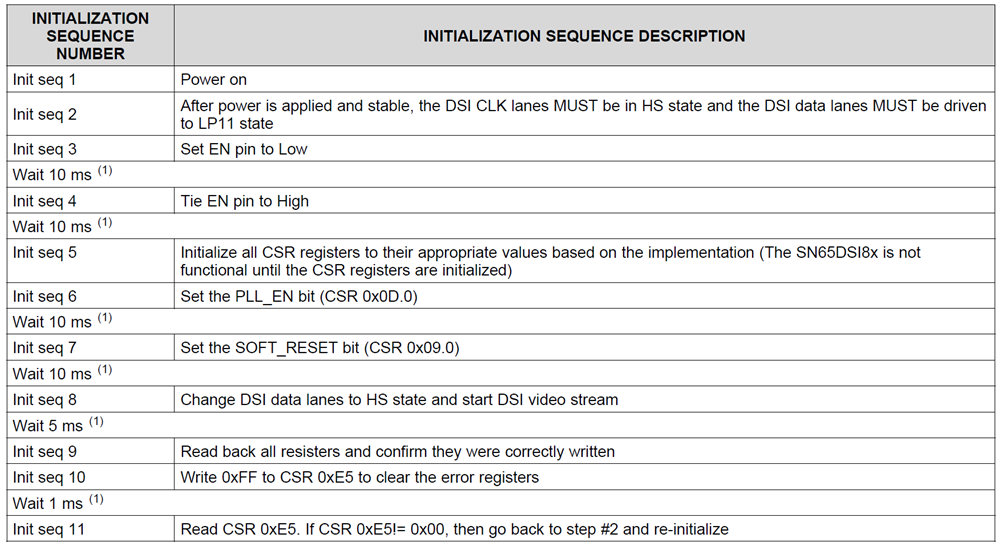

下面以 SN65DSI83为例说明,如何使用 DSI Tuner 软件工具来完成 SN65DSI8x 的软件配置,并完成初始化代码的导出。其中 DSI Tuner 生成的代码能够直接用于视频信息和相关寄存器的配置。SN65DSI83初始化流程 是其初始化流程,需要对应规格书中正确的推荐顺序来设置,在 int seq5 的时候需要对寄存器 Control and Status Registers (CSR) 进行配置,此步骤可以直接使用 DSI Tuner 生成的代码。

图 5 SN65DSI83初始化流程

图 5 SN65DSI83初始化流程DSI Tuner 使用流程详解

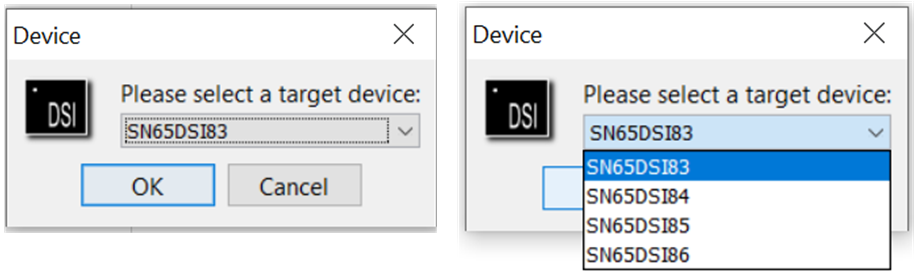

- 打开软件后,选择对应的器件,并点击 OK,如图2所示。

图 6 设备选择

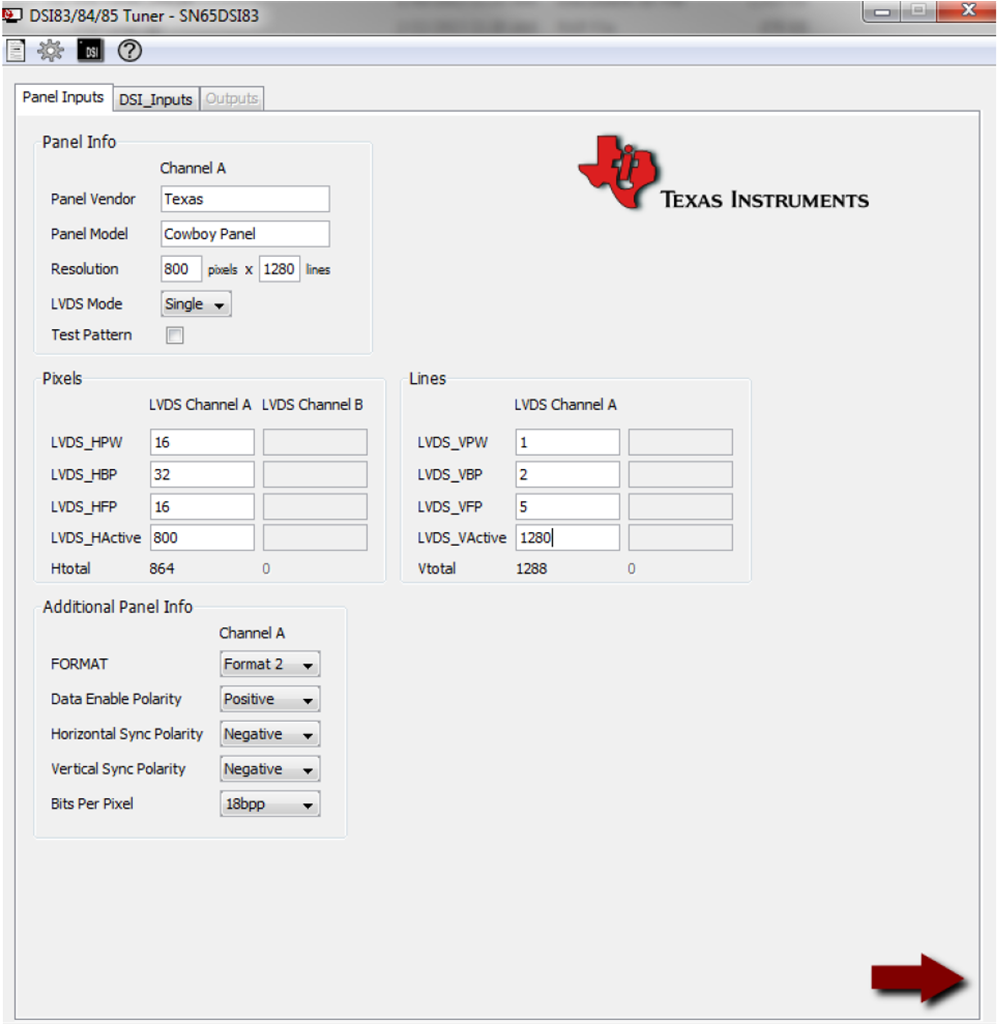

图 6 设备选择 - 输入屏幕信息,如图3所示。

图 7 屏幕信息输入

图 7 屏幕信息输入Panel Vendor& Panel Model: 输入屏幕供应商和屏幕型号。

Resolution:水平像素数×垂直线数。 当输入分辨率后,LVDS_HActive(水平有效像素数)和 LVDS_VActive(垂直有效行数)会自动更新。

LVDS Mode:选择 LVDS 输出为单通道或双通道。 对于 SN65DSI83,仅支持“单通道” LVDS 模式。

Test Pattern:勾选这里会启用测试图案生成功能,仅用于调试。如果不需要发送测试图案,不需要勾选。

- Pixels

and Lines 输入

输入对应的 LVDS 参数,需要根据屏幕的实际情况来填写。这个信息在屏幕的规格书中能够找到。

图 8 LVDS 信息输入

图 8 LVDS 信息输入 - Additional Panel Info

FORMAT(格式):在 Format 1和 Format 2 之间选择。如果选择了RGB666 数据作为 DSI 视频模式,则必须选择 Format 2,如图5。如果从 DSI 接收到的是 RGB888 24 bpp 数据,并且选择了18 bpp 的屏幕,同时 CH*_24BPP_MODE 为 0(默认值),则必须选择 Format 1。关于Format 的详细描述,见参考资料中的 SN65DSI83-Q1 的规格书。

图 9 其他信息输入

图 9 其他信息输入 图 10 6 LVDS Output Data

(Format2); Single-Link 24 bpp

图 10 6 LVDS Output Data

(Format2); Single-Link 24 bpp 图 11 LVDS Output Data

(Format1); Single-Link 24 bpp

图 11 LVDS Output Data

(Format1); Single-Link 24 bppData Enable Polarity(数据使能极性)、Horizontal Sync Polarity(水平同步极性)、Vertical Sync Polarity(垂直同步极性)和 Bits per Pixel(每像素位数)需要根据屏幕要求来选择。

1- 5 输入完成后选择

进行下一步。

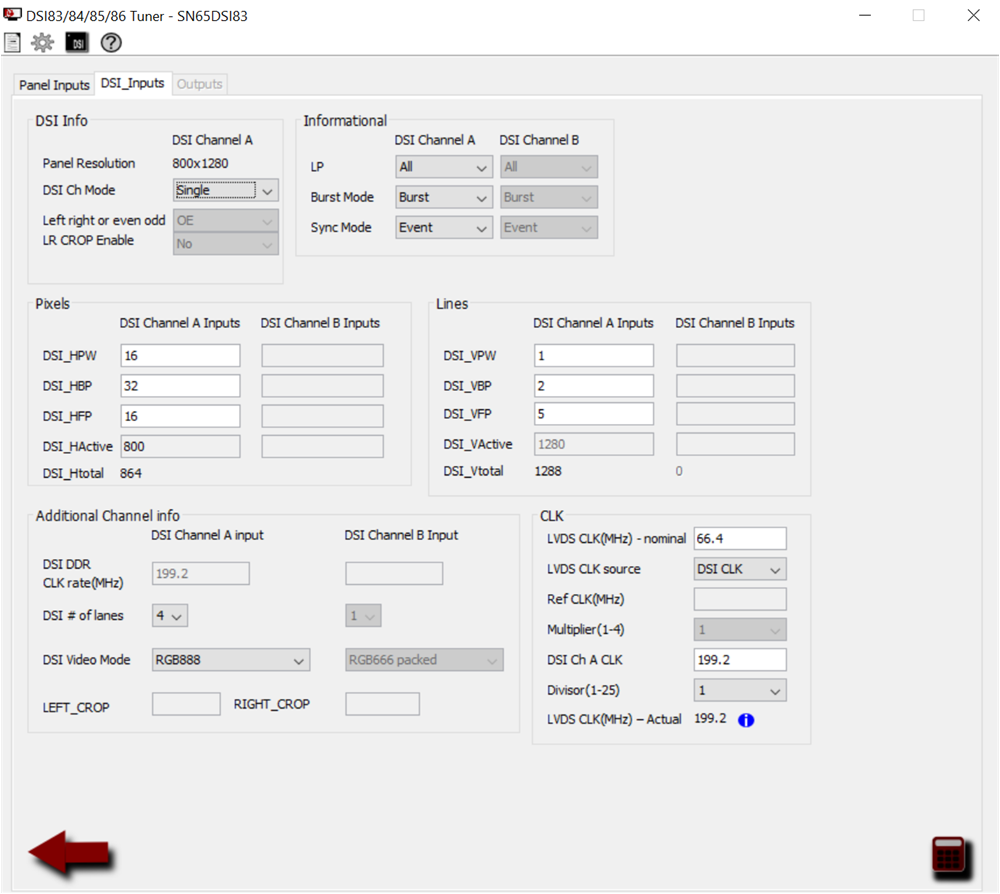

进行下一步。 - DSI 参数输入

所有与 DSI 相关的输入信息都在这个窗口中输入,如DSI Input窗口 所示。

图 12 DSI Input窗口

图 12 DSI Input窗口 - DSI Info输入

- 根据屏幕要求输入窗口中的 LVDS 信息。

- 选择 DSI 通道模式:单通道、双通道或两个单通道。对于SN65DSI83 和 SN65DSI84,只有单通道模式是有效的。

- 选择左右 (LR) 或偶奇 (OE):注意如果 DSI 通道模式不是双通道,将会无法选择。

- 选择是否启用 LR CROP:是或否。通常需要禁用 LR CROP(选择否)。

- Pixels & Lines 输入

如Pixels & Lines输入 所示。

图 13 Pixels &

Lines输入

图 13 Pixels &

Lines输入 - Additional Channel Info

图 14 Additional Channel

Info输入

图 14 Additional Channel

Info输入- DSI DDR CLK rate(CLK)这栏输入 DSI Channel A 的速率,其速率默认等于 CLK 栏中的 DSI CH A CLK 的值(此时 LVDS CLK 输出参考 DSI CLK)。如果 CLK 中选择 Ref CLK(LVDS CLK 参考外部时钟),则 DSI DDR CLK rate(CLK)这栏需要手动写对应的 DSI CLOCK值。

- DSI #of Lanes 选择对应的 DSI 通道数量:1~4。

- DSI Video Mode 选择 DSI 视频模式:RGB666、RGB666 或 RGB888。

- 时钟配置

此栏需输入时钟配置信息。DSI_TUNNR 软件根据非突发模式的选择计算 LVDS 时钟速率(MHz)及建议的最低 DSI 时钟速率。SN65DSI8x 可以配置为使用外部参考时钟或 DSI Ch A CLK 作为 LVDS 时钟源。如时钟配置 所示。

图 15 时钟配置

图 15 时钟配置- 在 “LVDS CLK (MHz)-nominal” 处输入屏幕的 LVDS PCLK。

- 选择 LVDS 时钟源:DSI 时钟或参考时钟。

- 如果选择了参考时钟,需在 “Ref

CLK(MHz)” 栏中输入参考时钟频率,然后选择倍数(1-4): 参考时钟(MHz)× 倍数 = LVDS CLK。如果选择了DSI

时钟,需在 “DSI Ch A CLK” 栏中输入 DSI 通道 A 的时钟频率,然后选择分频(1-25),DSI DDR CLK rate

(MHz) 会根据前面输入的值自动计算出结果。 完成所有信息输入后,点击

确认。

确认。

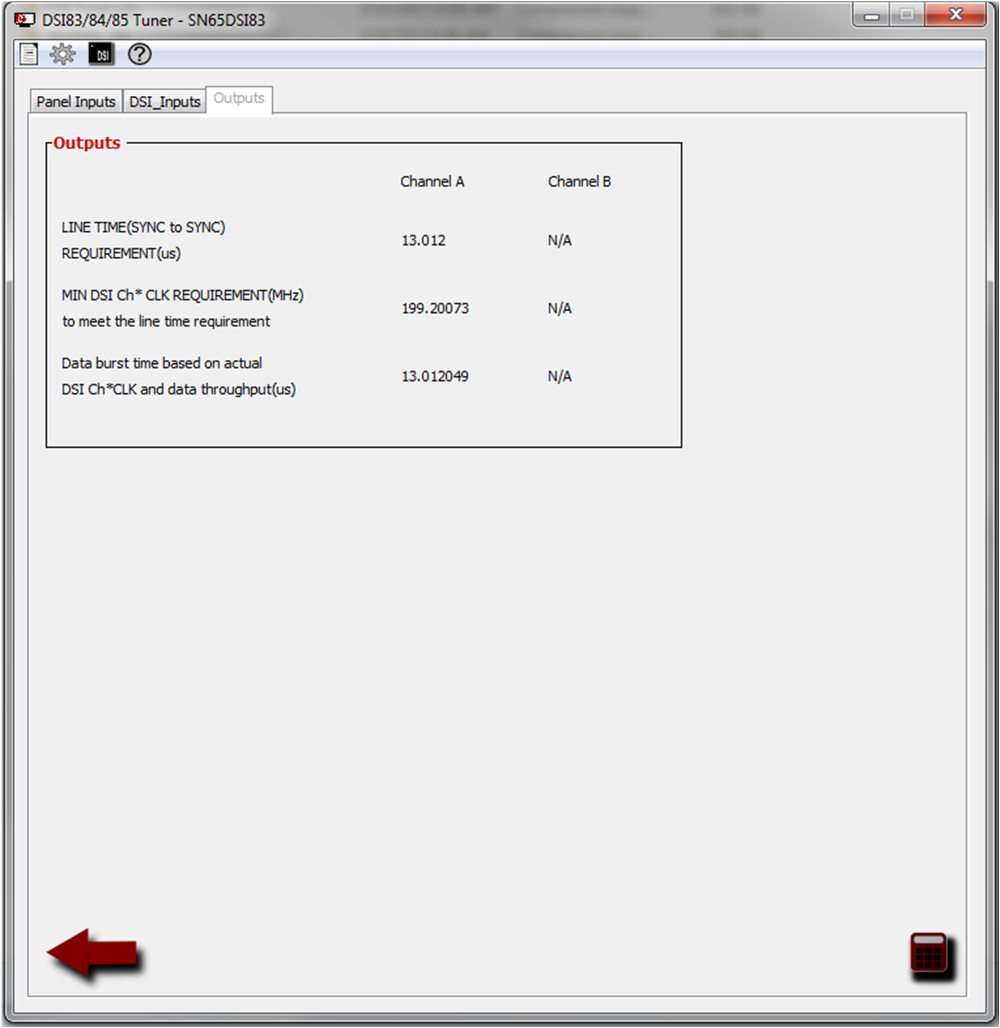

- 输出 Outputs

所有参数都完成输入后,点击计算器图标,将会跳转到输出窗口。输出窗口将输出行时间(从 SYNC 到 SYNC)要求、最小 DSI 通道时钟要求和基于实际 DSI 通道时钟和实际速率的突发时间。这些结果对确保显示器正确配置和时序同步至关重要,如输出窗口 所示。

图 16 输出窗口

图 16 输出窗口- Line Time (SYNC to SYNC)

Requirement (us) 行时间

Line time 代表了DSI 输入端从一个 HSYNC(或 VSYNC)到下一个 HSYNC 行的时间要求。SoC 或者 GPU 等 DSI 信号源必须确保行时间符合本窗口计算出的行时间要求。

- MIN DSI Ch* CLK

REQUIREMENT (MHz) 最小 DSI 通道时钟

最小 DSI 通道时钟需是指在行时间内,采样 DSI 数据所必需的最低 DSI 时钟频率。此值基于 DSI 速率和行时间计算得出。这个值等同于非突发操作模式下应使用的 DSI 时钟速率。

- Data Burst Time 数据突发时间

数据突发速率是根据实际的 DSI DDR CLK 速率和 DSI 数据量计算得出的。如果突发时间小于行时间,则剩余的行时间周期会用空白数据包填充。如果突发时间大于行时间,则需要增加 DSI DDR CLK 速率以满足行时间要求。在非突发操作模式下,数据突发时间通常等于行时间;而在突发模式操作中,它则少于行时间。这种模式下发送 RGB 数据包的时间被压缩,以留出更多的时间用来传送其他的数据。

- Line Time (SYNC to SYNC)

Requirement (us) 行时间

- 完成配置后输出结果

结果计算结束后,在菜单栏选择

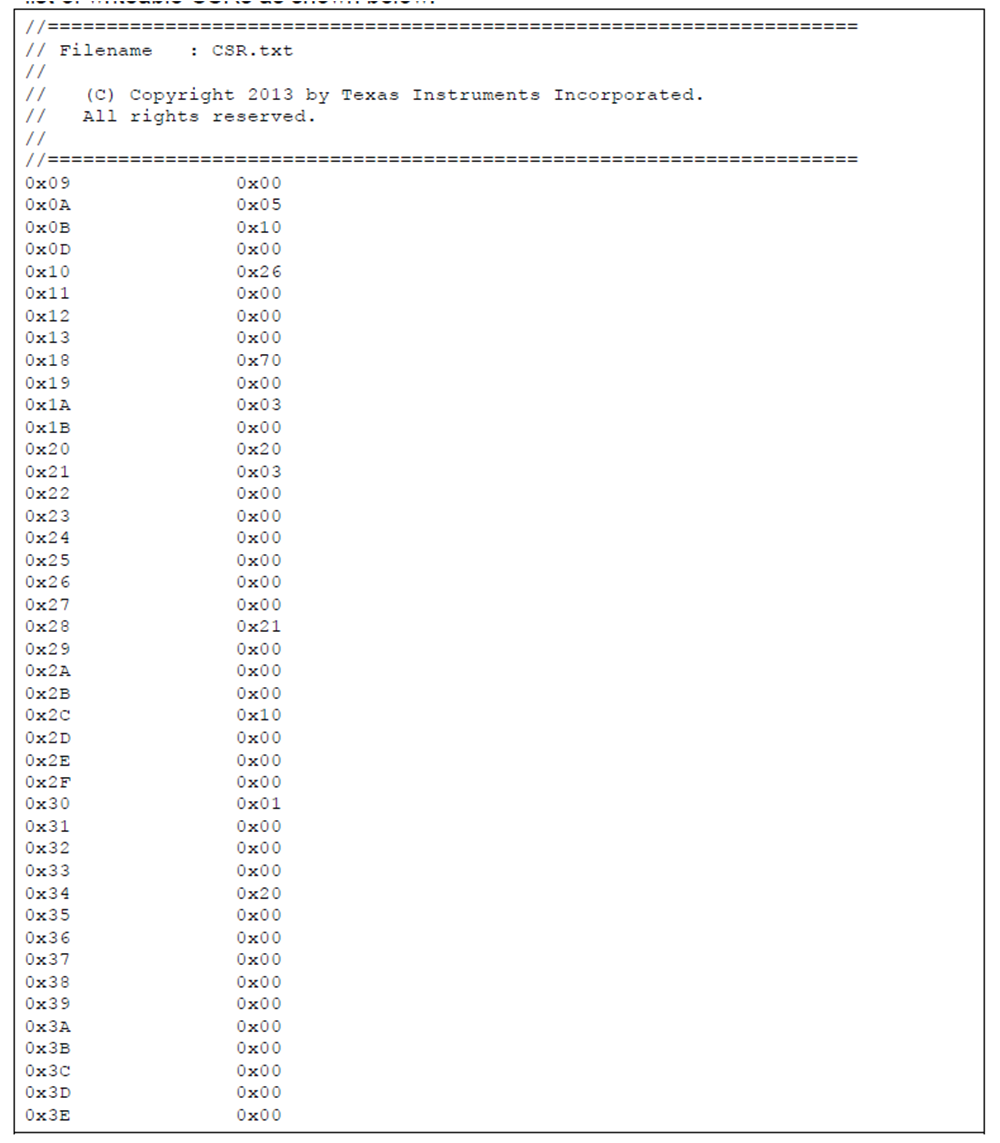

并选择 Generate CSR List 能够看到完整的 Control and Status Registers 列表。

并选择 Generate CSR List 能够看到完整的 Control and Status Registers 列表。 图 17 工具菜单

图 17 工具菜单 图 18 输出窗口

图 18 输出窗口为了方便用户配置,选择对应的

按键可以保持对应的寄存器配置文本。

按键可以保持对应的寄存器配置文本。注意:PLL_EN位和SOFT_RESET位没配置,需要用户按照数据手册中推荐的顺序来设置。

图 19 输出的寄存器文本

图 19 输出的寄存器文本

总结

本文介绍了TI 视频转换芯片 SN65DSI8x 系列选型方法和提供了 DSI Tuner 视频配置工具的相关方法,有助于工程师更高效地设计出更具竞争力的显示产品。