ZHCSHD5A January 2018 – October 2018 ADS112U04

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Multiplexer

- 8.3.2 Low-Noise Programmable Gain Stage

- 8.3.3 Voltage Reference

- 8.3.4 Modulator and Internal Oscillator

- 8.3.5 Digital Filter

- 8.3.6 Conversion Times

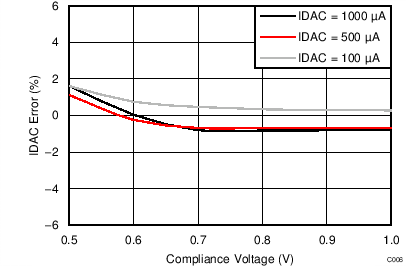

- 8.3.7 Excitation Current Sources

- 8.3.8 Sensor Detection

- 8.3.9 System Monitor

- 8.3.10 Temperature Sensor

- 8.3.11 Offset Calibration

- 8.3.12 Conversion Data Counter

- 8.3.13 Data Integrity

- 8.3.14 General-Purpose Digital Inputs/Outputs

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Map

- 8.6.1 Configuration Registers

- 8.6.2

Register Descriptions

- 8.6.2.1 Configuration Register 0 (address = 00h) [reset = 00h]

- 8.6.2.2 Configuration Register 1 (address = 01h) [reset = 00h]

- 8.6.2.3 Configuration Register 2 (address = 02h) [reset = 00h]

- 8.6.2.4 Configuration Register 3 (address = 03h) [reset = 00h]

- 8.6.2.5 Configuration Register 4 (address = 04h) [reset = 00h]

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

6.8 Typical Characteristics

at TA = 25°C, AVDD = 3.3 V, and AVSS = 0 V using internal VREF = 2.048 V (unless otherwise noted)

| Normal mode, PGA disabled, VIN = 0 V |

| Turbo mode, PGA disabled, VIN = 0 V |

| Normal mode, PGA disabled, VCM = 1.65 V |

Differential Input Voltage

| Turbo mode, PGA disabled, VCM = 1.65 V |

Differential Input Voltage

| PGA enabled, external reference, best fit |

| PGA enabled, gain = 1, 620 samples |

| PGA enabled | ||

| PGA enabled, gain = 1, 620 samples |

| PGA disabled |

| PGA disabled |

| Normal mode |

| Normal mode |

| DVDD = 3.3 V |

| Normal mode |

| Power-down mode |

| Normal mode |

| Normal mode, PGA enabled, VIN = 0 V |

| Turbo mode, PGA enabled, VIN = 0 V |

| Normal mode, PGA enabled, VCM = 1.65 V |

Differential Input Voltage

| Turbo mode, PGA enabled, VCM = 1.65 V |

Differential Input Voltage

| PGA enabled, internal reference, best fit |

| PGA disabled |

| PGA disabled, gain = 1, 620 samples |

| PGA enabled, gain = 128, 620 samples |

| PGA enabled |

| PGA enabled |

| Normal mode | ||

| DVDD = 3.3 V |

| Power-down mode |

| Normal mode |