HD3SS3220 具有超高速 2:1 多路复用器的 USB Type-C DRP 端口控制器

1 特性

- 集成了 2:1 超高速多路复用器的 USB Type-C 端口控制器

- 兼容 USB Type-C™ 规格

- 支持高达 10Gbps 的 USB 3.1 G1 和 G2

- 支持高达 15W 的电力输送与 3A 电流的广播和检测

- 模式配置

- 仅主机 - DFP/供电端

- 仅设备 – UFP/受电端

- 双角色端口 – DRP

- 通道配置 (CC)

- USB 端口连接检测

- 电缆方向检测

- 角色检测

- Type-C 电流模式(默认、中等和高)

- 对于有源电缆的 V(BUS) 检测和 VCONN 支持

- 音频和调试附件支持

- 支持 Try.SRC 和 Try.SNK DRP 模式

- 通过通用输入/输出 (GPIO) 和 I2C 控制配置

- 工作和待机电流消耗都很低

- 工业温度范围:–40°C 至 85°C

3 说明

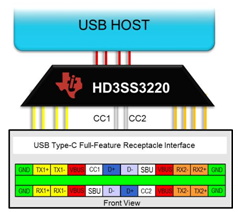

HD3SS3220 是一款具有 USB 超高速 (SS) 2:1 多路复用器的 DRP 端口控制器。该器件为实现 USB Type-C 的生态系统提供通道配置 (CC) 逻辑和 5V VCONN 电源。HD3SS3220 可配置为下行端口 (DFP)、上行端口 (UFP) 或双角色端口 (DRP),因此非常适合任何应用。

根据 Type-C 规范,HD3SS3220 在 DRP 模式下会交替将自身配置为 DFP 或 UFP。CC 逻辑块通过监视 CC1 和 CC2 引脚上的上拉或下拉电阻,以确定何时连接了 USB 端口以及其端口角色。连接 USB 端口后,CC 逻辑还将确定电缆方向并相应地配置 USB SS 多路复用器。最后,CC 逻辑将分别在 DFP 和 UFP 模式下广播或检测 Type-C 电流模式(默认、中等或高)。

集成的多路复用器具有出色的动态特性,可在信号眼图衰减最小的情况下实现转换,并且附加抖动极少。尽管 RX 和 TX 通道的共模电压不同,但是该器件的开关路径会部署自适应共模电压跟踪功能,确保两通道相同。

| 器件型号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| HD3SS3220 | VQFN RNH (30) | 2.50mm x 4.50mm |

| HD3SS3220I |

简化原理图

简化原理图 典型应用

典型应用4 修订历史记录

Date Letter Revision History Changes Intro HTMLC (May 2017)to RevisionD (September 2020)

- 将 VDD 更改为 VDD5。Go

- 在绝对最大额定值 的“控制引脚”行中,DIR 同时位于 VDD5 和 VCC33 中。从 VDD5 中删除了 DIRGo

- 删除了建议运行条件 表中的 C(bus,I2c) Go

- 将当为 I2C 使用 3.3V 时,客户必须始终确保 VDD 高于 3V。修改为当为 I2C 使用 3.3V 时,客户必须始终确保 VDD5 高于 3V。Go

- 更改了时序要求 表的“I2C(SDA、SCL)”部分Go

- 在时序要求 表部分添加了 tENnCC_HI 参数Go

- 在时序要求 表部分添加了 tVDD5V_PG 参数Go

- 在 DFP/供电端 – 下行端口 部分中添加了注释,即 ID 引脚将保持高电平,直到 VBUS 达到 VSafe0VGo

- 将当在 CC1 上检测到处于适当阈值内的电压电平时,DIR 引脚被拉至低电平。修改为当在 CC1 上检测到处于适当阈值内的电压电平时,DIR 引脚为高电平。Go

- 将当在 CC2 上检测到处于适当阈值内的电压电平时,DIR 引脚为高电平。修改为当在 CC2 上检测到处于适当阈值内的电压电平时,DIR 引脚被拉至低电平。Go

- 将HD3SS3220 在 UFP、DFP 和 DRP 模式下支持音频和调试附件。修改为HD3SS3220 在 UFP、DFP 和 DRP 模式下默认支持音频和调试附件Go

- 添加了可通过设置 DISABLE_UFP_ACCESSORY 寄存器来禁用 UFP 附件支持的注释Go

- 添加了有关 VDD5 和 VCC33 上电要求的部分Go

- 删除了电池无电 部分中关于非失效防护引脚的注释,因为此信息位于 VDD5 和 VCC33 上电要求 部分Go

Date Letter Revision History Changes Intro HTMLB (September 2016)to RevisionC (May 2017)

- 添加了 RVBUS 值:MIN = 855,TYP = 887,MAX = 920KΩGo

Date Letter Revision History Changes Intro HTMLA (August 2016)to RevisionB (September 2016)

- 将引脚 CC1 和 CC2 值从“MIN = –0.3 MAX = VDD5 +0.3”更改为“MIN –0.3 MAX = 6”(在绝对最大额定值 中)Go

Date Letter Revision History Changes Intro HTML* (December 2016)to RevisionA (August 2016)