ZHCACZ7A december 2022 – august 2023 TPS25762-Q1 , TPS25772-Q1

4.3.2 突发模式补丁下载过程

以下是详细说明了突发模式下载过程的流程图。

图 4-5 补丁捆绑包更新的流程图 – 突发模式下载

图 4-5 补丁捆绑包更新的流程图 – 突发模式下载图 4-5 展示了突发模式下载的过程。在主机确认器件已进入 PTCH 模式后,主机应实施以下序列来下载补丁捆绑包:

- 主机初始化固件,通过向 DATAx(如果使用 I2C1,则为 0x09;如果使用 I2C2,则为 0x11)寄存器写入 6 个字节的数据,为 PBMx 加载序列做好准备,并确定补丁捆绑包的内容:

- 首先发送 0x06,告诉 PD 控制器写入了一个 6 字节的有效载荷。

- 字节 0 至 3 为补丁捆绑包大小。在图 4-6 中,补丁捆绑包大小为 0x3500 或 13568 字节。字节 4 是要为数据传输分配的 DATAx.SlaveAddress。PD 控制器的 0x00 或器件的 I2C 从器件地址(0x22/0x26 或 0x23/0x27)无效。图 4-6 展示了已选择和使用的随机地址 0x35。

- 字节 5 是突发模式超时值(LSB 为 100ms)。必须使用非零值,并建议始终使用 0x32,这样会提供 5 秒的窗口来完成突发模式补丁更新。

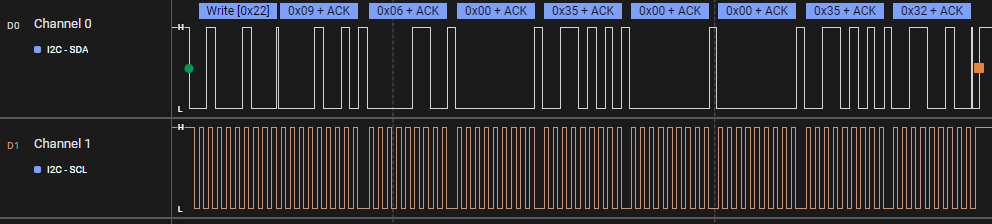

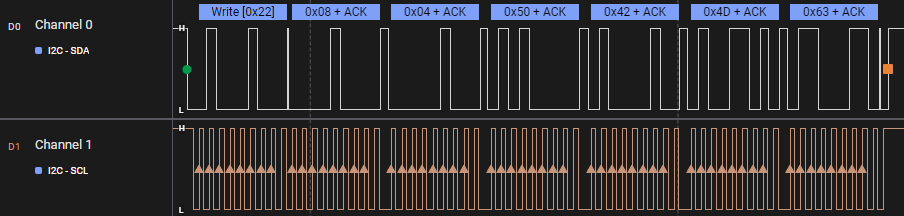

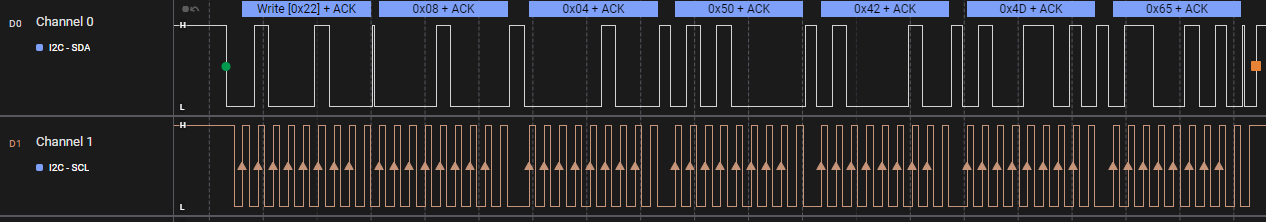

图 4-6 补丁突发模式初始化

图 4-6 补丁突发模式初始化 - 主机应通过向 CMDx(如果使用 I2C1,则为 0x08;如果使用 I2C2,则为 0x10)寄存器发送 4CC ASCII PBMs 任务命令来启动突发模式补丁下载过程。首先发送 0x04,告诉 PD 控制器总共将写入 4 个字节。

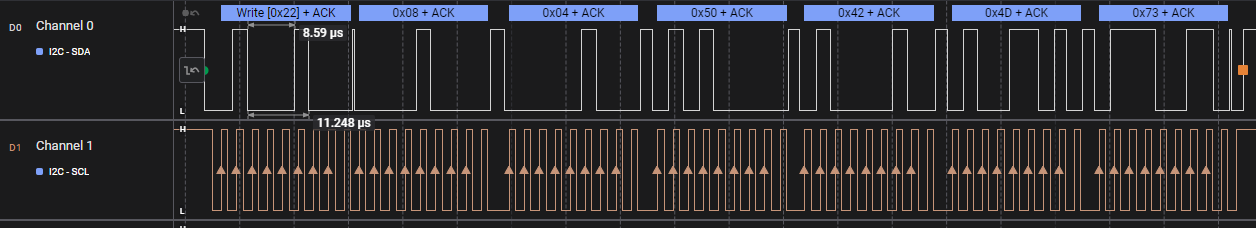

图 4-7 PBMs 任务命令

图 4-7 PBMs 任务命令 - 读取并轮询 CMDx 寄存器,直到字节 1 为 0x00,指示任务处理已完成。

图 4-8 CMDx 输出 - 任务处理已完成

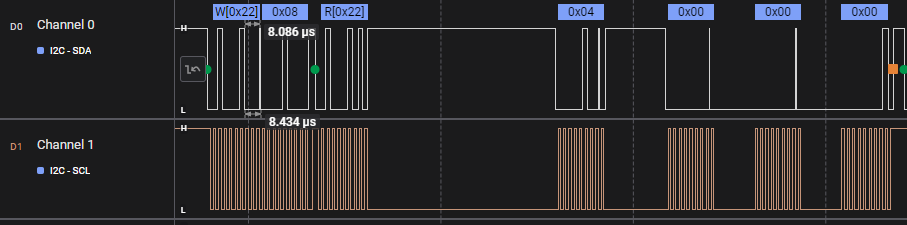

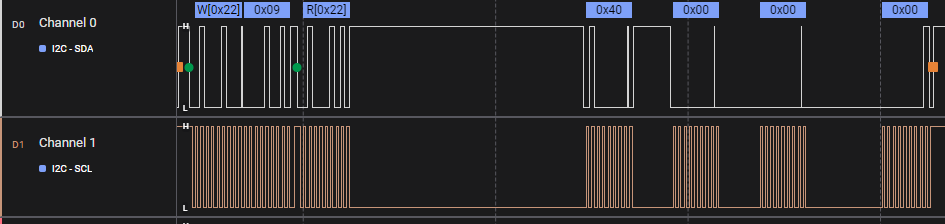

图 4-8 CMDx 输出 - 任务处理已完成 - 读取并轮询 DATAx 寄存器,直至字节 1 为 0x00,指示步骤 1 的补丁初始化成功。

图 4-9 DATAx 输出 - 补丁初始化成功

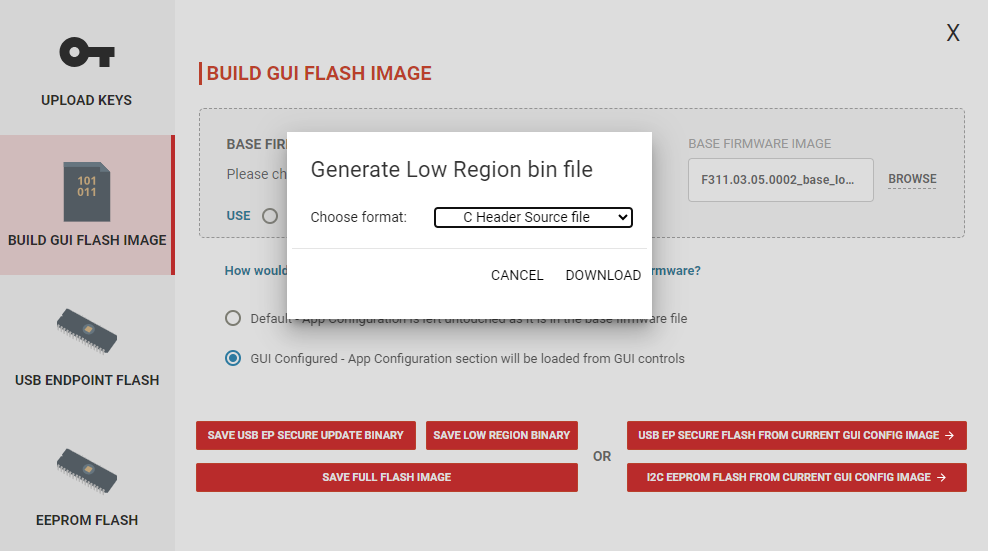

图 4-9 DATAx 输出 - 补丁初始化成功 - 以大小为 256 字节的数据包,将补丁捆绑包数据发送到在步骤 1 中配置的 DATAx.SlaveAddress。可以使用 TPS257XX-Q1-GUI(从 v1.2.0 开始提供)将补丁捆绑包生成为 C 样式数组。从“Build GUI FLASH Image”菜单中选择“SAVE LOW REGION BINARY”。然后选择 C 头文件源文件作为格式,并点击“SAVE”。此文件还将包含补丁捆绑包大小。

图 4-10 将补丁捆绑包生成为 C 数组

图 4-10 将补丁捆绑包生成为 C 数组 - 成功写入补丁捆绑包数据后,等待 500us,然后将 PBMc 任务写入 CMDx 寄存器,以便完成补丁加载序列。在此步骤之后,确保返回来写入到 PD 控制器的原始 I2C 从器件地址。

图 4-11 PBMc 任务命令

图 4-11 PBMc 任务命令 - 读取并轮询 CMDx 寄存器,直到字节 1 为 0x00,指示任务处理已完成。

- 读取并轮询 DATAx 寄存器,直至字节 1 为 0x00,指示器件补丁捆绑包下载成功。I2C 中断(即 GPIO9)将在大约 110ms 后释放。

- 将 PBMe 任务写入 CMDx 寄存器,以便结束补丁加载序列并进入“APP”模式(可选)。

图 4-12 PBMe 任务命令

图 4-12 PBMe 任务命令 - 读取 MODE 寄存器以检查器件是否处于 APP 模式,这表明 PD 控制器收到所有补丁和应用程序配置数据并在应用程序固件中完全正常运行。