ZHCAC56A February 2023 – March 2024 DS90LVRA2 , DS90LVRA2-Q1

数十年来,低电压差分信号 (LVDS) 一直是首选差分信号标准。自 LVDS 问世以来,每当电子系统设计人员需要实现高数据速率、低功耗和噪声容限数据和控制链路时,他们都会考虑使用 LVDS。随着系统设计人员利用新型处理器、FPGA 和 ASSP 技术,实现低功耗和高效 LVDS 链路比以往更加重要。新的处理器技术正在以更小的 CMOS 工艺几何形状开发,这些几何形状的工作核心电压要低得多,因此支持传统 LVDS 接收器 I/O(高达 3.3V)的更高 I/O(输入/输出)电压电平会带来设计挑战。与新型低功耗处理器技术配合使用时,PECL 和 CML 等其他差分 I/O 标准也面临着类似的连接挑战。对于大多数应用来说,增加大型处理器或 FPGA 的总体功率耗散来支持少量数据输入没有意义。

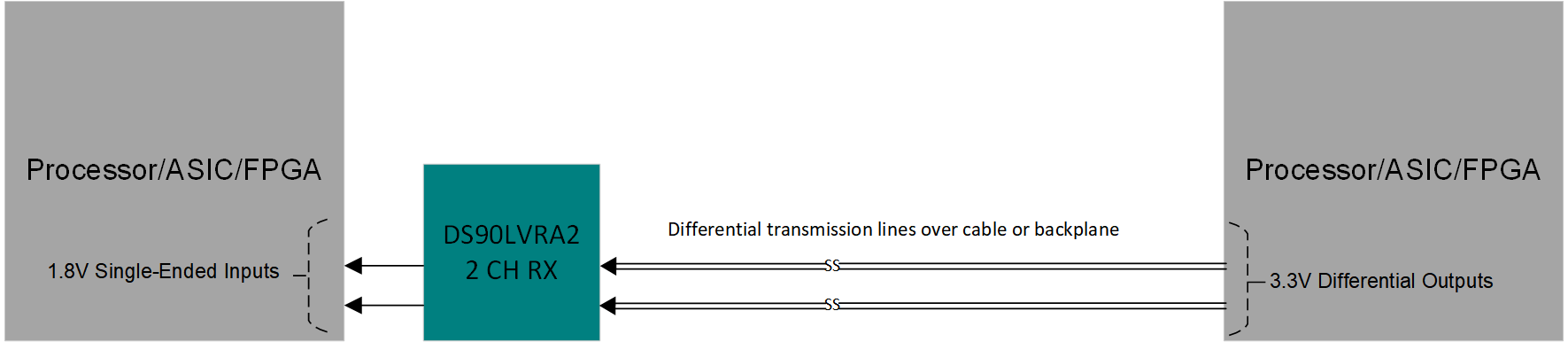

系统设计人员可以使用 TI 的新款 1.8V LVDS 差分接收器将 LVDS 链路轻松集成到他们的设计中,而且不会影响所选处理器的功率或性能。借助 TI 的新款差分信号接收器,系统设计人员可以将 LVDS、LVPECL 和 CML 等差分信号轻松集成到其低功耗处理器的工作电压为 1.8V 的单端输入中(有关示例用例,请参阅图 1)。新型 DS90LVRA2 是一款双通道 LVDS(差分)接收器,支持单端 1.8V CMOS 输出,可轻松与大多数处理器、FPGA 和 ASSP 器件上常见的 1.8V 输入连接。

图 1 DS90LVRA2 用例示例

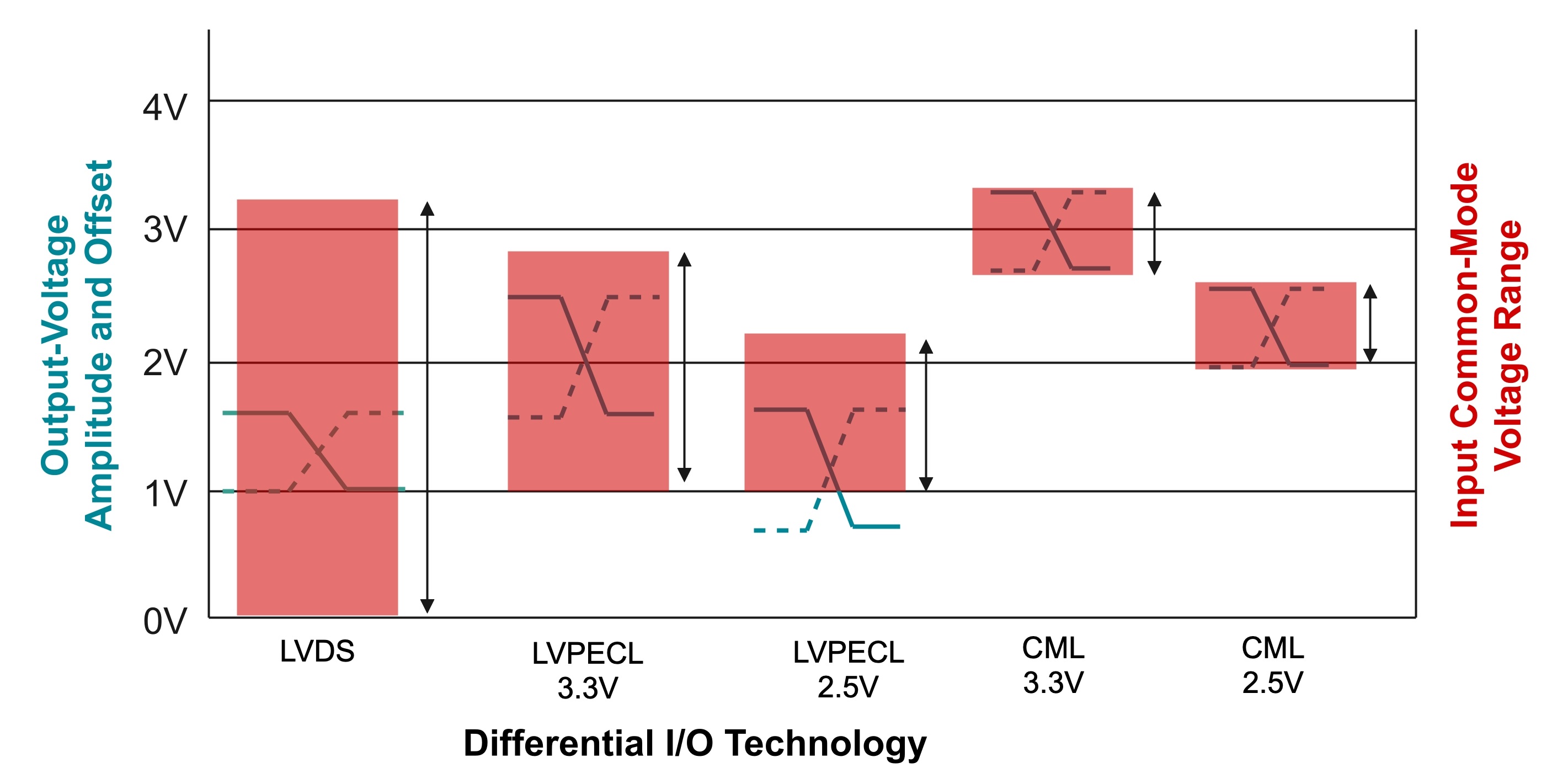

图 1 DS90LVRA2 用例示例DS90LVRA2 支持两个差分输入通道和两个单端 1.8V CMOS 输出通道,每个差分输入的工作速率高达 600Mbps (300MHz)。该器件具有灵活的输入,能够接受 LVDS、LVPECL 或 CML 差分输入(请参阅图 2),需要单电压电源 (1.8V),并采用 8 引脚 WSON 封装,支持直通式引脚排列。LVDS 和 LVPECL 等更高数据速率的差分信号需要正确端接,避免影响信号完整性,因此不建议采用分立式电平转换和转换方法。与分立式电平转换实现相比,使用 DS90LVRA2 可实现出色的信号性能,尤其是在数据速率较高的情况下,放大器和电阻器等分立式器件实际上会降低信号性能,同时还会增加成本和元件数量。有关 DS90LVRA2 的更多信息,请访问 ti.com 上的 DS90LVRA2 器件产品页面。该器件还提供汽车级选项 DS90LVRA2-Q1。

图 2 DS90LVRA2 LVDS、CML 和 LVPECL 支持差分信令标准输入

图 2 DS90LVRA2 LVDS、CML 和 LVPECL 支持差分信令标准输入