SLAZ582V January 2014 – May 2021 MSP430F67661A

- 1Functional Advisories

- 2Preprogrammed Software Advisories

- 3Debug Only Advisories

- 4Fixed by Compiler Advisories

- 5Nomenclature, Package Symbolization, and Revision Identification

-

6Advisory Descriptions

- 6.1 ADC39

- 6.2 ADC42

- 6.3 ADC69

- 6.4 AUXPMM2

- 6.5 BSL7

- 6.6 BSL14

- 6.7 COMP10

- 6.8 CPU21

- 6.9 CPU22

- 6.10 CPU36

- 6.11 CPU37

- 6.12 CPU40

- 6.13 CPU46

- 6.14 CPU47

- 6.15 DMA4

- 6.16 DMA7

- 6.17 DMA9

- 6.18 DMA10

- 6.19 EEM17

- 6.20 EEM19

- 6.21 EEM23

- 6.22 JTAG26

- 6.23 JTAG27

- 6.24 LCDB6

- 6.25 PMM11

- 6.26 PMM12

- 6.27 PMM14

- 6.28 PMM15

- 6.29 PMM18

- 6.30 PMM20

- 6.31 PMM26

- 6.32 PORT15

- 6.33 PORT19

- 6.34 PORT26

- 6.35 SD3

- 6.36 SYS16

- 6.37 UCS11

- 6.38 USCI36

- 6.39 USCI37

- 6.40 USCI41

- 6.41 USCI42

- 6.42 USCI47

- 6.43 USCI50

- 7Revision History

6.28 PMM15

PMM Module

Category

Functional

Function

Device may not wake up from LPM2, LPM3, or LPM4

Description

Device may not wake up from LPM2, LPM3 or LMP4 if an interrupt occurs within 1 us after the entry to the specified LPMx; entry can be caused either by user code or automatically (for example, after a previous ISR is completed). Device can be recovered with an external reset or a power cycle. Additionally, a PUC can also be used to reset the failing condition and bring the device back to normal operation (for example, a PUC caused by the WDT).

This effect is seen when:

- A write to the SVSMHCTL and SVSMLCTL registers is immediately followed by an LPM2, LPM3, LPM4 entry without waiting the requisite settling time ((PMMIFG.SVSMLDLYIFG = 0 and PMMIFG.SVSMHDLYIFG = 0)).

or

The following two conditions are met:

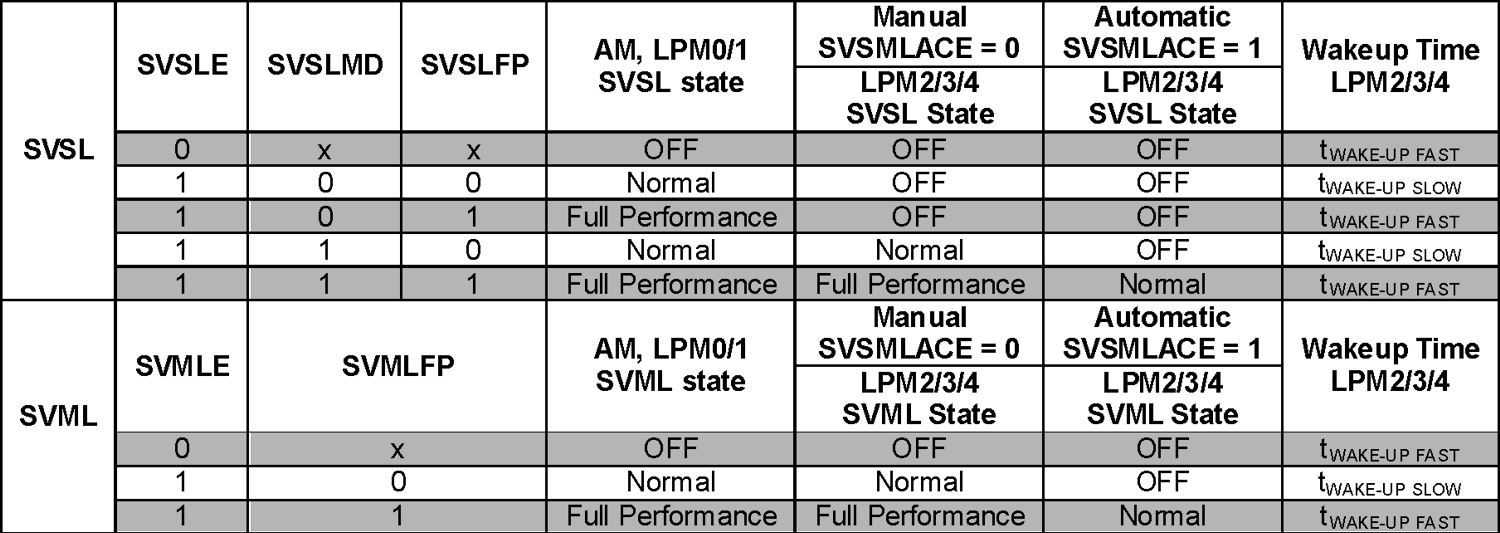

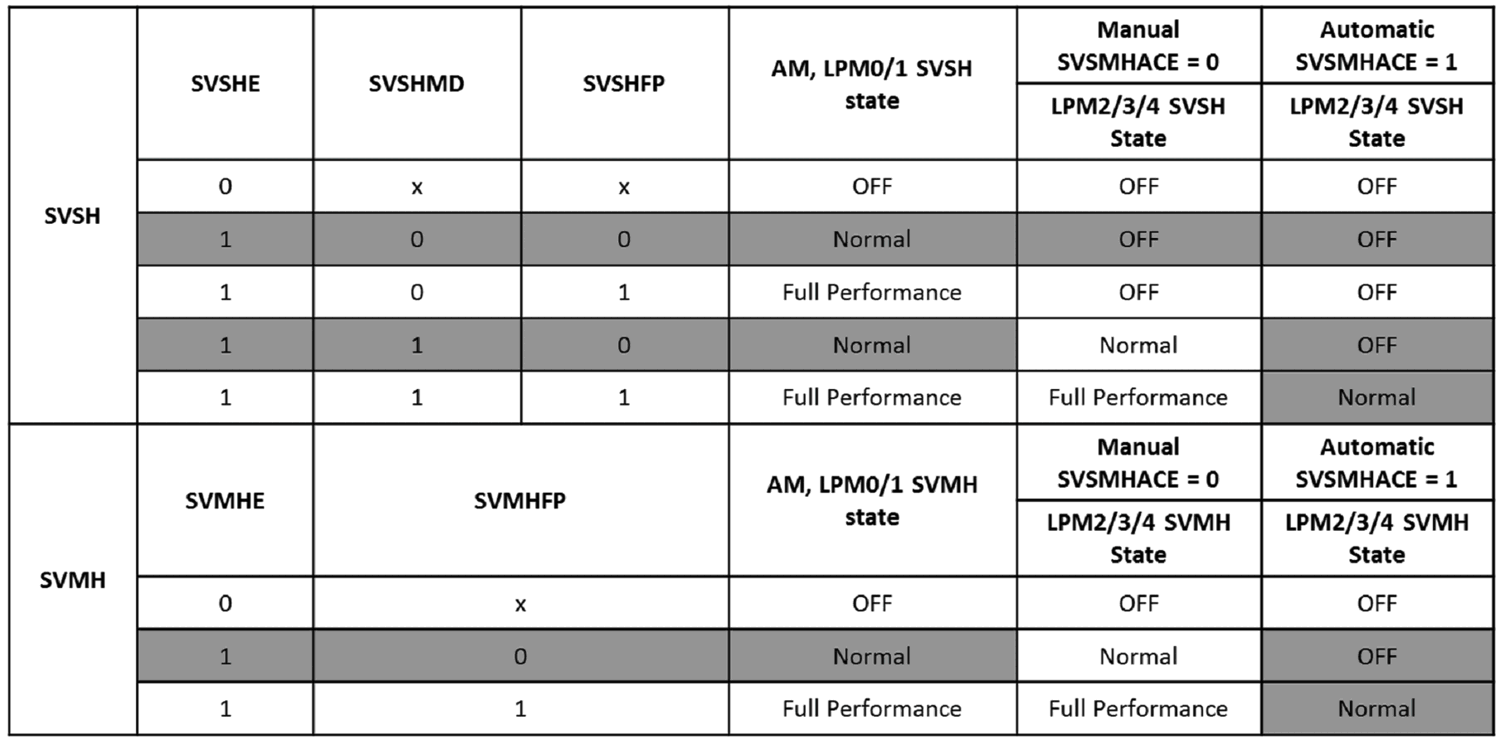

- The SVSL module is configured for a fast wake-up or when the SVSL/SVML module is turned off. The affected SVSMLCTL register settings are shaded in the following table.

and

-The SVSH/SVMH module is configured to transition from Normal mode to an OFF state when moving from Active/LPM0/LPM1 into LPM2/LPM3/LPM4 modes. The affected SVSMHCTL register settings are shaded in the following table.

Workaround

Any write to the SVSMxCTL register must be followed by a settling delay (PMMIFG.SVSMLDLYIFG = 0 and PMMIFG.SVSMHDLYIFG = 0) before entering LPM2, LPM3, LPM4.

and

1. Ensure the SVSx, SVMx are configured to prevent the issue from occurring by the following:

- Configure the SVSL module for slow wake up (SVSLFP = 0). Note that this will increase the wakeup time from LPM2/3/4 to twakeupslow (~150 us).

or

- Do not configure the SVSH/SVMH such that the modules transition from Normal mode to an OFF state on LPM entry and ensure SVSH/SVMH is in manual mode. Instead force the modules to remain ON even in LPMx. Note that this will cause increased power consumption when in LPMx.

Refer to the MSP430 Driver Library(MSPDRIVERLIB) for proper PMM configuration functions.

Use the following function, PMM15Check (void), to determine whether or not the existing PMM configuration is affected by the erratum. The return value of the function is 1 if the configuration is affected, and 0 if the configuration is not affected.

unsigned char PMM15Check (void)

{

// First check if SVSL/SVML is configured for fast wake-up

if ( (!(SVSMLCTL & SVSLE)) || ((SVSMLCTL & SVSLE) && (SVSMLCTL & SVSLFP)) ||

(!(SVSMLCTL & SVMLE)) || ((SVSMLCTL & SVMLE) && (SVSMLCTL & SVMLFP)) )

{ // Next Check SVSH/SVMH settings to see if settings are affected by PMM15

if ((SVSMHCTL & SVSHE) && (!(SVSMHCTL & SVSHFP)))

{

if ( (!(SVSMHCTL & SVSHMD)) || ((SVSMHCTL & SVSHMD) &&

(SVSMHCTL & SVSMHACE)) )

return 1; // SVSH affected configurations

}

if ((SVSMHCTL & SVMHE) && (!(SVSMHCTL & SVMHFP)) && (SVSMHCTL & SVSMHACE))

return 1; // SVMH affected configurations

}

return 0; // SVS/M settings not affected by PMM15

}

}

2. If fast servicing of interrupts is required, add a 150us delay either in the interrupt service routine or before entry into LPM3/LPM4.