KOKT165 August 2025 UCC24624

고주파 공진 컨버터 설계 고려 사항에는 부품 선택, 기생 매개 변수를 사용한 설계, 동기 정류기 설계 및 전압 게인 설계가 포함됩니다. 이 전원 팁에서는 스위칭 부품 선택에 영향을 미치는 주요 매개 변수와 고주파 공진 컨버터에서 변압기 권선 내 커패시턴스의 영향에 대해 중점적으로 다룹니다.

지난 10년 동안 WBG(넓은 밴드갭) 장치가 상용화되어 더 높은 전력 밀도를 위해 훨씬 더 높은 주파수에서 전력 컨버터를 작동할 수 있게 되었습니다. 고성능 전원 공급 장치에는 특히 실리콘 카바이드 및 질화 갈륨 FET(전계 효과 트랜지스터)와 같은 WBG 장치가 이제 막 포함되기 시작했습니다. 이는 이 장치들이 가진 출력 커패시턴스(Coss), 게이트 전하(Qg), 온 저항(RDS(on)) 및 역복구 전하(Qrr) 특성 때문이며, 모두 동일한 항복 전압 수준에서 실리콘 또는 실리콘 초접합 FET보다 수치가 더 낮거나 존재하지 않습니다. Qg가 더 낮아 필요한 구동 전력이 감소하며(Pdrive = Vdrive Qg Fsw), RDS(on)이 더 낮아 전도 손실이 줄어듭니다. 여기서 Vdrive는 구동 전압이고 Fsw는 FET 스위칭 주파수입니다. Qg 및 RDS(on)뿐만 아니라 고주파 컨버터를 선택할 때는 Coss 및 Qrr을 고려하는 것도 중요합니다.

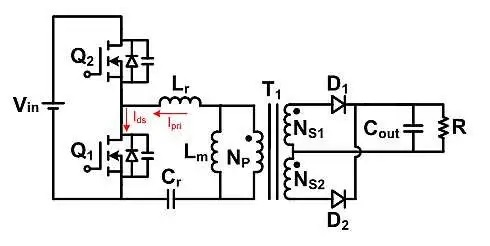

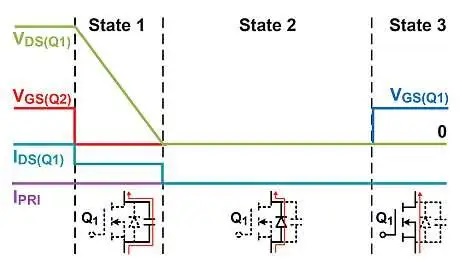

그림 1에 표시된 LLC-SRC(인덕터-인덕터-커패시터 직렬 공진 컨버터) 등의 공진 컨버터에서는 ZVS(제로 전압 스위칭)를 달성하기 위해 공진 탱크의 전류가 FET(그림 2의 상태 1)의 Coss를 충전/방전합니다. ZVS는 게이트 전압이 하이로 상승하기 전에 FET 드레인-소스 전압(VDS)이 제로에 도달하는 것을 말합니다. 따라서 Coss가 더 낮으면 동일한 공진 탱크 전류 수준에서 ZVS 도달을 위한 데드 타임이 더 짧아집니다. 데드 타임이 짧으면 듀티 사이클이 더 크고 1차측 공진 탱크 및 FET의 RMS(평균 제곱근) 전류가 더 낮습니다. 즉, 효율이 더 높고 더 높은 스위칭 주파수에서 컨버터를 작동할 수 있습니다.

그림 1 LLC-SRC

그림 1 LLC-SRCZVS를 달성하기 위해 FET의 바디 다이오드가 전류를 전도하는 기간이 항상 있으며, 그림 2에 표시된 상태 2에 해당합니다. FET에 Qrr이 있고 바디 다이오드가 계속해서 전류를 전도할 때 다시 켜지는 경우 FET 자체에서 역방향 전류를 생성하여 Qrr을 방전하고 하드 스위칭 및 고전압 응력을 유발함으로써 FET가 손상될 가능성이 있습니다.

그림 2 LLC-SRC의 스위칭 전환

그림 2 LLC-SRC의 스위칭 전환그림 3에서는 그림 1에 표시된 것처럼 LLC-SRC의 시동 프로세스 동안 발생하는 이러한 하드 스위칭 현상을 보여줍니다. FET Q2가 먼저 전류를 전도하고 인덕터 전류 IPRI가 형성됩니다. 그런 다음, 전류 IPRI가 FET Q1 채널 및 바디 다이오드를 통해 전도됩니다. 전류가 역방향으로 흐르지 않도록 하면서 FET Q2가 다시 켜집니다. Qrr의 영향으로 인해 FET Q1이 역방향 전류를 자체적으로 생성하여 Qrr을 방전시킵니다. 이로 인해 고전압 응력이 발생합니다.

그림 3 Qrr으로 인한 하드 스위칭

그림 3 Qrr으로 인한 하드 스위칭고주파 공진 컨버터에서는 공진 탱크 임피던스가 일반적으로 저주파 공진 컨버터보다 훨씬 더 낮습니다. 따라서 고주파 공진 컨버터의 시동 돌입 전류가 더 높을 것으로 예상됩니다. 그림 1의 LLC-SRC를 예로 사용하면, 출력 전압이 제로(시동 시 초기 상태)인 경우 Q2가 먼저 전도되는 시동 전류를 제한하는 유일한 임피던스는 Lr(LLC-SRC의 직렬 공진 인덕터)입니다. 특히 버스 컨버터와 같은 고효율 및 고주파 공진 컨버터 설계에서는 효율을 높이기 위해 일반적으로 Lr을 최소화합니다. Lr 값이 작으면 동일한 시동 주파수에서 시동 전류가 더 높아지므로 Qrr 관련 하드 스위칭에 더 취약해집니다. 따라서 고주파 공진 컨버터에서는 낮은 Qrr FET를 사용하는 것이 필수적입니다.

앞서 언급한 WBG 장치의 장점을 활용하면 메가헤르츠 범위에서 절연 공진 컨버터를 작동할 수 있으며, 이는 기존 절연 전원 공급 장치보다 5~10배 더 빠릅니다. 이 "더 높은 주파수" 영역에서는 이전에는 컨버터 설계 프로세스에서 "무시할 수 있는" 수준으로 간주되던 많은 매개 변수를 더 이상 무시할 수 없습니다(예: 변압기 권선 내 커패시터).

기존 공진 컨버터 설계 프로세스에서 설계자는 ZVS를 달성하기 위해 Coss가 공진 탱크에 저장된 에너지를 전부 소모할 수 있도록 공진 탱크에 저장된 에너지가 FET Coss에 저장된 에너지보다 더 높도록 해야 합니다. 그림 1에 표시된 LLC-SRC를 예로 사용하면, 방정식 1에서 이 부등성의 유효성이 보장됩니다.

여기서 ILm은 자화 인덕터 Lm의 피크 전류이고 Vin은 LLC-SRC의 입력 전압입니다. 방정식 1은 Lm에 대한 인덕터에 옴의 법칙을 적용하여 방정식 2로 고칠 수 있습니다.

여기서 n = Np:Ns1(Ns1을 Ns2라고 가정)은 변압기 권선 비율이고 Vout은 출력 전압입니다.

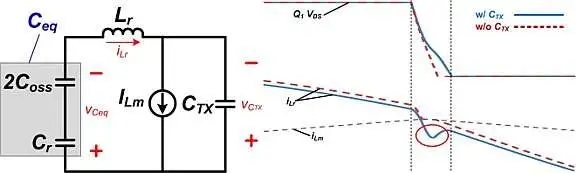

공진 컨버터 설계에서 넓은 작동 범위 및 홀드업 시간을 처리해야 하는 경우 Ln = Lm/Lr을 낮게 유지하기 위해(폐쇄형 루프 LLC-SRC 설계에서 4~10의 Ln 값 적용) Lm은 일반적으로 방정식 2 우변의 값보다 훨씬 더 작습니다. 버스 컨버터 등의 공진 컨버터 설계에서 높은 컨버터 효율이 필요한 경우에는 Lm을 최대화하면 더 낮은 전도 손실을 위해 1차측 RMS 전류가 줄어듭니다. 이 경우 Lm 값은 방정식 2 우변의 값에 가까워집니다. 하지만 방정식 2는 이상적인 변압기를 사용한 이상적인 상태를 나타낼 뿐입니다. 실제 변압기에서는 많은 매개 변수가 Coss 충전 및 방전 성능에 영향을 미칠 수 있습니다. 가장 중요한 매개 변수는 권선 내 커패시턴스입니다.

그림 4에서는 LLC-SRC 스위칭 과도 중의 간소화된 회로 모델을 보여줍니다. 여기서 Lm(ILm)의 전류는 Ceq(공진 커패시터 Cr과 직렬로 연결된 FET 2개의 Coss)를 방전시킵니다(Cr을 전압 소스라고 가정함). 변압기 권선 내 커패시턴스(CTX)가 없으면 모든 ILm이 Ceq로 이동하며 방정식 2는 유효합니다. 그러나 CTX가 있으면 변압기 권선 극성을 바꾸기 위해 일부 ILm이 CTX로 이동해야 하며, 이로 인해 Coss 방전 성능이 줄고 ZVS 미달성 가능성이 생깁니다. 따라서 1차측 권선 계층을 각 계층과 이격하고 2차측 권선 계층과도 이격하여 CTX를 낮게 유지하는 것이 필수적입니다.

그림 4 변압기 권선 내 커패시터의 효과

그림 4 변압기 권선 내 커패시터의 효과경험에 근거한 Lm 값을 결정하는 방법은 방정식 2를 사용하여 계산된 최대 Lm 값의 절반만 사용하는 것입니다. 이는 일반적으로 실제로 변압기를 만들기 전에 CTX 값을 예측하는 것이 어렵기 때문입니다. CTX는 일반적으로 400V 입력의 컨버터에서 22pF~100pF의 범위에 속합니다. 또한 변압기 구조가 정해진 후에는 마진을 두고 충분히 낮은 Lm을 보장하기 위해 회로 시뮬레이션에서 CTX를 모델링하는 것이 큰 도움이 됩니다.

시리즈의 다음 회에서는 고주파 공진 컨버터 설계에서의 동기 정류기 설계 과제에 대해 중점적으로 다룹니다.

관련 문서:

- Power Tips #84: Think outside the LLC series resonant converter box

- MOSFET Qrr: Ignore at your peril in the pursuit of power efficiency

- 하프 브리지 공진 LLC 컨버터 및 1차측 MOSFET 선택 시 설계 고려 사항

- 많은 유사 공진과 공진 컨버터 사용

이전에 EDN.com에 게시되었습니다.