SLUSBE8B May 2013 – September 2015 UCC28720

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1 Stand-by Power Estimate

- 8.2.2.2 Input Bulk Capacitance and Minimum Bulk Voltage

- 8.2.2.3 Transformer Turns Ratio, Inductance, Primary-Peak Current

- 8.2.2.4 Transformer Parameter Verification

- 8.2.2.5 Output Capacitance

- 8.2.2.6 VDD Capacitance, CDD

- 8.2.2.7 VS Resistor Divider, Line Compensation, and Cable Compensation

- 8.2.3 Application Curves

- 9 Power Supply Recommendations

- 10Layout

-

11Device and Documentation Support

- 11.1

Device Support

- 11.1.1

Device Nomenclature

- 11.1.1.1

Definition of Terms

- 11.1.1.1.1 Capacitance Terms in Farads

- 11.1.1.1.2 Duty Cycle Terms

- 11.1.1.1.3 Frequency Terms in Hertz

- 11.1.1.1.4 Current Terms in Amperes

- 11.1.1.1.5 Current and Voltage Scaling Terms

- 11.1.1.1.6 Transformer Terms

- 11.1.1.1.7 Power Terms in Watts

- 11.1.1.1.8 Resistance Terms in Ω

- 11.1.1.1.9 Timing Terms in Seconds

- 11.1.1.1.10 Voltage Terms in Volts

- 11.1.1.1.11 AC Voltage Terms in VRMS

- 11.1.1.1.12 Efficiency Terms

- 11.1.1.1

Definition of Terms

- 11.1.1

Device Nomenclature

- 11.2 Documentation Support

- 11.3 Community Resources

- 11.4 Trademarks

- 11.5 Electrostatic Discharge Caution

- 11.6 Glossary

- 11.1

Device Support

- 12Mechanical, Packaging, and Orderable Information

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

The UCC28720 flyback power supply controller provides constant voltage (CV) and constant current (CC) output regulation to help meet USB-compliant adaptors and charger requirements. This device uses the information obtained from auxiliary winding sensing (VS) to control the output voltage and does not require optocoupler/TL431 feedback circuitry. Not requiring optocoupler feedback reduces the component count and makes the design more cost effective and efficient.

8.2 Typical Application

Figure 20. Design Procedure Application Example

Figure 20. Design Procedure Application Example

8.2.1 Design Requirements

The design parameters are listed in Table 1.

Table 1. Design Parameters

| PARAMETER | TEST CONDITIONS | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|---|

| INPUT CHARACTERISTICS | ||||||

| VIN | RMS Input Voltage | 100 (VIN(MIN)) | 115/230 | 240 | V | |

| fLINE | Line Frequency | 47 | 50/60 | 64 | Hz | |

| PSB_CONV | No Load Input Power | VIN = Nom, IOUT = 0 A | 10 | mW | ||

| VIN(RUN) | Brownout Voltage | IOUT = Nom | 70 | V | ||

| OUTPUT CHARACTERISTICS | ||||||

| VOCV | Output Voltage | VIN = Nom, IOUT = NOM | 4.75 | 5 | 5.25 | V |

| VRIPPLE | Output Voltage Ripple | VIN = Nom, IO = Max | 0.1 | V | ||

| IOUT | Output Current | VIN = Min to Max | 1 | 1.05 | A | |

| Output OVP | IOUT = Min to Max | 5.75 | V | |||

| Transient Response | ||||||

| Load Step (ITRAN = 0.6 A) | (0.1 to 0.6 A) or (0.6 to 0.1 A)

VOΔ= 0.9 V for Calculations |

4.1 | 5 | 5 | V | |

| SYSTEMS CHARACTERISTICS | ||||||

| fMAX | Switching Frequency | 70 | kHz | |||

| ƞ | Full Load Efficiency (115/230 V RMS input) | IOUT = 1 A | 74% | |||

8.2.2 Detailed Design Procedure

This procedure outlines the steps to design a constant-voltage, constant-current flyback converter using the UCC28720 controller. Refer to the Figure 20 for component names and network locations. The design procedure equations use terms that are defined below.

8.2.2.1 Stand-by Power Estimate

Assuming no-load stand-by power is a critical design parameter, determine estimated no-load power based on target converter maximum switching frequency and output power rating.

The following equation estimates the stand-by power of the converter.

For a typical USB charger application, the bias power during no-load is approximately 2.5 mW. This is based on 25-V VDD and 100-µA bias current. The output preload resistor can be estimated by VOCV and the difference in the converter stand-by power and the bias power. The equation for output preload resistance accounts for bias power estimated at 2.5 mW.

The capacitor bulk voltage for the loss estimation is the highest voltage for the stand-by power measurement, typically 325 VDC.

For the total stand-by power estimation add an estimated 2.5 mW for snubber loss to the converter stand-by power loss.

8.2.2.2 Input Bulk Capacitance and Minimum Bulk Voltage

Determine the minimum voltage on the input capacitance, CB1 and CB2 total, in order to determine the maximum Np to Ns turns ratio of the transformer. The input power of the converter based on target full-load efficiency, minimum input RMS voltage, and minimum AC input frequency are used to determine the input capacitance requirement.

Maximum input power is determined based on VOCV, IOCC, and the full-load efficiency target.

The below equation provides an accurate solution for input capacitance based on a target minimum bulk capacitor voltage. To target a given input capacitance value, iterate the minimum capacitor voltage to achieve the target capacitance.

8.2.2.3 Transformer Turns Ratio, Inductance, Primary-Peak Current

The maximum primary-to-secondary turns ratio can be determined by the target maximum switching frequency at full load, the minimum input capacitor bulk voltage, and the estimated DCM quasi-resonant time.

Initially determine the maximum available total duty cycle of the on time and secondary conduction time based on target switching frequency and DCM resonant time. For DCM resonant time, assume 500 kHz if you do not have an estimate from previous designs. For the transition mode operation limit, the period required from the end of secondary current conduction to the first valley of the VCE voltage is ½ of the DCM resonant period, or 1 µs assuming 500-kHz resonant frequency. DMAX can be determined using the equation below.

Once DMAX is known, the maximum turns ratio of the primary to secondary can be determined with the equation below. DMAGCC is defined as the secondary diode conduction duty cycle during constant-current, CC, operation. It is set internally by the UCC28720 at 0.425. The total voltage on the secondary winding needs to be determined; which is the sum of VOCV, the secondary rectifier VF, and the cable compensation voltage (VOCBC). For the 5-V USB charger applications, a turns ratio range of 13 to 15 is typically used.

Once an optimum turns ratio is determined from a detailed transformer design, use this ratio for the following parameters.

The UCC28720 constant-current regulation is achieved by maintaining a maximum DMAG duty cycle of 0.425 at the maximum primary current setting. The transformer turns ratio and constant-current regulating voltage determine the current sense resistor for a target constant current.

Since not all of the energy stored in the transformer is transferred to the secondary, a transformer efficiency term is included. This efficiency number includes the core and winding losses, leakage inductance ratio, and bias power ratio to rated output power. For a 5-V, 1-A charger example, bias power of 1.5% is a good estimate. An overall transformer efficiency of 0.9 is a good estimate to include 3.5% leakage inductance, 5% core and winding loss, and 1.5% bias power.

The primary transformer inductance can be calculated using the standard energy storage equation for flyback transformers. Primary current, maximum switching frequency and output and transformer power losses are included in the equation below. Initially determine transformer primary current.

Primary current is simply the maximum current sense threshold divided by the current sense resistance.

The secondary winding to auxiliary winding transformer turns ratio (NAS) is determined by the lowest target operating output voltage in constant-current regulation and the VDD UVLO of the UCC28720. There is additional energy supplied to VDD from the transformer leakage inductance energy which allows a lower turns ratio to be used in many designs.

8.2.2.4 Transformer Parameter Verification

The transformer turns ratio selected affects the transistor VC and secondary rectifier reverse voltage so these should be reviewed. The UCC28720 does require a minimum on time of the transistor (tON) and minimum DMAG time (tDMAG) of the secondary rectifier in the high line, minimum load condition. The selection of fMAX, LP and RCS affects the minimum tON and tDMAG.

The secondary rectifier and transistor voltage stress can be determined by the equations below.

For the transistor VC voltage stress, an estimated leakage inductance voltage spike (VLK) needs to be included.

Equation 20 and Equation 21 are used to determine if the minimum tON target of 300 ns and minimum tDMAG target of 1.2 µs is achieved.

8.2.2.5 Output Capacitance

The output capacitance value is typically determined by the transient response requirement from no-load. For example, in some USB charger applications there is a requirement to maintain a minimum VO of 4.1 V with a load-step transient of 0 mA to 500 mA . The equation below assumes that the switching frequency can be at the UCC28720 minimum of fSW(min).

Another consideration of the output capacitor(s) is the ripple voltage requirement which is reviewed based on secondary peak current and ESR. A margin of 20% is added to the capacitor ESR requirement in the equation below.

8.2.2.6 VDD Capacitance, CDD

The capacitance on VDD needs to supply the device operating current until the output of the converter reaches the target minimum operating voltage in constant-current regulation. At this time the auxiliary winding can sustain the voltage to the UCC28720. The total output current available to the load and to charge the output capacitors is the constant-current regulation target. The equation below assumes the output current of the flyback is available to charge the output capacitance until the minimum output voltage is achieved. There is 1 V of margin added to VDD in the calculation.

8.2.2.7 VS Resistor Divider, Line Compensation, and Cable Compensation

The VS divider resistors determine the output voltage regulation point of the flyback converter, also the high-side divider resistor (RS1) determines the line voltage at which the controller enables continuous DRV operation. RS1 is initially determined based on transformer auxiliary to primary turns ratio and desired input voltage operating threshold.

The low-side VS pin resistor is selected based on desired VO regulation voltage.

The UCC28720 can maintain tight constant-current regulation over input line by utilizing the line compensation feature. The line compensation resistor (RLC) value is determined by current flowing in RS1 and expected base drive and transistor turn-off delay. Assume a 50-ns internal delay in the UCC28720.

The UCC28720 has adjustable cable drop compensation. The resistance for the desired compensation level at the output terminals can be determined using Equation 28.

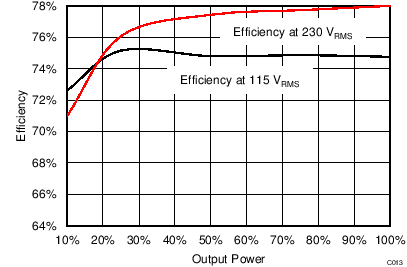

8.2.3 Application Curves

Figure 21. Efficiency

Figure 21. Efficiency

Figure 23. Output at Start-up 115-V RMS, 5-Ω Load

Figure 23. Output at Start-up 115-V RMS, 5-Ω Load

Figure 25. Output at Start-up 230-V RMS, 5-Ω Load

Figure 25. Output at Start-up 230-V RMS, 5-Ω Load

NOTE:

CH4 = VOCV with 5-V offset, CH1 = IOUT Figure 22. Output at Start-up 115-V RMS, No Load

Figure 22. Output at Start-up 115-V RMS, No Load

Figure 24. Output at Start-up 230-V RMS, No Load

Figure 24. Output at Start-up 230-V RMS, No Load

NOTE:

CH4 = VOCV with 5-V offset, CH1 = IOUT

NOTE:

Ch2 = VOCV at the end of 3M cable and 1 µF of capacitance.The output ripple at the end of the cables is less than 50 mV.