SGLS245E May 2020 – May 2020 UCC2813-0-Q1 , UCC2813-1-Q1 , UCC2813-2-Q1 , UCC2813-3-Q1 , UCC2813-4-Q1 , UCC2813-5-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Detailed Pin Descriptions

- 8.3.2 Undervoltage Lockout (UVLO)

- 8.3.3 Self-Biasing, Active Low Output

- 8.3.4 Reference Voltage

- 8.3.5 Oscillator

- 8.3.6 Synchronization

- 8.3.7 PWM Generator

- 8.3.8 Minimum Off-Time Adjustment (Dead-Time Control)

- 8.3.9 Leading Edge Blanking

- 8.3.10 Minimum Pulse Width

- 8.3.11 Current Limiting

- 8.3.12 Overcurrent Protection and Full-Cycle Restart

- 8.3.13 Soft Start

- 8.3.14 Slope Compensation

- 8.4 Device Functional Modes

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Application

- 9.2.1 Design Requirements

- 9.2.2

Detailed Design Procedure

- 9.2.2.1 Bulk Capacitor Calculation

- 9.2.2.2 Transformer Design

- 9.2.2.3 MOSFET and Output Diode Selection

- 9.2.2.4 Output Capacitor Calculation

- 9.2.2.5 Current Sensing Network

- 9.2.2.6 Gate Drive Resistor

- 9.2.2.7 REF Bypass Capacitor

- 9.2.2.8 RT and CT

- 9.2.2.9 Start-Up Circuit

- 9.2.2.10 Voltage Feedback Compensation Procedure

- 9.2.3 Application Curves

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

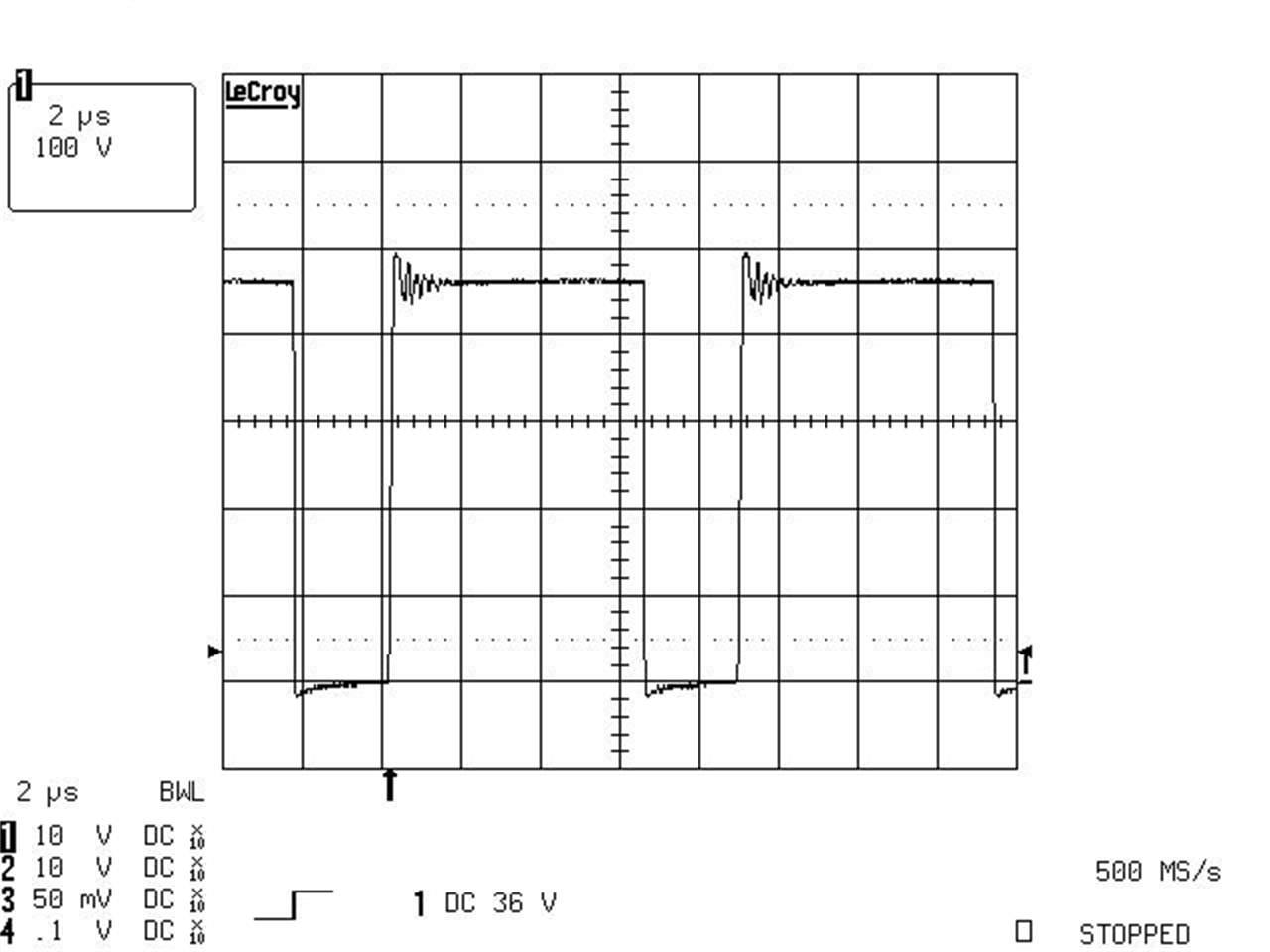

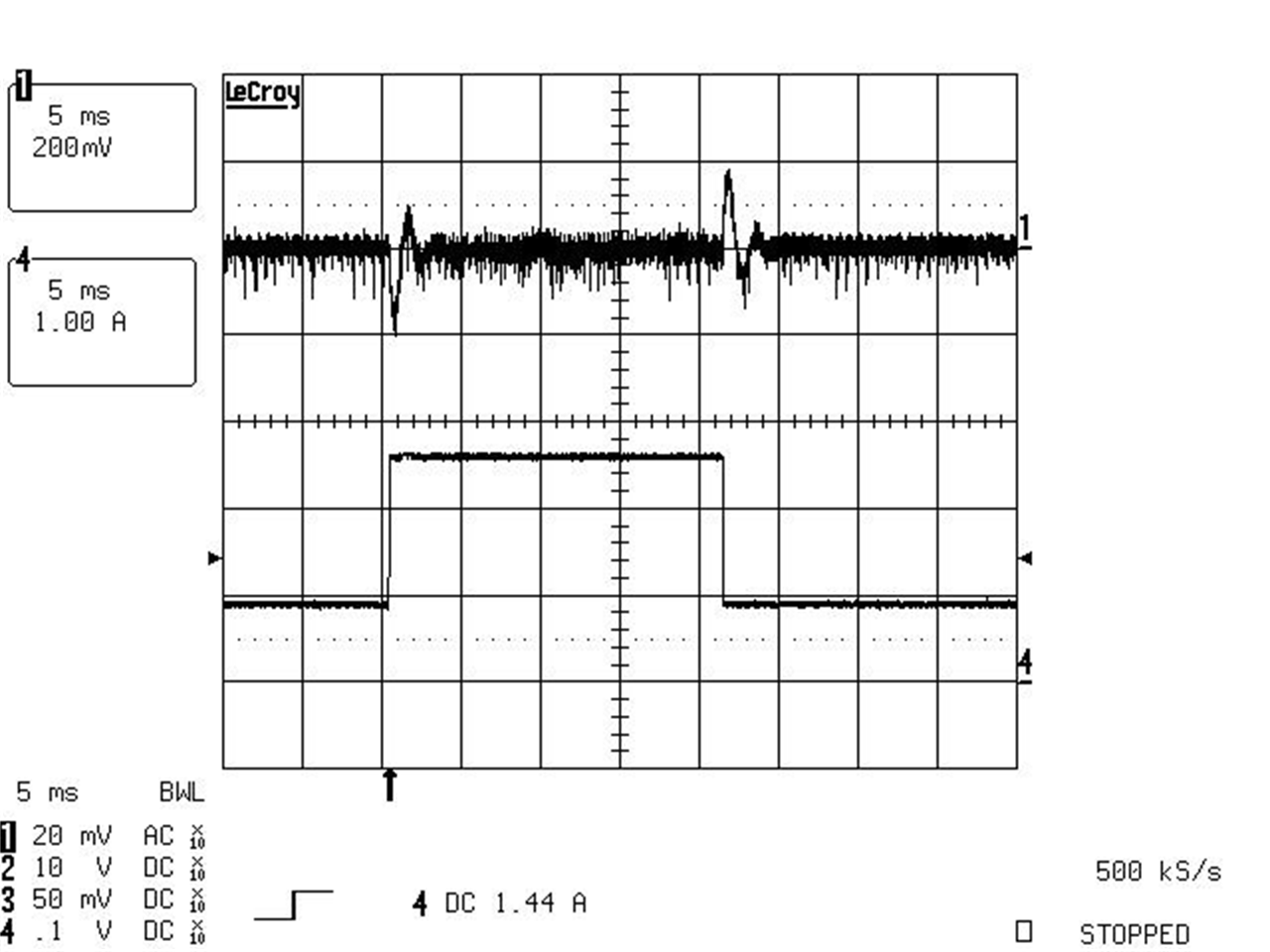

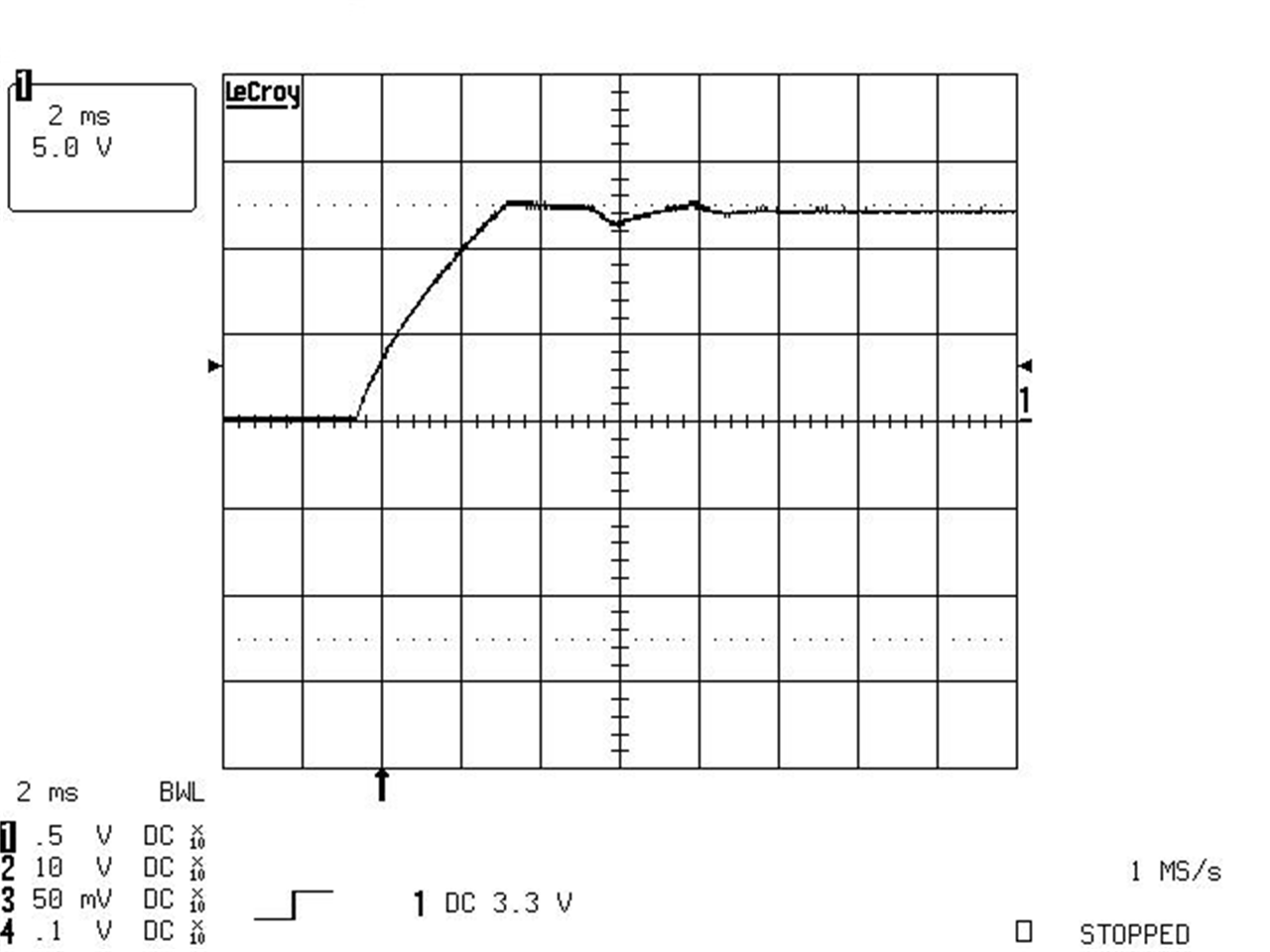

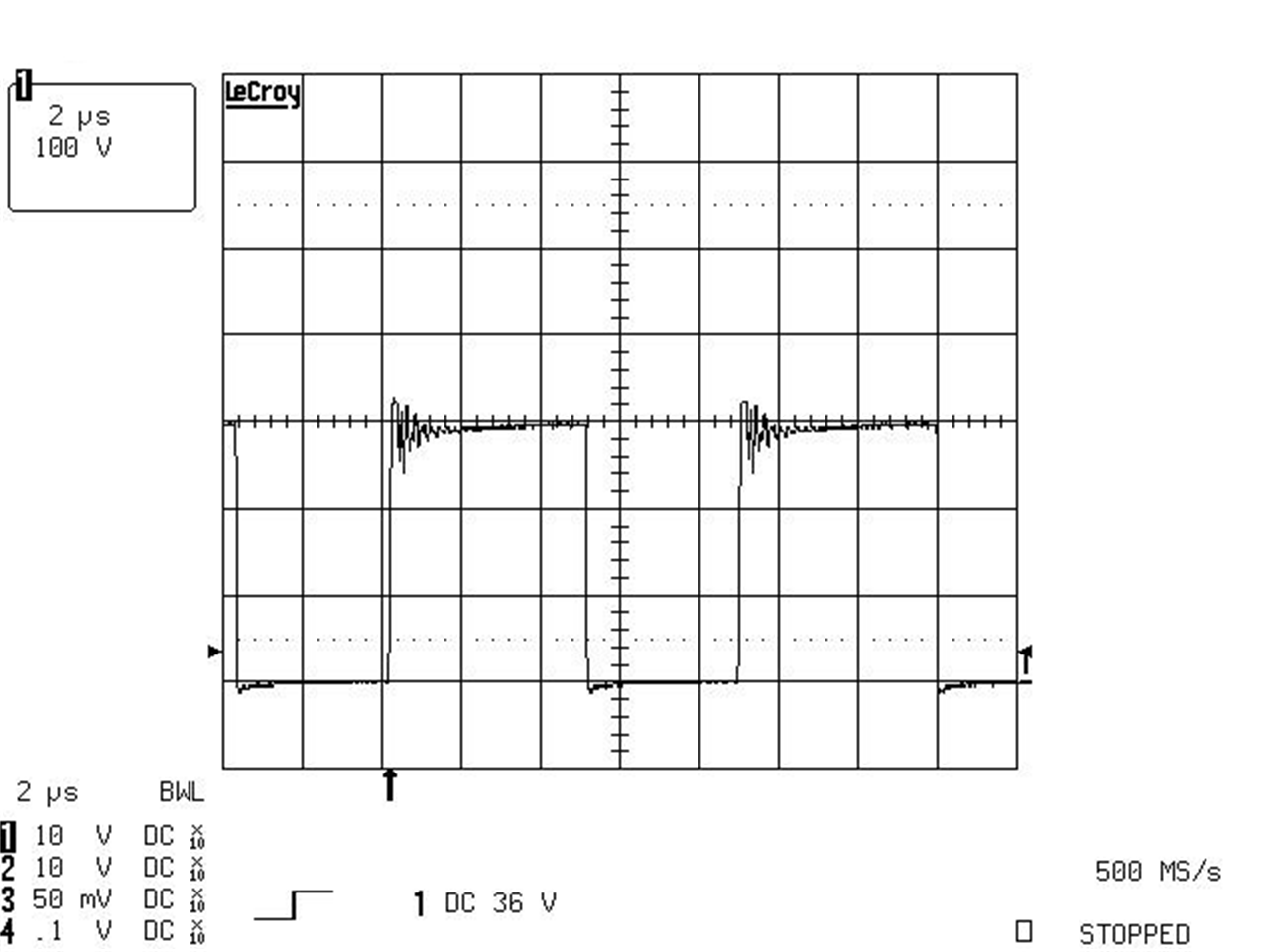

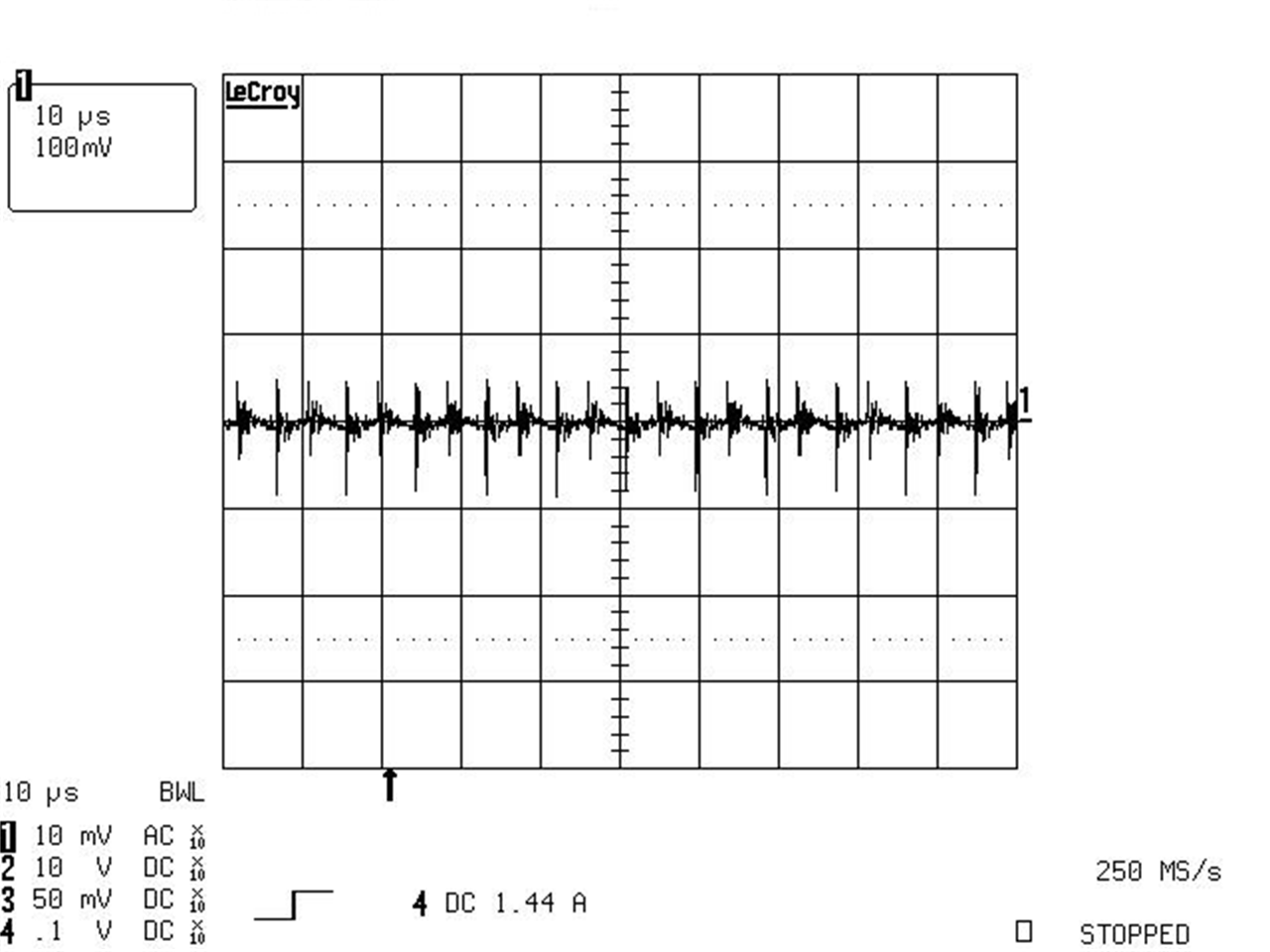

9.2.3 Application Curves

| 100 V/div | 2 µs/div |

| CH1: output voltage AC coupled | 200 mV/div | |

| CH4: output current | 1 A/div | 5 ms/div |

| 5 V/div | 2 ms/div |

| 100 V/div | 2 µs/div |

| 100 mV/div | 10 µs/div | |