ZHCSF10B May 2016 – August 2017 TPS564201

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

1 特性

- TPS564201 集成有 50mΩ 和 22mΩ 场效应晶体管 (FET) 的 4A 转换器

- D-CAP2™模式控制,用于快速瞬态响应

- 输入电压范围:4.5V 至 17V

- 输出电压范围:0.76V 至 7V

- 脉冲跳跃模式

- 560kHz 开关频率

- 低关断电流(小于 5µA)

- 1.6% 反馈电压精度 (25°C)

- 从预偏置输出电压中启动

- 逐周期过流限制

- 断续模式过流保护

- 非锁存欠压保护 (UVP) 和热关断 (TSD) 保护

- 固定软启动时间:1.0ms

- 结合使用 TPS564201 和 WEBENCH® 电源设计器创建定制设计方案

2 应用

- 数字电视电源

- 高清 蓝光™光盘播放器

- 网络家庭终端设备

- 数字机顶盒 (STB)

- 安全监控

3 说明

TPS564201 是一款采用 SOT-23 封装的简单易用型 4A 同步降压转换器。

该器件经过优化,最大限度地减少了运行所需的外部组件并且可以实现低待机电流。

这些开关模式电源 (SMPS) 器件采用 D-CAP2 模式控制,能够提供快速瞬态响应,并且在无需外部补偿组件的情况下支持诸如高分子聚合物等低等效串联电阻 (ESR) 输出电容以及超低 ESR 陶瓷电容器。

TPS564201 可在脉冲跳跃模式下运行,从而能在轻载运行期间保持高效率。 TPS564201 采用 6 引脚 1.6-mm × 2.9-mm SOT (DDC) 封装,额定结温范围为 –40°C 至 125°C。

器件信息(1)

| 器件型号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| TPS564201 | DDC (6) | 1.60mm x 2.90mm |

- 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

空格

空白

空白

简化电路原理图

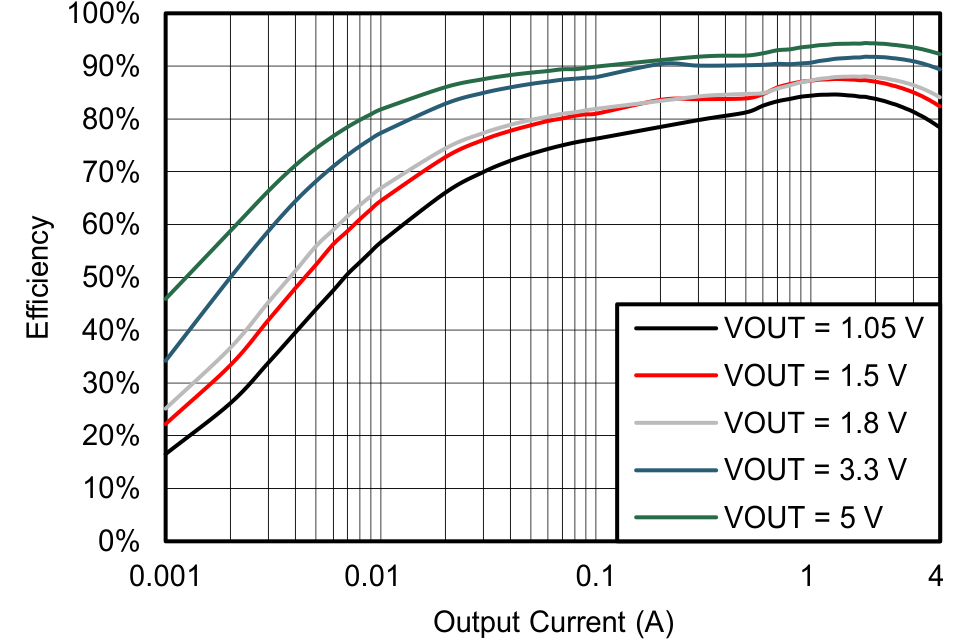

TPS564201 效率