ZHCSBK5B June 2013 – November 2015 TLV716P

PRODUCTION DATA.

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

The TLV716 and TLV716P belong to a family of dual-channel, capacitor-free, 150-mA, low-dropout voltage (LDO) regulators. These devices can be used with or without external capacitors and are available in a 1.2-mm × 1.2-mm package, making these devices a very small solution size for dual-channel, low-dropout (LDO) regulators. This family of LDO regulators offers current limit and thermal protection, and is specified from –40°C to 85°C. Figure 24 shows an application circuit for this family of devices.

8.2 Typical Application

8.2.1 Design Requirements

Table 1 lists the design requirements.

Table 1. Design Parameters

| PARAMETER | DESIGN REQUIREMENT | |||

|---|---|---|---|---|

| Input voltage | 4.2 V to 3 V (Lithium Ion battery) | |||

| Output 1 voltage | 2.8 V ±1.5% | |||

| Output 1 DC current | 50 mA | |||

| Output 2 voltage | 1.8 V ±1.5% | |||

| Output2 DC current | 10 mA | |||

| Maximum ambient temperature | 65°C | |||

8.2.2 Detailed Design Procedure

An input capacitor is not required for this design because of the low impedance connection directly to the battery. No output capacitor allows for the minimal possible inrush current during start-up, ensuring the 180-mA maximum input current limit is not exceeded. Verify that the maximum junction temperature is not exceeded by calculating the total power dissipation and the junction temperature rise. For this example the total worst case power dissipation is (4.2 V - 2.8 V) × 0.05 A + (4.2 V - 1.8 V) × 0.01 = 0.094 W. The rise in junction temperature is calculated by multiplying the power dissipation by thermal resistance RθJA. For this example, assuming the board size is similar to the JEDEC High K standard, the rise in junction temperature is 0.094 W × 149.3 °C/W = 14°C. The junction temperature is calculated by adding the rise in junction temperature to the maximum ambient temperature; in this example the maximum junction temperature can be calculated to be 65°C + 14°C = 79°C. It is mandatary to keep the junction temperature below the maximum operating junction temperature. For additional thermal information see the Thermal Considerations and Power Dissipation sections.

8.2.2.1 Input and Output Capacitor Requirements

The TLV716 and TLV716P uses an advanced internal control loop to obtain stable operation both with or without the use of input or output capacitors. If an output capacitor is used the device can support values as high as 100-µF. The dynamic performance of the device is improved with the use of an output capacitor. An output capacitance of 0.1 μF or larger generally provides good dynamic response. X5R- and X7R-type ceramic capacitors are recommended because these capacitors have minimal variation in value and equivalent series resistance (ESR) over temperature.

Although an input capacitor is not required for stability, good analog design practice is to connect a 0.1-µF to

1-µF capacitor from IN to GND. This capacitor counteracts input source impedance and improves supply transient response, input ripple, and PSRR. A higher value capacitor may be necessary if large, fast, rise-time load transients are anticipated or if the device is located several inches from the input power source.

8.2.2.2 Dropout Voltage

The TLV716 and TLV716P use a PMOS pass transistor to achieve low dropout. When (VIN – VOUT) is less than the dropout voltage (VDO), the PMOS pass device is in the linear region of operation and the input-to-output resistance is the RDS(ON) of the PMOS pass element. VDO scales approximately with the output current because the PMOS device behaves like a resistor in dropout.

As with any linear regulator, PSRR and transient response are degraded as (VIN – VOUT) approaches dropout.

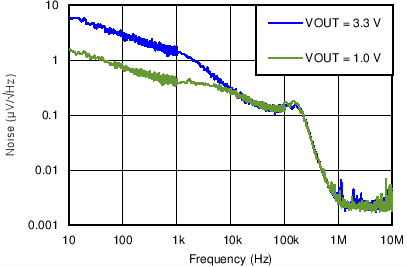

8.2.3 Application Curves