ZHCSDK3 March 2015 LPV542

PRODUCTION DATA.

10 Layout

10.1 Layout Guidelines

The V+ pin should be bypassed to ground with a low ESR capacitor.

The optimum placement is closest to the V+ and ground pins.

Care should be taken to minimize the loop area formed by the bypass capacitor connection between V+ and ground.

The ground pin should be connected to the PCB ground plane at the pin of the device.

The feedback components should be placed as close to the device as possible to minimize strays.

There is an internal electrical connection between the exposed Die Attach Pad (DAP) and the V- pin. For best performance the DAP should be connected to the exact same potential as the V- pin. Do not use the DAP as the primary V- supply. Floating the DAP pad is not recommended. The DAP and V- pin should be joined directly as shown in the Layout Example.

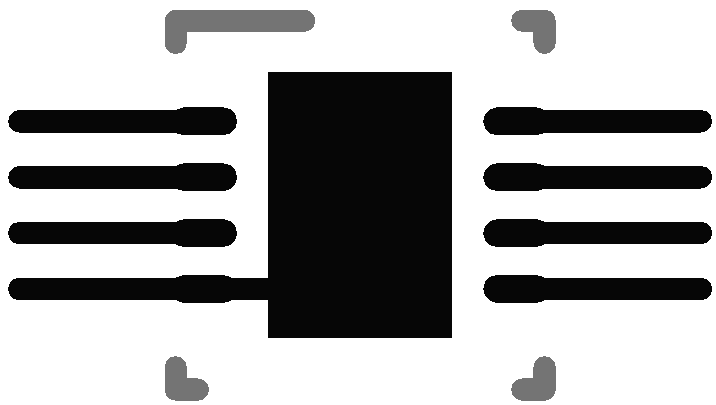

10.2 Layout Example

Figure 41. X1SON Layout Example (top view)

Figure 41. X1SON Layout Example (top view)