ZHCSQ62F November 1998 – March 2022 CD54HC173 , CD54HCT173 , CD74HC173 , CD74HCT173

PRODUCTION DATA

- 1 特性

- 2 说明

- 3 Revision History

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Power Supply Recommendations

- 9 Layout

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

封装选项

请参考 PDF 数据表获取器件具体的封装图。

机械数据 (封装 | 引脚)

- N|16

- D|16

散热焊盘机械数据 (封装 | 引脚)

- D|16

订购信息

6 Parameter Measurement Information

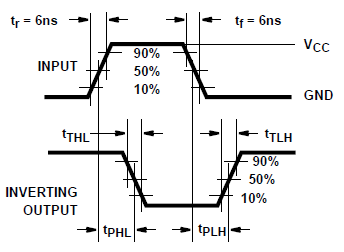

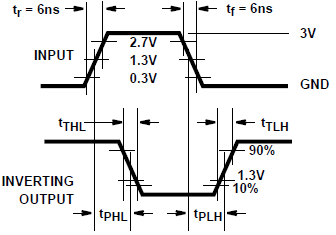

tPD is the maximum between tPLH and tPHL

tt is the maximum between tTLH and tTHL

NOTE: Outputs should be switching from 10% VCC to 90% VCC in accordance with device truth table. For fMAX, input duty cycle = 50%

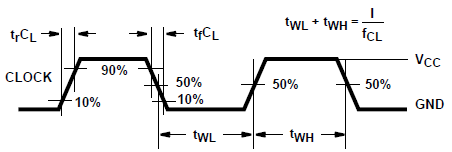

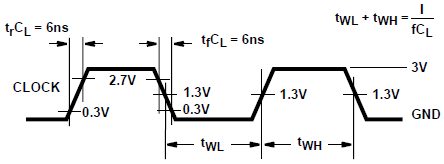

Figure 6-1 HC clock pulse rise and fall times and pulse width Figure 6-3 HC and HCU transition

times and propagation delay times, combination logic

Figure 6-3 HC and HCU transition

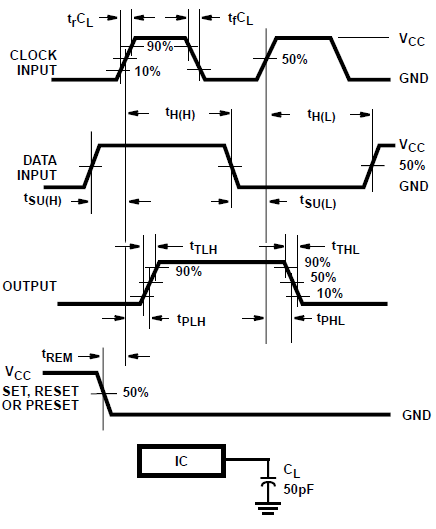

times and propagation delay times, combination logic Figure 6-5 HC setup times, hold

times, removal time, and propagation delay times for edge triggered

sequential logic circuits

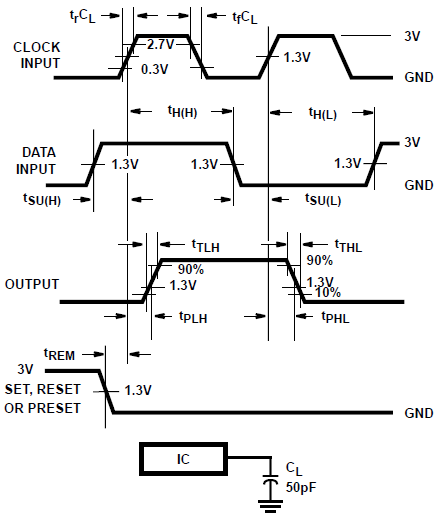

Figure 6-5 HC setup times, hold

times, removal time, and propagation delay times for edge triggered

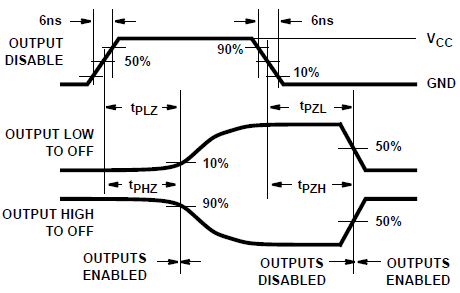

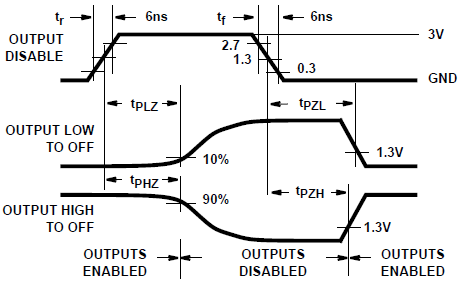

sequential logic circuits Figure 6-7 HC three-state propagation

delay waveform

Figure 6-7 HC three-state propagation

delay waveform

NOTE: Outputs should be switching from 10% VCC to 90% VCC in accordance with device truth table. FOr fMAX, input duty cycle = 50%

Figure 6-2 HCT clock pulse rise and fall times and pulse width Figure 6-4 HCT transition times and

propagation delay times, combination logic

Figure 6-4 HCT transition times and

propagation delay times, combination logic Figure 6-6 HCT setup times, hold

times, removal time, and propagation delay times for edge triggered

sequential logic circuits

Figure 6-6 HCT setup times, hold

times, removal time, and propagation delay times for edge triggered

sequential logic circuits Figure 6-8 HCT three-state

propagation delay waveform

Figure 6-8 HCT three-state

propagation delay waveform

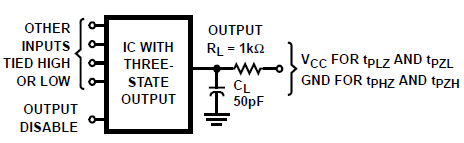

NOTE: Opend drain waveforms tPLZ and tPZL are the same as those for three-state shown on the left. The test circuit is Output RL = 1kΩ to VCC, CL = 50pF

Figure 6-9 HC and HCT three-state propagation delay test circuit