ZHCSDW0 July 2015 ADS8664 , ADS8668

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Analog Inputs

- 8.3.2 Analog Input Impedance

- 8.3.3 Input Overvoltage Protection Circuit

- 8.3.4 Programmable Gain Amplifier (PGA)

- 8.3.5 Second-Order, Low-Pass Filter (LPF)

- 8.3.6 ADC Driver

- 8.3.7 Multiplexer (MUX)

- 8.3.8 Reference

- 8.3.9 Auxiliary Channel

- 8.3.10 ADC Transfer Function

- 8.3.11 Alarm Feature

- 8.4

Device Functional Modes

- 8.4.1 Device Interface

- 8.4.2

Device Modes

- 8.4.2.1 Continued Operation in the Selected Mode (NO_OP)

- 8.4.2.2 Frame Abort Condition (FRAME_ABORT)

- 8.4.2.3 STANDBY Mode (STDBY)

- 8.4.2.4 Power-Down Mode (PWR_DN)

- 8.4.2.5 Auto Channel Enable with Reset (AUTO_RST)

- 8.4.2.6 Manual Channel n Select (MAN_Ch_n)

- 8.4.2.7 Channel Sequencing Modes

- 8.4.2.8 Reset Program Registers (RST)

- 8.5

Register Maps

- 8.5.1 Command Register Description

- 8.5.2

Program Register Description

- 8.5.2.1 Program Register Read/Write Operation

- 8.5.2.2 Program Register Map

- 8.5.2.3

Program Register Descriptions

- 8.5.2.3.1 Auto-Scan Sequencing Control Registers

- 8.5.2.3.2 Device Features Selection Control Register (address = 03h)

- 8.5.2.3.3 Range Select Registers (addresses 05h-0Ch)

- 8.5.2.3.4 Alarm Flag Registers (Read-Only)

- 8.5.2.3.5 Alarm Threshold Setting Registers

- 8.5.2.3.6 Command Read-Back Register (address = 3Fh)

- 9 Application and Implementation

- 10Power-Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | |

|---|---|---|---|

| AIN_nP, AIN_nGND to GND(2) | –20 | 20 | V |

| AIN_nP, AIN_nGND to GND(3) | –11 | 11 | V |

| AUX_GND to GND | –0.3 | 0.3 | V |

| AUX_IN to GND | –0.3 | AVDD + 0.3 | V |

| AVDD to GND or DVDD to GND | –0.3 | 7 | V |

| REFCAP to REFGND or REFIO to REFGND | –0.3 | 5.7 | V |

| GND to REFGND | –0.3 | 0.3 | V |

| Digital input pins to GND | –0.3 | DVDD + 0.3 | V |

| Digital output pins to GND | –0.3 | DVDD + 0.3 | V |

| Operating temperature, TA | –40 | 125 | °C |

| Storage temperature, Tstg | –65 | 150 | °C |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) AVDD = 5 V or offers a low impedance of < 30 kΩ.

(3) AVDD = floating with an impedance > 30 kΩ.

7.2 ESD Ratings

| VALUE | UNIT | ||||

|---|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | Analog input pins (AIN_nP; AIN_nGND) | ±4000 | V |

| All other pins | ±2000 | ||||

| Charged device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | ||||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| AVDD | Analog supply voltage | 4.75 | 5 | 5.25 | V |

| DVDD | Digital supply voltage | 1.65 | 3.3 | AVDD | V |

7.4 Thermal Information

| THERMAL METRIC(1) | ADS8664, ADS8668 | UNIT | |

|---|---|---|---|

| DBT (TSSOP) | |||

| 38 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 68.8 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 19.9 | °C/W |

| RθJB | Junction-to-board thermal resistance | 30.4 | °C/W |

| ψJT | Junction-to-top characterization parameter | 1.3 | °C/W |

| ψJB | Junction-to-board characterization parameter | 29.8 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | NA | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

7.5 Electrical Characteristics

Minimum and maximum specifications are at TA = –40°C to 125°C. Typical specifications are at TA = 25°C.AVDD = 5 V, DVDD = 3 V, VREF = 4.096 V (internal), and fSAMPLE = 500 kSPS, unless otherwise noted.

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | TEST LEVEL(1) | |||

|---|---|---|---|---|---|---|---|---|---|

| ANALOG INPUTS | |||||||||

| Full-scale input span(2)

(AIN_nP to AIN_nGND) |

Input range = ±2.5 × VREF | –2.5 × VREF | 2.5 × VREF | V | A | ||||

| Input range = ±1.25 × VREF | –1.25 × VREF | 1.25 × VREF | A | ||||||

| Input range = ±0.625 × VREF | –0.625 × VREF | 0.625 × VREF | A | ||||||

| Input range = ±0.3125 × VREF | –0.3125 × VREF | 0.3125 × VREF | A | ||||||

| Input range = ±0.15625 × VREF | –0.15625 × VREF | 0.15625 × VREF | A | ||||||

| Input range = 2.5 × VREF | 0 | 2.5 × VREF | A | ||||||

| Input range = 1.25 × VREF | 0 | 1.25 × VREF | A | ||||||

| Input range = 0.625 × VREF | 0 | 0.625 × VREF | A | ||||||

| Input range = 0.3125 × VREF | 0 | 0.3125 × VREF | A | ||||||

| AIN_nP | Operating input range, positive input |

Input range = ±2.5 × VREF | –2.5 × VREF | 2.5 × VREF | V | A | |||

| Input range = ±1.25 × VREF | –1.25 × VREF | 1.25 × VREF | A | ||||||

| Input range = ±0.625 × VREF | –0.625 × VREF | 0.625 × VREF | A | ||||||

| Input range = ±0.3125 × VREF | –0.3125 × VREF | 0.3125 × VREF | A | ||||||

| Input range = ±0.15625 × VREF | –0.15625 × VREF | 0.15625 × VREF | A | ||||||

| Input range = 2.5 × VREF | 0 | 2.5 × VREF | A | ||||||

| Input range = 1.25 × VREF | 0 | 1.25 × VREF | A | ||||||

| Input range = 0.625 × VREF | 0 | 0.625 × VREF | A | ||||||

| Input range = 0.3125 × VREF | 0 | 0.3125 × VREF | A | ||||||

| AIN_nGND | Operating input range, negative input |

All input ranges | –0.1 | 0 | 0.1 | V | B | ||

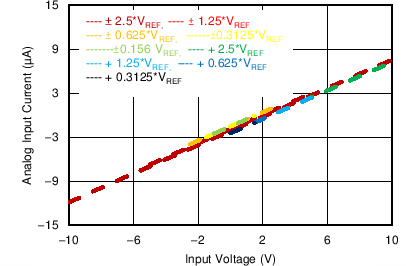

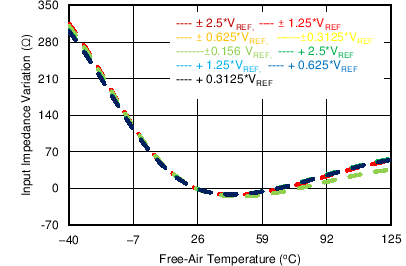

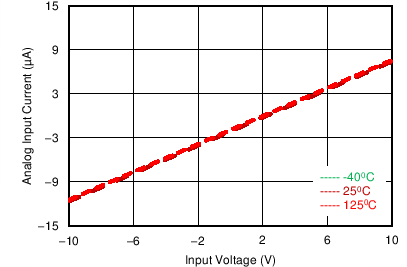

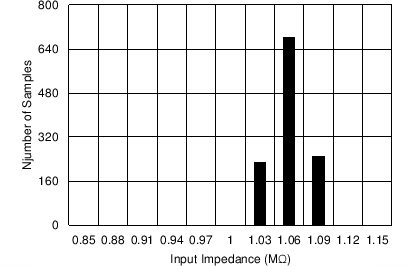

| zi | Input impedance | At TA = 25°C, all input ranges |

0.85 | 1 | 1.15 | MΩ | B | ||

| Input impedance drift | All input ranges | 7 | 25 | ppm/°C | B | ||||

| IIkg(in) | Input leakage current | With voltage at AIN_nP pin = VIN, input range = ±2.5 × VREF |

VIN – 2.25 ———— RIN |

µA | A | ||||

| With voltage at AIN_nP pin = VIN, input range = ±1.25 × VREF |

VIN – 2.00 ———— RIN |

A | |||||||

| With voltage at AIN_nP pin = VIN, input ranges = ±0.625 × VREF; ±0.3125 × VREF; ±0.15625 × VREF |

VIN – 1.60 ———— RIN |

A | |||||||

| With voltage at AIN_nP pin = VIN, input range = 2.5 × VREF |

VIN – 2.50 ———— RIN |

A | |||||||

| With voltage at AIN_nP pin = VIN, input range = 1.25 × VREF; 0.625 × VREF; 0.3125 × VREF |

VIN – 2.50 ———— RIN |

A | |||||||

| INPUT OVERVOLTAGE PROTECTION | |||||||||

| VOVP | Overvoltage protection voltage | AVDD = 5 V or offers low impedance < 30 kΩ, all input ranges | –20 | 20 | V | B | |||

| AVDD = floating with impedance > 30 kΩ, all input ranges |

–11 | 11 | B | ||||||

| SYSTEM PERFORMANCE | |||||||||

| Resolution | 12 | Bits | A | ||||||

| NMC | No missing codes | 12 | Bits | A | |||||

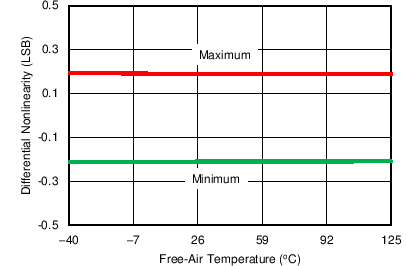

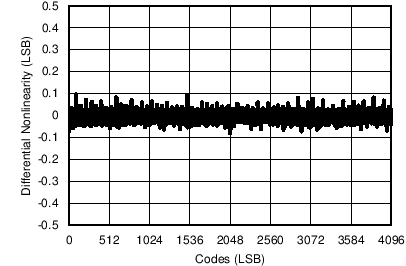

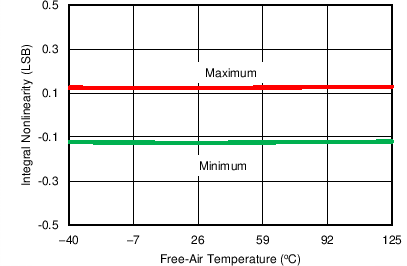

| DNL | Differential nonlinearity | –0.5 | ±0.2 | 0.5 | LSB(3) | A | |||

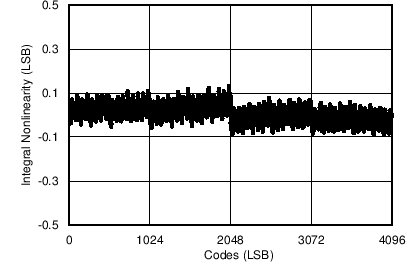

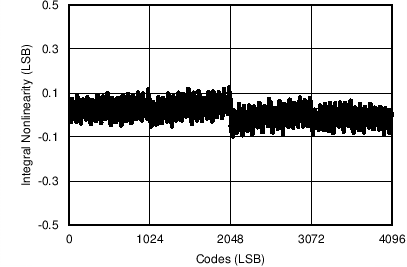

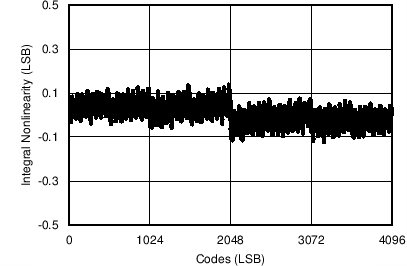

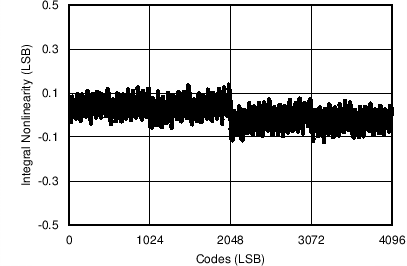

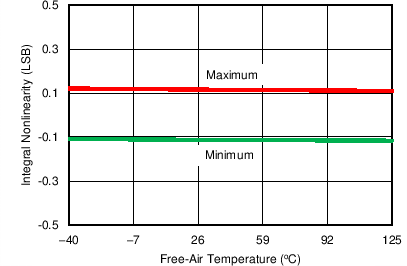

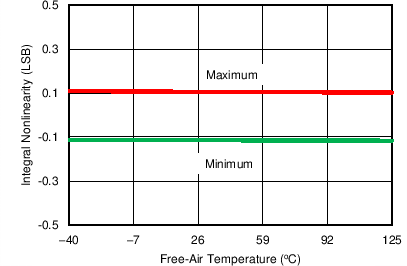

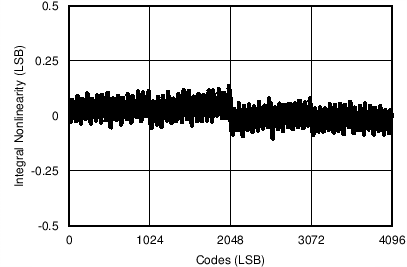

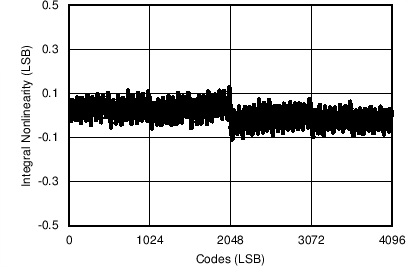

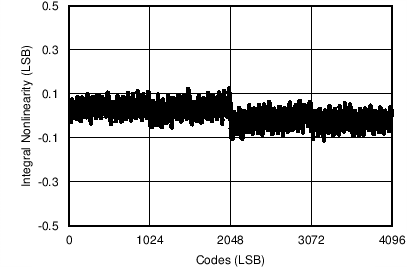

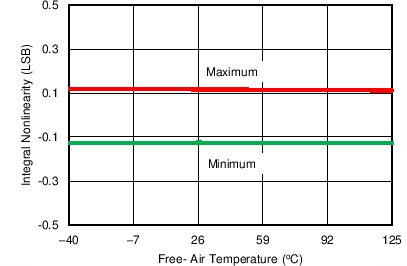

| INL | Integral nonlinearity(6) | –0.5 | ±0.2 | 0.5 | LSB | A | |||

| EG | Gain error | At TA = 25°C, all input ranges | ±0.05 | ±0.1 | %FSR(4) | A | |||

| Gain error matching (channel-to-channel) |

At TA = 25°C, all input ranges | ±0.05 | ±0.1 | %FSR | A | ||||

| Gain error temperature drift | All input ranges | 1 | 5 | ppm/°C | B | ||||

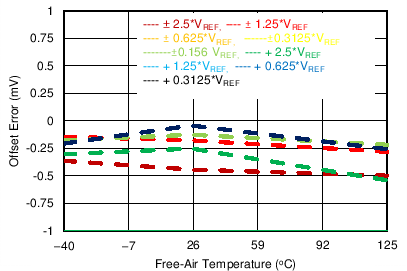

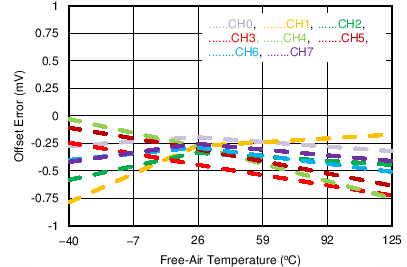

| EO | Offset error | At TA = 25°C, all input ranges |

±1 | ±2.5 | mV | A | |||

| Offset error matching (channel-to-channel) |

At TA = 25°C, all input ranges |

±1 | ±2.5 | mV | A | ||||

| Offset error temperature drift | Input range = ±2.5 × VREF | 1 | 3 | ppm/°C | B | ||||

| Input range = ±1.25 × VREF | 1 | 3 | B | ||||||

| Input range = ±0.625 × VREF | 1 | 3 | B | ||||||

| Input range = ±0.3125 × VREF | 2 | 6 | B | ||||||

| Input range = ±0.15625 × VREF | 4 | 12 | B | ||||||

| Input range = 0 to 2.5 × VREF | 1 | 3 | B | ||||||

| Input range = 0 to 1.25 × VREF | 1 | 3 | B | ||||||

| Input range = 0 to 0.625 × VREF | 2 | 6 | B | ||||||

| Input range = 0 to 0.3125 × VREF | 4 | 12 | B | ||||||

| SAMPLING DYNAMICS | |||||||||

| tCONV | Conversion time | 850 | ns | A | |||||

| tACQ | Acquisition time | 1150 | ns | A | |||||

| fS | Maximum throughput rate without latency |

500 | kSPS | A | |||||

| DYNAMIC CHARACTERISTICS | |||||||||

| SNR | Signal-to-noise ratio (VIN – 0.5 dBFS at 1 kHz) |

Input range = ±2.5 × VREF | 73 | 73.85 | dB | A | |||

| Input range = ±1.25 × VREF | 73 | 73.85 | A | ||||||

| Input range = ±0.625 × VREF | 73 | 73.85 | A | ||||||

| Input range = ±0.3125 × VREF | 72.7 | 73.5 | A | ||||||

| Input range = ±0.15625 × VREF | 71.4 | 72.5 | A | ||||||

| Input range = 2.5 × VREF | 73 | 73.85 | A | ||||||

| Input range = 1.25 × VREF | 73 | 73.85 | A | ||||||

| Input range = 0.625 × VREF | 72.7 | 73.5 | A | ||||||

| Input range = 0.3125 × VREF | 71.4 | 72.5 | A | ||||||

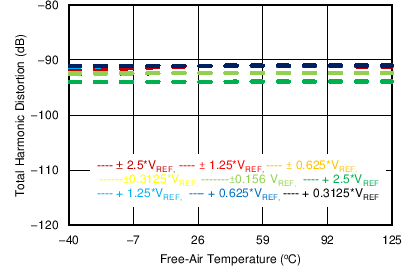

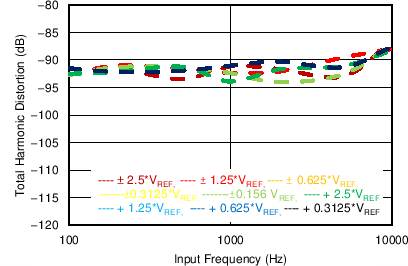

| THD | Total harmonic distortion(5)

(VIN – 0.5 dBFS at 1 kHz) |

All input ranges | –95 | dB | B | ||||

| SINAD | Signal-to-noise ratio (VIN – 0.5 dBFS at 1 kHz) |

Input range = ±2.5 × VREF | 73 | 73.8 | dB | A | |||

| Input range = ±1.25 × VREF | 73 | 73.8 | A | ||||||

| Input range = ±0.625 × VREF | 73 | 73.8 | A | ||||||

| Input range = ±0.3125 × VREF | 72.7 | 73.5 | A | ||||||

| Input range = ±0.15625 × VREF | 71.4 | 72.5 | A | ||||||

| Input range = 2.5 × VREF | 73 | 73.8 | A | ||||||

| Input range = 1.25 × VREF | 73 | 73.8 | A | ||||||

| Input range = 0.625 × VREF | 72.7 | 73.5 | A | ||||||

| Input range = 0.3125 × VREF | 71.4 | 72.5 | A | ||||||

| SFDR | Spurious-free dynamic range (VIN – 0.5 dBFS at 1 kHz) |

All input ranges | 97 | dB | B | ||||

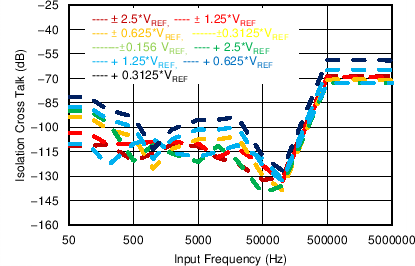

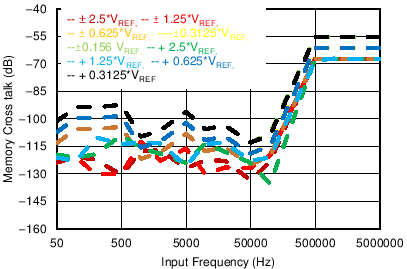

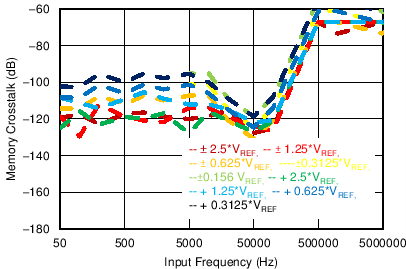

| Crosstalk isolation(7) | Aggressor channel input overdriven to 2 × maximum input voltage | 110 | dB | B | |||||

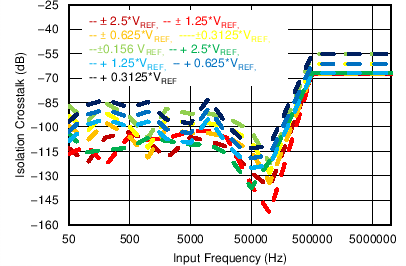

| Crosstalk memory(8) | Aggressor channel input overdriven to 2 × maximum input voltage | 90 | dB | B | |||||

| BW(–3 dB) | Small-signal bandwidth, –3 dB | At TA = 25°C, all input ranges | 15 | kHz | B | ||||

| BW(–0.1 dB) | Small-signal bandwidth, –0.1 dB | At TA = 25°C, all input ranges | 2.5 | kHz | B | ||||

| AUXILIARY CHANNEL | |||||||||

| Resolution | 12 | Bits | A | ||||||

| V(AUX_IN) | AUX_IN voltage range | (AUX_IN – AUX_GND) | 0 | VREF | V | A | |||

| Operating input range | AUX_IN | 0 | VREF | V | A | ||||

| AUX_GND | 0 | V | A | ||||||

| Ci | Input capacitance | During sampling | 75 | pF | C | ||||

| During conversion | 5 | pF | C | ||||||

| IIkg(in) | Input leakage current | 100 | nA | A | |||||

| DNL | Differential nonlinearity | –0.5 | ±0.2 | 0.5 | LSB | A | |||

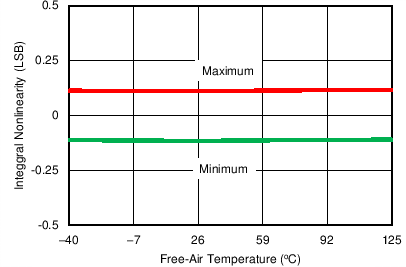

| INL | Integral nonlinearity | –0.75 | ±0.5 | 0.75 | LSB | A | |||

| EG(AUX) | Gain error | At TA = 25°C | ±0.02 | ±0.2 | %FSR | A | |||

| EO(AUX) | Offset error | At TA = 25°C | –5 | 5 | mV | A | |||

| SNR | Signal-to-noise ratio | V(AUX_IN) = –0.5 dBFS at 1 kHz | 73.2 | 73.7 | dB | A | |||

| THD | Total harmonic distortion(5) | V(AUX_IN) = –0.5 dBFS at 1 kHz | –90 | dB | B | ||||

| SINAD | Signal-to-noise + distortion | V(AUX_IN) = –0.5 dBFS at 1 kHz | 72.5 | 73.5 | dB | A | |||

| SFDR | Spurious-free dynamic range | V(AUX_IN) = –0.5 dBFS at 1 kHz | 93 | dB | B | ||||

| INTERNAL REFERENCE OUTPUT | |||||||||

| V(REFIO_INT)(9) | Voltage on REFIO pin (configured as output) |

At TA = 25°C | 4.094 | 4.096 | 4.098 | V | A | ||

| Internal reference temperature drift | 8 | 20 | ppm/°C | B | |||||

| C(OUT_REFIO) | Decoupling capacitor on REFIO | 10 | 22 | µF | B | ||||

| V(REFCAP) | Reference voltage to ADC (on REFCAP pin) |

At TA = 25°C | 4.094 | 4.096 | 4.098 | V | A | ||

| Reference buffer output impedance | 0.5 | 1 | Ω | B | |||||

| Reference buffer temperature drift | 0.6 | 1.5 | ppm/°C | B | |||||

| C(OUT_REFCAP) | Decoupling capacitor on REFCAP | 10 | 22 | μF | B | ||||

| Turn-on time | C(OUT_REFCAP) = 22 µF, C(OUT_REFIO) = 22 µF |

15 | ms | B | |||||

| EXTERNAL REFERENCE INPUT | |||||||||

| VREFIO_EXT | External reference voltage on REFIO (configured as input) | 4.046 | 4.096 | 4.146 | V | C | |||

| POWER-SUPPLY REQUIREMENTS | |||||||||

| AVDD | Analog power-supply voltage | Analog supply | 4.75 | 5 | 5.25 | V | B | ||

| DVDD | Digital power-supply voltage | Digital supply range | 1.65 | 3.3 | AVDD | V | B | ||

| Digital supply range for specified performance | 2.7 | 3.3 | 5.25 | B | |||||

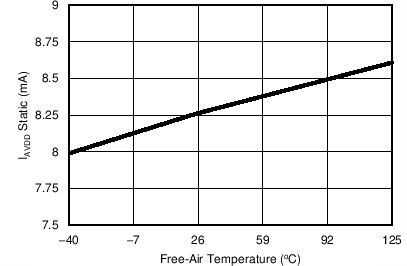

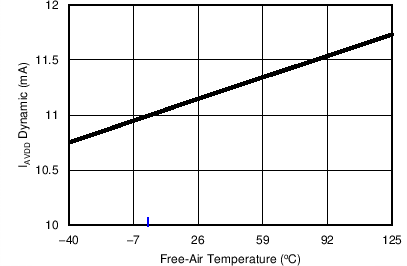

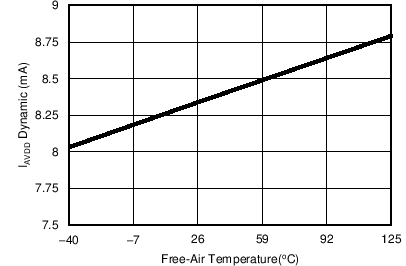

| IAVDD_DYN | Analog supply current | Dynamic, AVDD | For the ADS8668; AVDD = 5 V, fS = maximum and internal reference | 13 | 16 | mA | A | ||

| For the ADS8664; AVDD = 5 V, fS = maximum and internal reference | 8.5 | 11.5 | A | ||||||

| IAVDD_STC | Static | For the ADS8668; AVDD = 5 V, device not converting and internal reference | 10 | 12 | mA | A | |||

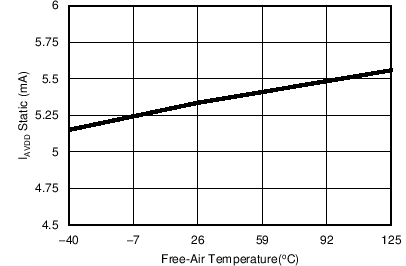

| For the ADS8664; AVDD = 5 V, device not converting and internal reference | 5.5 | 8.5 | A | ||||||

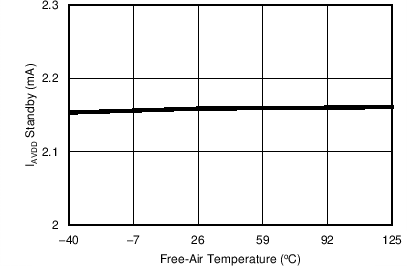

| ISTDBY | Standby | At AVDD = 5 V, device in STDBY mode and internal reference | 3 | 4.5 | mA | A | |||

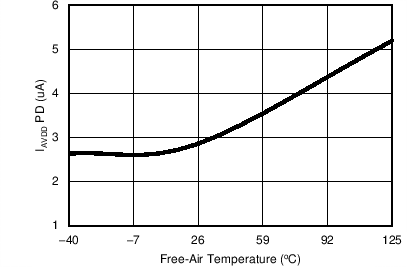

| IPWR_DN | Power-down | At AVDD = 5 V, device in PWR_DN | 3 | 20 | μA | B | |||

| IDVDD_DYN | Digital supply current | At DVDD = 3.3 V, output = 0000h | 0.5 | mA | A | ||||

| DIGITAL INPUTS (CMOS) | |||||||||

| VIH | Digital input logic levels DVDD > 2.1 V |

0.7 × DVDD | DVDD + 0.3 | V | A | ||||

| VIL | –0.3 | 0.3 × DVDD | A | ||||||

| VIH | Digital input logic levels DVDD ≤ 2.1 V |

0.8 × DVDD | DVDD + 0.3 | V | A | ||||

| VIL | –0.3 | 0.2 × DVDD | A | ||||||

| Input leakage current | 100 | nA | A | ||||||

| Input pin capacitance | 5 | pF | C | ||||||

| DIGITAL OUTPUTS (CMOS) | |||||||||

| VOH | Digital output logic levels | IO = 500-μA source | 0.8 × DVDD | DVDD | V | A | |||

| VOL | IO = 500-μA sink | 0 | 0.2 × DVDD | A | |||||

| Floating state leakage current | Only for SDO | 1 | µA | A | |||||

| Internal pin capacitance | 5 | pF | C | ||||||

| TEMPERATURE RANGE | |||||||||

| TA | Operating free-air temperature | –40 | 125 | °C | B | ||||

(1) Test Levels: (A) Tested at final test. Over temperature limits are set by characterization and simulation. (B) Limits set by characterization and simulation, across temperature range. (C) Typical value only for information, provided by design simulation.

(2) Ideal input span, does not include gain or offset error.

(3) LSB = least significant bit.

(4) FSR = full-scale range.

(5) Calculated on the first nine harmonics of the input frequency.

(6) This parameter is the endpoint INL, not best-fit INL.

(7) Isolation crosstalk is measured by applying a full-scale sinusoidal signal up to 10 kHz to a channel, not selected in the multiplexing sequence, and measuring its effect on the output of any selected channel.

(8) Memory crosstalk is measured by applying a full-scale sinusoidal signal up to 10 kHz to a channel that is selected in the multiplexing sequence, and measuring its effect on the output of the next selected channel for all combinations of input channels.

(9) Does not include the variation in voltage resulting from solder-shift and long-term effects.

7.6 Timing Requirements: Serial Interface

Minimum and maximum specifications are at TA = –40°C to 125°C. Typical specifications are at TA = 25°C.AVDD = 5 V, DVDD = 3 V, VREF = 4.096 V (internal), SDO load = 20 pF, and fSAMPLE = 500 kSPS, unless otherwise noted.

| MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|

| TIMING SPECIFICATIONS | |||||

| fS | Sampling frequency (fCLK = max) | 500 | kSPS | ||

| tS | ADC cycle time period (fCLK = max) | 2 | µs | ||

| fSCLK | Serial clock frequency (fS = max) | 17 | MHz | ||

| tSCLK | Serial clock time period (fS = max) | 59 | ns | ||

| tCONV | Conversion time | 850 | ns | ||

| tDZ_CSDO | Delay time: CS falling to data enable | 10 | ns | ||

| tD_CKCS | Delay time: last SCLK falling to CS rising | 10 | ns | ||

| tDZ_CSDO | Delay time: CS rising to SDO going to 3-state | 10 | ns | ||

| TIMING REQUIREMENTS | |||||

| tACQ | Acquisition time | 1150 | ns | ||

| tPH_CK | Clock high time | 0.4 | 0.6 | tSCLK | |

| tPL_CK | Clock low time | 0.4 | 0.6 | tSCLK | |

| tPH_CS | CS high time | 30 | ns | ||

| tSU_CSCK | Setup time: CS falling to SCLK falling | 30 | ns | ||

| tHT_CKDO | Hold time: SCLK falling to (previous) data valid on SDO | 10 | ns | ||

| tSU_DOCK | Setup time: SDO data valid to SCLK falling | 25 | ns | ||

| tSU_DICK | Setup time: SDI data valid to SCLK falling | 5 | ns | ||

| tHT_CKDI | Hold time: SCLK falling to (previous) data valid on SDI | 5 | ns | ||

| tSU_DSYCK | Setup time: DAISY data valid to SCLK falling | 5 | ns | ||

| tHT_CKDSY | Hold time: SCLK falling to (previous) data valid on DAISY | 5 | ns | ||

Figure 1. Serial Interface Timing Diagram

Figure 1. Serial Interface Timing Diagram

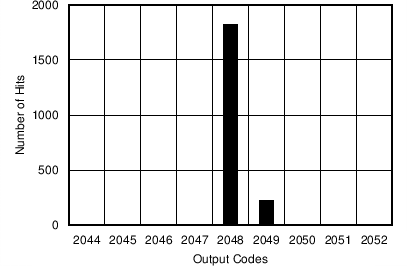

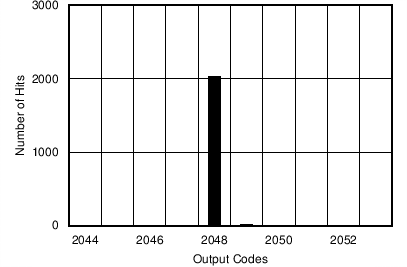

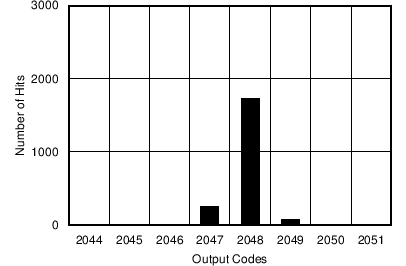

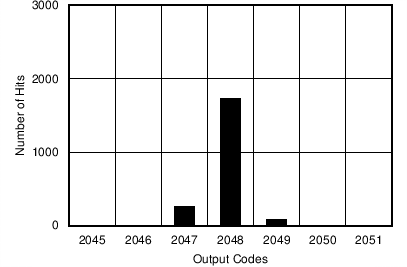

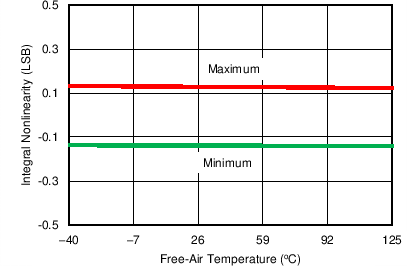

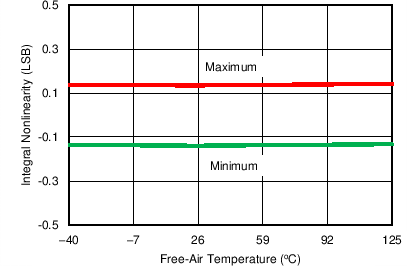

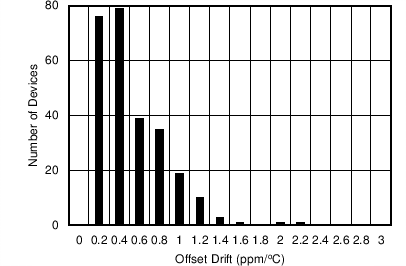

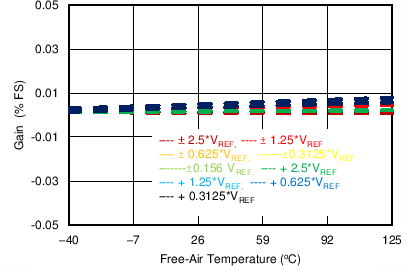

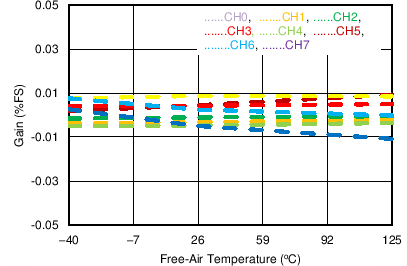

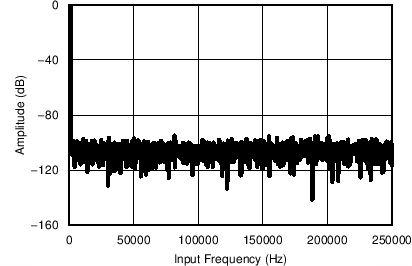

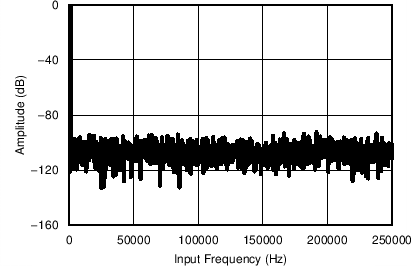

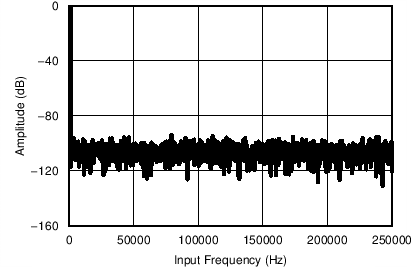

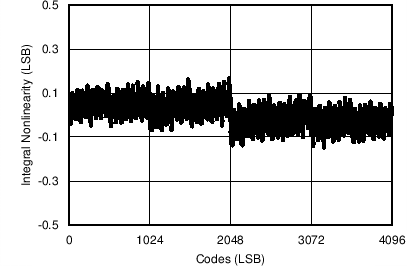

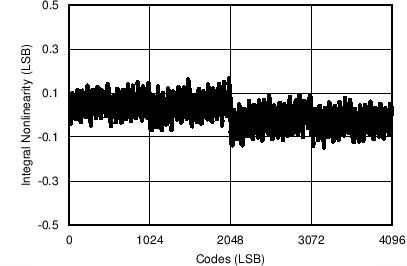

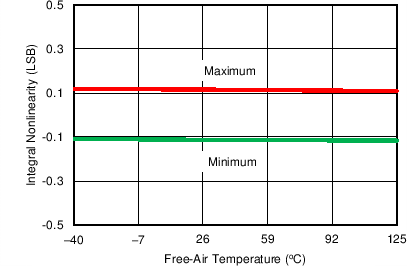

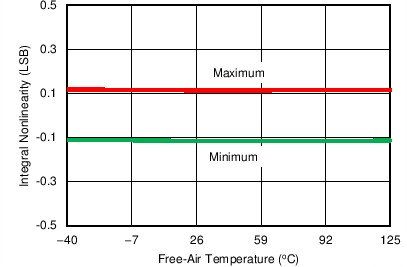

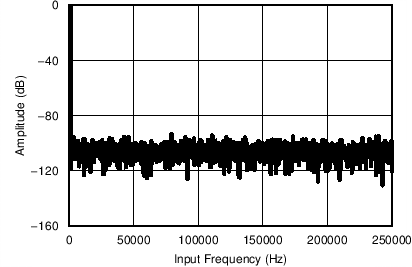

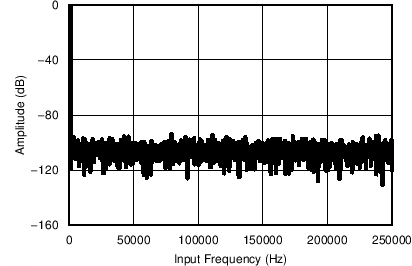

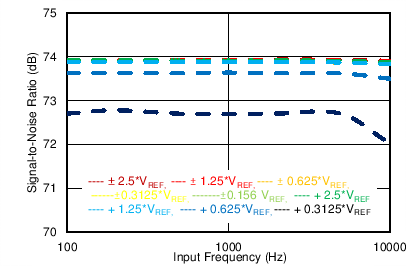

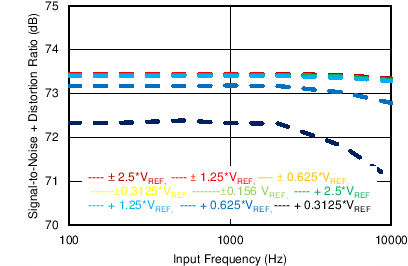

7.7 Typical Characteristics

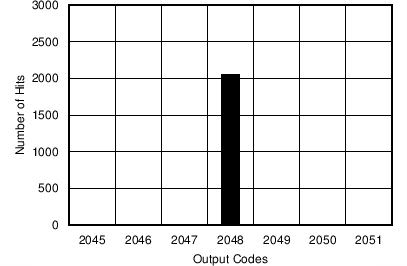

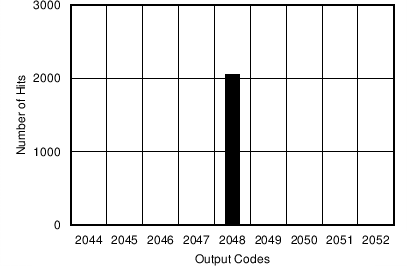

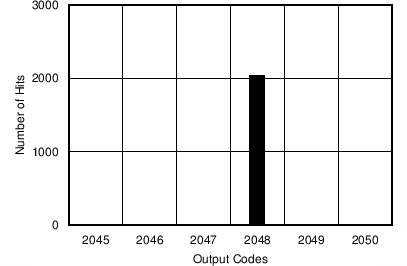

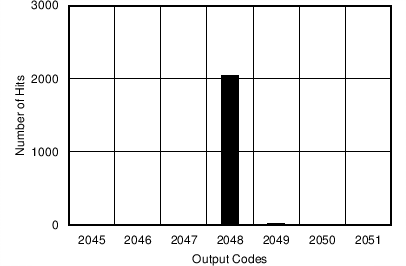

At TA = 25°C, AVDD = 5 V, DVDD = 3 V, internal reference VREF = 4.096 V, and fSAMPLE = 500 kSPS, unless otherwise noted.

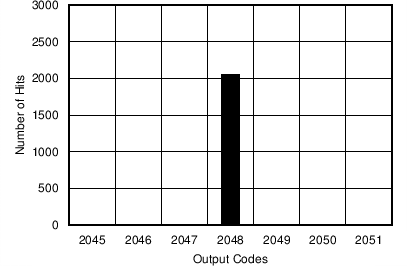

| Mean = 2048, sigma = 0.0, input = 0 V, range = ±2.5 × VREF |

| Mean = 2048, sigma = 0.1, input = 0 V, range = ±0.625 × VREF |

| Mean = 2048, sigma = 0.0, input = 0.625 × VREF, range = 1.25 × VREF |

(1.25 × VREF)

| Mean = 2048, sigma = 0.18, input = 0 V, range = ±0.15625 × VREF |

(±0.15625 x VREF)

| Mean = 2048, sigma = 0.18, input = 0.15625 × VREF, range = 0.3125 × VREF |

(0.3125 x VREF)

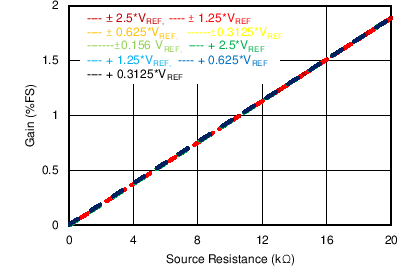

| All input ranges |

| Range = ±1.25 × VREF |

| Range = 2.5 × VREF |

| Range = ±0.3125 × VREF |

| Range = 0.625 × VREF |

| Range = ±2.5 × VREF |

| Range = ±0.625 × VREF |

| Range = 1.25 × VREF |

| Range = ±0.15625 × VREF |

| Range = 0.3125 × VREF |

| Range = ±2.5 × VREF |

| Range = ±2.5 × VREF |

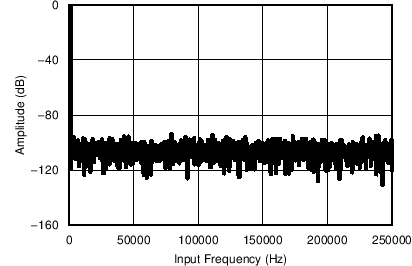

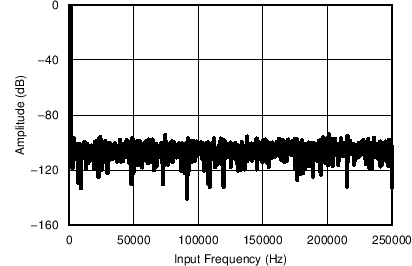

| Number of points = 4k, fIN = 1 kHz, SNR = 73.69 dB, SINAD = 73.69 dB, THD = –91.13 dB, SFDR = 94 dB |

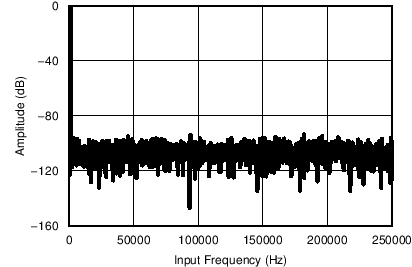

| Number of points = 4k, fIN = 1 kHz, SNR = 73.65 dB, SINAD = 73.64 dB, THD = –92.382 dB, SFDR = 94 dB |

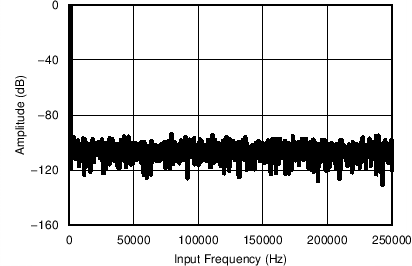

| Number of points = 4k, fIN = 1 kHz, SNR = 73.64 dB, SINAD = 73.64 dB, THD = –91.022 dB, SFDR = 94 dB |

| Number of points = 4k, fIN = 1 kHz, SNR = 72.57 dB, SINAD = 72.56 dB, THD = –92.382 dB, SFDR = 94 dB |

| Number of points = 4k, fIN = 1 kHz, SNR = 72.57 dB, SINAD = 72.56 dB, THD = –91.022 dB, SFDR = 94 dB |

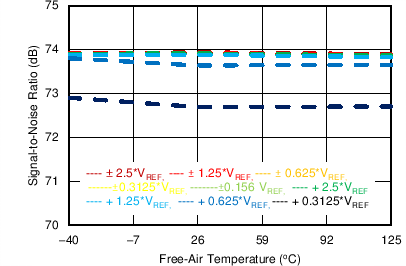

| fIN = 1 kHz |

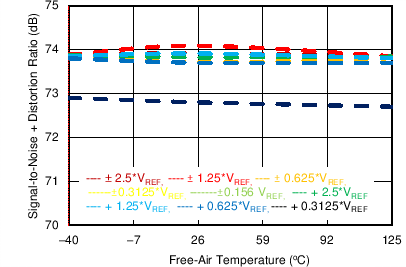

| fIN = 1 kHz |

| fIN = 1 kHz |

| Input = 2 × maximum input voltage |

Overrange Inputs

(During Sampling)

(During Sampling)

(Power Down)

| Input range = ±2.5 × VREF |

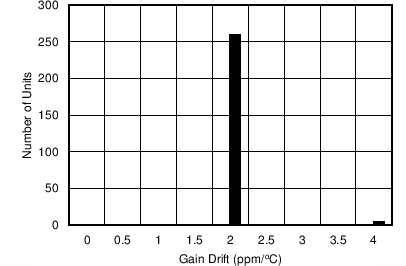

| Number of samples = 1160 |

| Mean = 2048, sigma = 0.0, input = 0 V, range = ±1.25 × VREF |

| Mean = 2048, sigma = 0.0, input = 1.25 × VREF, range = 2.5 × VREF |

| Mean = 2048, sigma = 0.1, input = 0 V, range = ±0.3125 × VREF |

(±0.3125 x VREF)

| Mean = 2048, sigma = 0.1, input = 0.3125 × VREF, range = 0.625 × VREF |

(0.625 x VREF)

| All input ranges | ||

| Range = ±2.5 × VREF |

| Range = ±0.625 × VREF |

| Range = 1.25 × VREF |

| Range = ±0.15625 × VREF |

| Range = 0.3125 × VREF |

| Range = ±1.25 × VREF |

| Range = 2.5 × VREF |

| Range = ±0.3125 × VREF |

| Range = 0.625 × VREF |

Temperature Across Input Ranges

| Range = ±2.5 × VREF |

| Range = ±2.5 × VREF |

| Number of points = 4k, fIN = 1 kHz, SNR = 73.68 dB, SINAD = 73.68 dB, THD = –92.34 dB, SFDR = 94 dB |

| Number of points = 4k, fIN = 1 kHz, SNR = 73.67 dB, SINAD = 73.67 dB, THD = –93.93 dB, SFDR = 94 dB |

| Number of points = 4k, fIN = 1 kHz, SNR = 73.44 dB, SINAD = 73.43 dB, THD = –92.382 dB, SFDR = 94 dB |

| Number of points = 4k, fIN = 1 kHz, SNR = 73.44 dB, SINAD = 73.43 dB, THD = –91.02 dB, SFDR = 94 dB |

| Input = 2 × maximum input voltage |

Overrange Inputs

(fS = 500 kSPS)

(fS = 500 kSPS)

(STANDBY)