ZHCT482 February 2024 UCC25600 , UCC25660

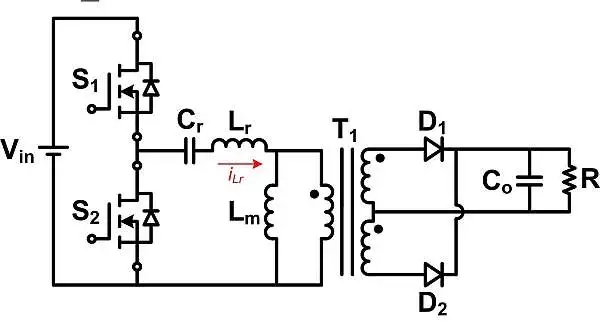

十几年来,电源行业广泛采用了图 1 中所示的电感器-电感器-电容器 (LLC) 串联谐振转换器 (LLC-SRC) 作为低成本、高效率的隔离式功率级,其中包含两个谐振电感器(两个“L”:Lm 和 Lr)和一个谐振电容器(一个“C”:Cr)。LLC-SRC 器件具有软开关特性,没有复杂的控制方案。得益于软开关特性,该器件支持使用额定电压较低的元件,并可提高效率。该器件采用简单的控制方案,即具有 50% 固定占空比的变频调制方案,与相移全桥转换器等用于其他软开关拓扑的控制器相比,所需的控制器成本更低。

图 1 LLC-SRC

图 1 LLC-SRC尽管 LLC-SRC 的效率可以比硬开关反激式和正激式转换器高很多,但如果要实现最佳的效率,仍然存在一些设计挑战。首先,在 LLC-SRC 设计中,为了实现足够宽的可控范围,两个谐振电感器之比 (Lm/Lr) 可能必须小于 10。同时,需要 Lm 具有较大的电感,以便降低循环电流,因此需要保持高 Lr 电感以确保谐振电感比值低。

值得注意的是,串联谐振电感器 Lr 中的电流完全是交流电,没有任何直流分量,这意味着磁通密度变化很大(即 ΔB 很高)。高 ΔB 意味着与交流相关的电感器损耗也很高。如果电感器绕在铁氧体磁芯上,磁芯空气间隙附近的边缘效应会产生较高的绕组损耗。

Lr 电感高,则意味着电感器匝数较多、交流绕组损耗较大。因此,许多 LLC-SRC 设计都对谐振电感器采用铁粉磁芯,在绕组损耗和磁芯损耗之间进行权衡。然而,高 ΔB 会在谐振电感器上产生相当大的损耗:高绕组损耗或高磁芯损耗。

LLC-SRC 设计的第二个挑战是如何合理优化同步整流器 (SR) 控制。LLC-SRC 整流器电流传导时序取决于负载条件和开关频率。最有前景的 LLC-SRC SR 控制方法是检测 SR 场效应晶体管 (FET) 漏源电压 (VDS),并在 VDS 低于或高于特定电平时开启和关闭 SR。VDS 检测方法需要毫伏级的精度,因此只能在集成电路中实现。自驱动或其他低成本 SR 控制方案不适用于 LLC-SRC,因为此类器件采用带电容负载的电流馈入型输出配置。因此,LLC-SRC SR 控制器电路的成本通常高于其他拓扑的成本。

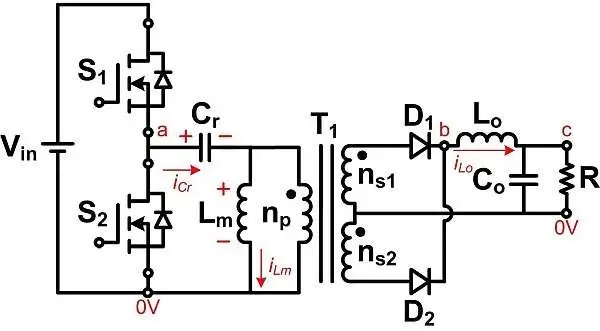

为了解决这两个挑战(高电感器损耗和 SR 控制),同时保持谐振转换器所能提供的大部分优势,请考虑使用改良版 CLL 多谐振转换器 (CLL-MRC),如图 2 所示。

图 2 改良版 CLL-MRC

图 2 改良版 CLL-MRC与所有三个谐振元件(一个电容器和两个电感器)都位于输入侧的 CLL-MRC 不同,改良版 CLL-MRC 将一个电感器从输入侧移动到输出侧,并将电感器放置在整流器 Lo 之后,如图 2 所示。这种修改允许谐振电感器上含有直流电流,这意味着 ΔB 更小,磁损耗也可能更低。

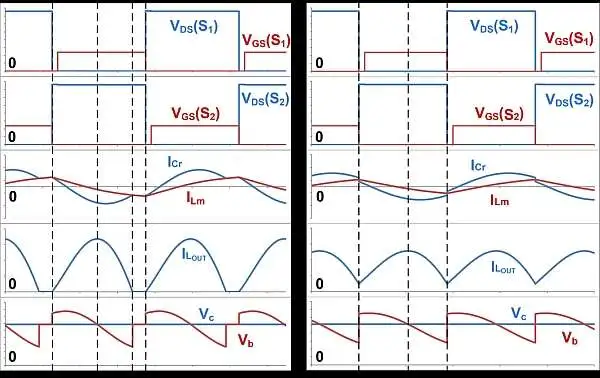

图 3 展示了改良版 CLL-MRC 的工作原理,其中 fsw 是转换器开关频率,而 fr1 = {2π[Cr (Lr1 //Lr2 )]0.5 } -1 是两个谐振频率的其中之一。当 fsw 低于 fr1 时,输出绕组电流在开关周期结束前下降到零,这一点与 LLC-SRC 中的输出绕组电流类似。现在,输出端有一个电感器。一组简单的电容器和电阻器即可检测输出电感器电压。每次出现较大的电压变化率 (dV/dt) 时,便是开启或关闭 SR 的时机。因此,SR 控制方案的成本低于 VDS 检测方案。

当 fsw 高于 fr1 时,输出电感器电流会处于连续导通模式。换言之,与 LLC-SRC 相比,ΔB 减小,电感器交流损耗可能大幅减小,转换器效率可能提高。

图 3 改良版 CLL-MRC 的重要波形:fsw < fr1(左),fsw > fr1(右)

图 3 改良版 CLL-MRC 的重要波形:fsw < fr1(左),fsw > fr1(右)为了验证这些性能假设,我构建了一个 LLC-SRC 和另一个具有完全相同元件和参数的改良版 CLL-MRC 功率级。两者唯一的区别是 72μH 电感器用作 LLC-SRC 谐振电感器,1μH 电感器用作改良版 CLL-MRC 输出电感器。

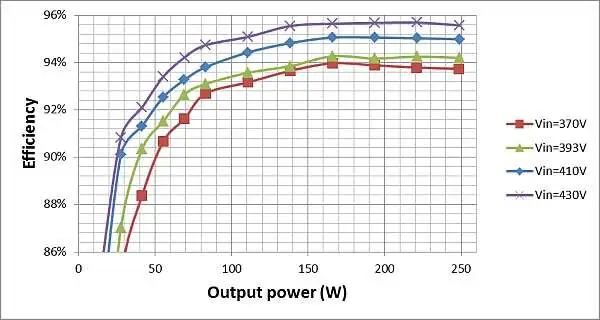

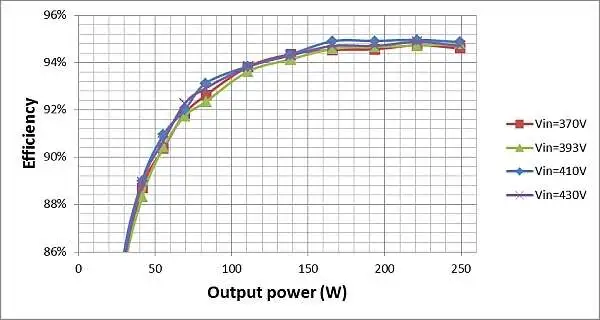

图 4 显示了两个功率级的效率测量结果。当输入电压较低时,fsw 小于 fr1,因此改良版 CLL-MRC 中的 Lo 电流仍处于不连续导通模式,并具有较大的 ΔB。因此,在这种运行条件下,改良版 CLL-MRC 没有效率优势。

当输入电压升高时,fsw 大于 fr1,Lo 电流处于连续导通模式。使用 430V 输入时,改良版 CLL-MRC 的效率比 LLC-SRC 高 1%。这一比较表明,如果将改良版 CLL-MRC 设计为始终在高于 fr1 的频率下运行,则其在整个范围内的效率性能可能优于 LLC-SRC。

图 4 不同输入电压电平下的转换器效率:改良版 CLL-MRC(顶部),LLC-SRC(底部)

图 4 不同输入电压电平下的转换器效率:改良版 CLL-MRC(顶部),LLC-SRC(底部)LLC-SRC 确实是出色的拓扑,可提供许多吸引人的特性。但根据应用的不同,其可能并不是最佳解决方案。为了实现更高的效率和更低的电路成本,有时需要跳出思维定式。

其他资源

- 阅读德州仪器 (TI) 电源设计研讨会的以下文章:

- “设计 LLC 谐振半桥电源转换器”。

- “谐振转换器拓扑结构综述”。

- “同步整流器的控制和设计挑战”。

- 查看 400V 直流输入转 28V/9A 输出、紧凑型高效 CLL 谐振转换器参考设计。

相关文章

- LLC resonant topology lowers switching losses, boosts efficiency

- High efficiency resonant mode implementation using digital control

- Design considerations when selecting half bridge resonant LLC converters and primary side MOSFETs

- Using quasi-resonant and resonant converters

- Power Tips #77: Designing a CCM flyback converter

之前发布在 EDN.com 上。