-

适用于 DLPR410 和 DLPR910 器件的 DLP 产品公告 ZHCT389 February 2023 DLP6500FLQ , DLP650LNIR , DLP7000 , DLP7000UV , DLP9000X , DLP9000XUV , DLP9500 , DLP9500UV , DLPC410 , DLPC910

ERRATA

适用于 DLPR410 和 DLPR910 器件的 DLP 产品公告

本资源的原文使用英文撰写。 为方便起见,TI 提供了译文;由于翻译过程中可能使用了自动化工具,TI 不保证译文的准确性。 为确认准确性,请务必访问 ti.com 参考最新的英文版本(控制文档)。

摘要

AMD Xilinx 已停止生产 XCF16P 配置 PROM,它用作以下 TI 器件的基底器件:2510442-0005、DLPR410YVA、DLPR410AYVA、DLPR410BYVA、DLPR910YVA、DLPR910AYVA。本文档详细介绍了德州仪器 (TI) 产品设计更新和支持。

1 受影响的产品

AMD Xilinx 已停止生产 XCF16P 配置 PROM,它用作以下 TI 器件的基底器件:

-

2510442-0005

-

DLPR410YVA

-

DLPR410AYVA

-

DLPR410BYVA

-

DLPR910YVA

-

DLPR910AYVA

2 主串行外设接口闪存配置方法

使用 DLPC910 或 DLPC410 控制器的产品设计需要进行更新,以实现 Xilinx 主串行外设接口 (SPI) 闪存配置方法。

3 SPI 闪存配置方法

请参阅以下 AMD Xilinx 信息,了解如何将 DLPC910 和 DLPC410 (Virtex-5 FPGA) 连接到 SPI 闪存以进行配置。

3.1 配置指南

Xilinx Virtex-5 配置指南:

3.2 FPGA 引脚排列信息

Xilinx Virtex-5 XC5VLX30FF676 FPGA 引脚排列信息:

http://www.xilinx.com/content/dam/xilinx/support/packagefiles/v5packages/5vlx30ff676.pkg.txt

3.3 支持 SPI 闪存配置方法的设计详细信息

通过 DLPC910 和 DLPC410 支持主串行外设接口 (SPI) 闪存配置的设计详细信息如下:

FPGA 控制器上的主串行外设接口闪存配置模式 M[2..0] 引脚必须更改为 M[2:0] = 001。

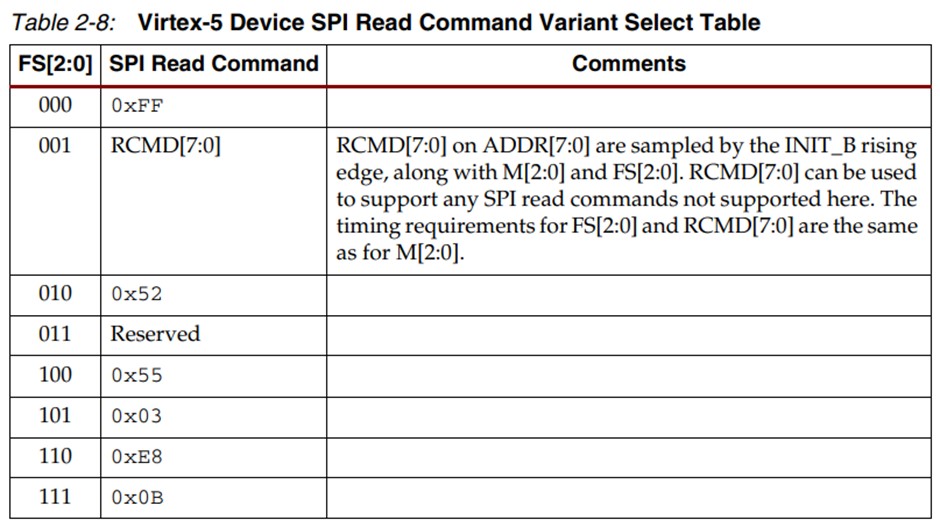

有关更多信息,请参阅 Xilinx Virtex-5 配置指南 UG191 的第 62 页:必须正确连接 FS[2:0] 引脚,以确定所选 SPI 闪存用于连接 FPGA 控制器的读取命令类型。下表(UG191 – Xilinx Virtex-5 配置指南中的表 2-8)描述了可用的选择:

FS2 = DLPC910 控制器和 DLPC410 控制器的引脚 AB11

FS1 = DLPC910 控制器和 DLPC410 控制器的引脚 AA13

FS0 = DLPC910 控制器和 DLPC410 控制器的引脚 AA14