ZHCSKH5C May 2008 – November 2019 DAC9881

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics: AVDD = 5 V

- 6.6 Electrical Characteristics: AVDD = 2.7 V

- 6.7 Timing Requirements—Standalone Operation Without SDO

- 6.8 Timing Requirements—Standalone Operation With SDO and Daisy-Chain Mode

- 6.9 Typical Characteristics: AVDD = 5 V

- 6.10 Typical Characteristics: AVDD = 2.7 V

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

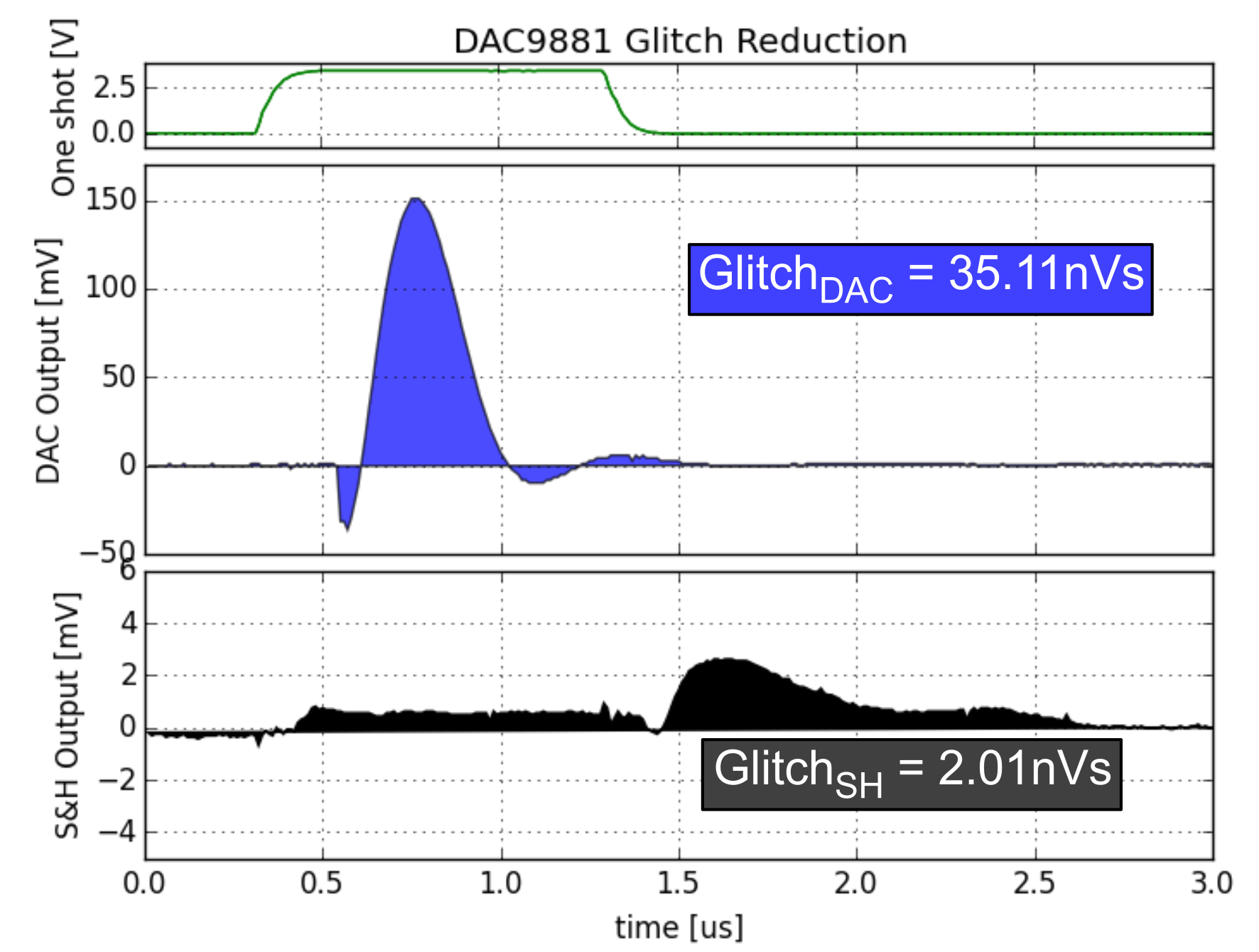

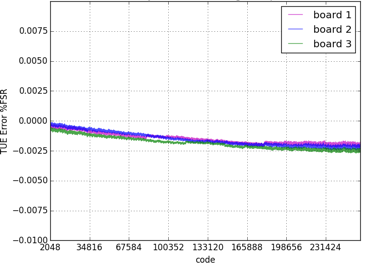

8.2.1.3 Application Curves

Glitch reduction and total unadjusted error (TUE) plots of the solution presented in Sample and Hold Glitch Reduction for Precision Outputs Design Guide (TIDU022) is shown in the following plots. The glitch area is reduced from 35.11 nVs to 2.01 nVs.

| CH = 8.2 nF | RS = 14.7 Ω |

(Top) Digital Signal One-Shot Pulse; (Middle) DAC Output Glitch; (Bottom) S-H Output Glitch