CC13x2x7, CC26x2x7 SimpleLink™ Wireless MCU

1 Read This First

This technical reference manual provides information about how to use the CC13x2x7 and CC26x2x7SimpleLink™ ultra-low power wireless microcontroller (MCU). The CC2652x7 and the CC13x2x7 device platforms share the same MCU architecture and most of the peripherals. The radio in the CC2652x7 device operates in the 2.4 GHz ISM frequency band, while the radio in the CC1312x7 device is designed for use in the Sub-1 GHz frequency bands. The CC1352x7 device is a multi-band wireless MCU and can operate both in the Sub-1 GHz and 2.4 GHz bands. This document covers the whole platform of devices, so refer to the individual device data sheets for supported modules and features.

About This Manual

This document is organized into sections that correspond to each major feature; it explains the features and functionality of each module and how to use them. For each feature, references are given to the driver documentation of the corresponding operating systems. Driver documentation does not contain performance characteristics for the device or modules, which are instead in the corresponding device data sheets. This manual is intended for system software developers, hardware designers, and application developers.

Devices

The CC13x2x7 and CC26x2x7 device platform includes both 2.4 GHz (CC2652x7 and CC1352x7) and Sub-1 GHz (CC1312x7) radios along with a variety of different memory sizes, peripherals, and package options. All devices are centered around an Arm®Cortex®-M4F series processor that handles the application layer and protocol stack, as well as an autonomous radio core centered around an Arm® Cortex®-M0 processor that handles all the low-level radio control and processing. Network processor options are available.

The availability of a wide range of different radio and MCU system combinations makes these device families very well suited for almost any low-power RF node implementation.

Register, Field, and Bit Calls

The naming convention applied for a call consists of:

- For a register call: <Module name>.<Register name>; for example: UART.UASR

- For a bit field call:

- <Module name>.<Register name>[End:Start] <Field name> field; for example, UART.UASR[4:0] SPEED bit field

- <Field name> field <Module name>.<Register name>[End:Start]; for example, SPEED bit field UART.UASR[4:0]

- For a bit call:

- <Module name>.<Register name>[pos] <Bit name> bit; for example, UART.UASR[5] BIT_BY_CHAR bit

- <Bit name> bit <Module name>.<Register name>[pos]; for example, BIT_BY_CHAR bit UART.UASR[5]

Related Documentation

The following related documents are available on the CC13x2x7 and CC26x2x7 device product pages at www.ti.com:

- CC1312x7:

- CC1312R7 data sheet and errata (Technical Documents)

- CC1352x7:

- CC1352P7 data sheet and errata (Technical Documents)

- CC2652x7:

- CC2652R7 data sheet and errata (Technical Documents)

- CC2652P7 data sheet and errata (Technical Documents)

- Cortex-M3/M4F Instruction Set Technical User's

ManualNote:

This list of documents was current as of publication date. Check the website for additional documentation, application notes, and white papers.

Additional, related documentation follows:

- The Institute of Electrical and Electronic Engineers, Inc., IEEE Standard Test Access Port and Boundary Scan Architecture, IEEE Std 1149.1a 1993 and Supplement Std. 1149.1b 1994 (see IEEExplore.ieee.org)

- The Institute of Electrical and Electronic Engineers, Inc., IEEE 1149.7 Standard for Reduced-Pin and Enhanced-Functionality Test Access Port and Boundary-Scan Architecture (see IEEExplore.ieee.org)

- National Institute of Standards and Technology, NIST Special Publication 800-38A, Recommendation for Block Cipher Modes of Operation Methods and Techniques (see NIST.gov)

- National Institute of Standards and Technology, NIST Special Publication 800-38D, Recommendation for Block Cipher Modes of Operation: Galois/Counter Mode (GCM) and GMAC (see NIST.gov)

- National Institute of Standards and Technology, FIPS 197, Advanced Encryption Standard (AES) (see NIST.gov)

- Bluetooth SIG, Inc., Bluetooth Specification versions 4.0, 4.1, 4.2, and 5.0 (see Bluetooth.com)

- Arm®v7-M Architecture Reference Manual (see Arm.com)

- Arm® Debug Interface V5 Architecture Specification (see Arm.com)

1.1 Trademarks

SimpleLink and EnergyTrace are trademarks of Texas Instruments.

CoreSight is a trademark of Arm Limited (or its subsidiaries).

Motorola is a trademark of Motorola Trademark Holdings, LLC.

Arm, Cortex, Thumb, Arm7, AMBA, and PrimeCell are registered trademarks of Arm Limited (or its subsidiaries).

Zigbee is a registered trademark of Zigbee Alliance.

All trademarks are the property of their respective owners.

2 Architectural Overview

The CC13x2x7 and CC26x2x7 device platform of the SimpleLink™ ultra-low-power wireless MCUs provides solutions for a wide range of applications. To help the user develop these applications, this user's guide focuses on the use of the different building blocks of the devices. For detailed device descriptions, complete feature lists, and performance numbers, see the data sheet for the specific device. The following subsections provide easy access to relevant information and guide the reader to the different chapters in this document.

The device platform system-on-chips (SoCs) are optimized for ultra-low power, while providing fast and capable MCU systems to enable short processing times and high integration. The combination of an Arm® Cortex®-M4F processing core up to 48 MHz, flash memory, and a wide selection of peripherals makes the CC13x2x7 and CC26x2x7 device platform specifically designed for single-chip implementation or network processor implementations of lower-power RF nodes.

2.1 Target Applications

The CC13x2x7 and CC26x2x7 SimpleLink™ ultra-low-power wireless MCU platform is positioned for low-power wireless applications, such as:

- Consumer electronics

- Mobile phone accessories

- Sports and fitness equipment

- HID applications

- Home and building automation

- Lighting control

- Alarm and security

- Electronic shelf labeling

- Proximity tags

- Medical

- Remote controls

- Smart metering

- Asset tracking

- Wireless sensor networks

2.2 Overview

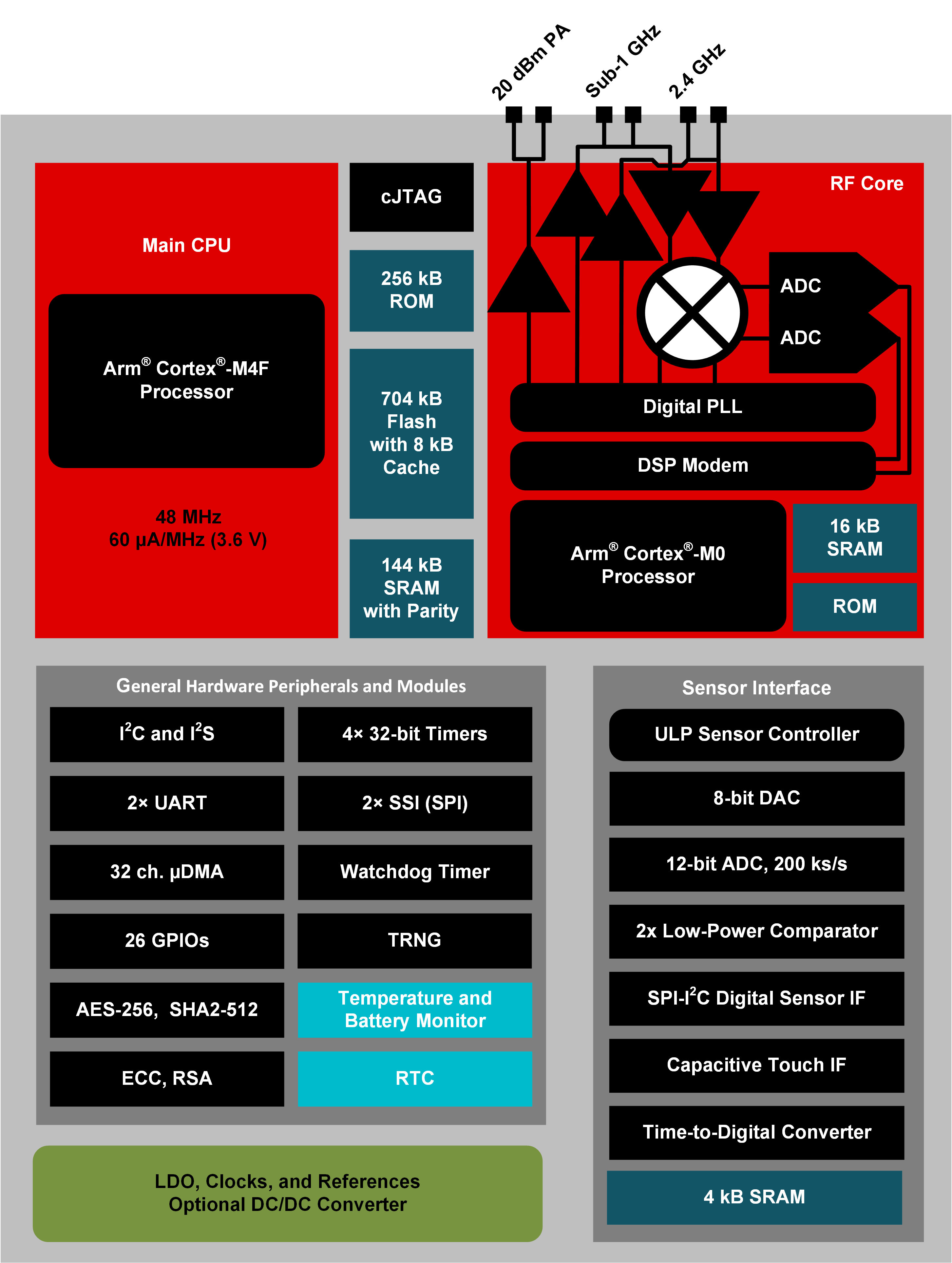

Figure 2-1 shows the building blocks of the CC13x2x7 and CC26x2x7 device platform.

The CC13x2x7 and CC26x2x7 device platform has the following features:

- Arm® Cortex®-M4F processor core

- 48 MHz RC oscillator and 48 MHz crystal oscillator

- 32 kHz crystal oscillator, 32 kHz RC oscillator, or low-power 48 MHz crystal derive clock for timing maintenance while in low-power modes

- Arm® Cortex® SysTick timer

- Nested vectored interrupt controller (NVIC)

- On-chip memory

- 704 kB of Flash with 8 kB of 4-way set-associative cache RAM for speed and low power

- 144 kB of System RAM with configurable retention in 16 kB blocks

- Power management

- Wide supply voltage range

- Efficient on-chip DC/DC converter for reduced power consumption

- High granularity clock gating and power gating of device parts

- Flexible frequency of operation

- Flexible low-power modes allowing low energy consumption in duty cycled applications

- Sensor interface

- Autonomous, intelligent sensor interface that can wake up independently of the System CPU system to perform sensor readings, collect data, and determine if the System CPU must be woken

- 12-bit analog-to-digital converter (ADC) with eight analog input channels

- Low-power analog comparator

- Serial communication interfaces

Figure 2-1 CC13x2x7 and

CC26x2x7 Block Diagram

Figure 2-1 CC13x2x7 and

CC26x2x7 Block Diagram- Advanced serial integration

- Universal asynchronous receiver/transmitter (UART)

- Inter-integrated circuit (I2C) module

- Synchronous serial interface modules (SSIs)

- Audio interface I2S module

- System integration

- Direct memory access (DMA) controller

- Four 32-bit timers (up to eight 16-bit) with pulse width modulation (PWM) capability and synchronization

- 32 kHz real-time clock (RTC)

- Watchdog timer

- On-chip temperature and supply voltage sensing

- GPIO with normal or high-drive capabilities

- GPIOs with analog capability for ADC and comparator

- Fully flexible digital pin muxing allows use as GPIO or any peripheral function

- IEEE 1149.7 compliant 2-pin cJTAG with legacy 1149.1 JTAG support

- 7-mm × 7-mm VQFN package

For applications requiring extreme conservation of power, the CC13x2x7 and CC26x2x7 device platform features a power-management system to efficiently power down the devices to a low-power state during extended periods of inactivity. A power-up and power-down sequencer, a 32-bit sleep timer (an RTC), with interrupt and 144 kB of ultra-low-leakage (ULL) RAM with retention in all power modes positions the MCU perfectly for battery applications.

In addition, the CC13x2x7 and CC26x2x7 device platform offers the advantages of the widely available development tools of Arm®, SoC infrastructure IP applications, and a large user community. Additionally, the microcontroller uses Arm Thumb®-compatible Thumb-2 instruction set to reduce memory requirements and, thereby, cost.

TI offers a complete solution to get to market quickly, with evaluation and development boards, white papers and application notes, an easy-to-use peripheral driver library, and a strong support, sales, and distributor network.

2.3 Functional Overview

The following subsections provide an overview of the features of the CC13x2x7 and CC26x2x7 device platform.

2.3.1 Arm® Cortex®-M4F

The following subsections provide an overview of the Arm® Cortex®-M4F processor core and instruction set, the integrated system timer (SysTick), and the NVIC.

2.3.1.1 Processor Core

The CC13x2x7 and CC26x2x7 device platform is designed around an Arm® Cortex®-M4F processor core. The Arm® Cortex®-M4F processor provides the core for a high-performance, low-cost platform that meets the needs of minimal memory implementation, reduced pin count, and low power consumption, while delivering outstanding computational performance and exceptional system response to interrupts.

Features of the processor core are as follows:

- 32-bit Arm® Cortex®-M4F architecture optimized for small-footprint embedded applications

- Outstanding processing performance combined with fast interrupt handling

- Thumb-2 mixed 16- and 32-bit instruction set delivers the high performance expected of a 32-bit Arm® core in a compact memory size, usually associated with 8- and 16-bit devices, typically in the range of a few kilobytes of memory for microcontroller-class applications.

- Single-cycle multiply instruction and hardware divide

- Atomic bit manipulation (bit-banding), delivering maximum memory use and streamlined peripheral control

- Unaligned data access, enabling efficient packing of data into memory

- Fast code execution permits slower processor clock or increases sleep mode time

- Harvard architecture characterized by separate buses for instruction and data

- Efficient processor core, system, and memories

- Hardware division and fast multiplier

- Deterministic, high-performance interrupt handling for time-critical applications

- Enhanced system debug with extensive breakpoint capabilities and debugging through power modes

- Compact JTAG interface reduces the number of pins required for debugging

- Ultra-low power consumption with integrated sleep modes

- Up to 48 MHz operation

2.3.1.2 System Timer (SysTick)

The Arm® Cortex®-M4F processor includes an integrated system timer (SysTick). SysTick provides a simple, 24-bit, clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism. The counter can be used in several different ways; for example:

- An RTOS tick timer that fires at a programmable rate (for example, 100 Hz) and invokes a SysTick routine

- A high-speed alarm timer using system clock 11

- A variable rate alarm or signal timer—the duration is range-dependent on the reference clock used and the dynamic range of the counter

- A simple counter used to measure time to completion and time used

- An internal clock-source control based on missing or meeting durations

2.3.1.3 Nested Vector Interrupt Controller (NVIC)

The CC13x2x7 and CC26x2x7 device controller includes the Arm® NVIC. The NVIC and Arm® Cortex®-M4F prioritize and handle all exceptions in handler mode. The processor state is automatically stored to the stack on an exception and automatically restored from the stack at the end of the interrupt service routine (ISR). The interrupt vector is fetched in parallel to state saving, thus enabling efficient interrupt entry. The processor supports tail-chaining, that is, back-to-back interrupts can be performed without the overhead of state saving and restoration. Software can set eight priority levels on seven exceptions (system handlers) and can set device interrupts.

Features of the NVIC are as follows:

- Deterministic, fast interrupt processing

- Always 12 cycles, or just 6 cycles with tail-chaining

- External nonmaskable interrupt (NMI) signal available for immediate execution of NMI handler for safety-critical applications

- Dynamically reprioritizable interrupts

- Exceptional interrupt handling through hardware implementation of required register manipulations

2.3.1.4 System Control Block

The system control block (SCB) provides system implementation information and system control (configuration, control, and reporting of system exceptions).

2.3.2 On-Chip Memory

The following subsections describe the on-chip memory modules.

2.3.2.1 SRAM

The CC13x2x7 and CC26x2x7 device platform provides 144 kB of low-leakage, on-chip SRAM with optional retention in all power modes. Retention can be configured per 16 kB block. Additionally, the 8 kB flash cache RAM can be reconfigured to operate as normal system RAM. Because read-modify-write (RMW) operations are very time consuming, Arm® has introduced bit-banding technology in the Arm® Cortex®-M4F processor. With a bit-band-enabled processor, certain regions in the memory map (SRAM and peripheral space) can use address aliases to access individual bits in a single, atomic operation.

Data can be transferred to and from the SRAM using the micro DMA (µDMA) controller.

2.3.2.2 Flash Memory

The flash block provides an in-circuit, programmable, nonvolatile program memory for the device. The 704 kB flash memory is organized as a set of 8 kB pages that can be individually erased. Erasing a block causes the entire contents of the block to be reset to all 1s. These pages can be individually protected. Read-only blocks cannot be erased or programmed, protecting the contents of those blocks from being modified. In addition to holding program code and constants, the nonvolatile memory allows the application to save data that must be preserved so that it is available after restarting the device. Using this feature lets the user use saved network-specific data to avoid the need for a full start-up and network find-and-join process.

2.3.2.3 ROM

The ROM is preprogrammed with a boot sequence, device driver functions, low-level protocol stack components, and a serial bootloader (SPI or UART).

2.3.3 Radio

The CC2652x7 device provides a highly integrated low-power 2.4 GHz radio transceiver with support for multiple modulations and packet formats. The CC1312x7 device provides similar functionality optimized for the Sub-1 GHz bands. The CC1352x7 device is a true dual-band radio with separate RF paths for Sub-1 GHz and 2.4 GHz operation. The radio subsystem provides an interface between the MCU and the radio, which makes it possible to issue commands, read status, also automate and sequence radio events.

2.3.4 Security Core

The security core of the CC13x2x7 and CC26x2x7 device platform features an Advanced Encryption Standard (AES) module with 256-bit key support, local key storage and DMA capability. It also includes a Hash engine (SHA-2) and a Public Key Acceleration (PKA) engine.

Features of the AES engine are as follows:

- ECB, CBC, CBC-MAC, CTR, CCM, and GCM modes of operation

- 118 Mbps throughput

- Secure key storage memory

- Low latency

- SHA-224, SHA-256, SHA-384, and SHA-512

- Hardware accelerators for elliptic curve calculations

2.3.5 General-Purpose Timers

General-purpose timers can be used to count or time external events that drive the timer-input pins. Each 16- or 32-bit GPTM block provides two 16-bit timers or counters that can be configured to operate independently as timers or event counters, or configured to operate as one 32-bit timer.

The general-purpose timer module (GPTM) contains four 16- or 32-bit GPTM blocks with the following functional options:

- 16- or 32-bit operating modes:

- 16- or 32-bit programmable one-shot timer

- 16- or 32-bit programmable periodic timer

- 16-bit general-purpose timer with an 8-bit prescaler

- 16-bit input-edge count- or time-capture modes with an 8-bit prescaler

- 16-bit PWM mode with an 8-bit prescaler and software-programmable output inversion of the PWM signal

- Count up or down

- Four 32-bit counters or up to eight 16-bit counters

- Up to eight capture/compare pins

- Up to four PWM pins (one PWM pin per 32-bit timer)

- Daisy-chaining of timer modules allows a single timer to initiate multiple timing events

- Timer synchronization allows selected timers to start counting on the same clock cycle

- User-enabled stalling when the microcontroller asserts CPU halt flag during debug

- Ability to determine the elapsed time between the assertion of the timer interrupt and entry into the ISR

- Efficient transfers using the µDMA controller

2.3.5.1 Watchdog Timer

The watchdog timer is used to regain control when the system fails because of a software error or an external device fails to respond properly. The watchdog timer can generate an interrupt or a reset when a predefined time-out value is reached.

2.3.5.2 Always-On Domain

The AON domain contains circuitry that is always enabled, except for the shutdown mode (where the digital supply is off). This domain includes the following:

- The RTC can be used to wake the CC13x2x7 and CC26x2x7 device platform from any state where it is active. The RTC contains three match registers and one compare register. With software support, the RTC can be used for clock and calendar operation. The RTC is clocked from the 32 kHz RC oscillator or the 32 kHz crystal oscillator.

- The battery monitor and temperature sensors are accessible by software. The battery monitor and temperature sensors provide continuous monitoring of battery state as well as coarse temperature.

2.3.6 Direct Memory Access

The CC13x2x7 and CC26x2x7 device platform includes a DMA controller, known as μDMA. The μDMA controller provides a way to offload data transfer tasks from the Arm® Cortex®-M4F processor, allowing more efficient use of the processor and the available bus bandwidth. The μDMA controller can perform transfers between memory and peripherals. Channels in the μDMA are dedicated for each supported on-chip module and can be programmed to automatically perform transfers between peripherals and memory, because the peripheral is ready to transfer more data.