-

Manufacturing and Rework Design Guide for MicroSiP Power Modules SLIB006A February 2011 – June 2021 TPS81256 , TPS82084 , TPS82085 , TPS82130 , TPS82140 , TPS82150 , TPS82670 , TPS82671 , TPS826711 , TPS826716 , TPS82672 , TPS826721 , TPS82673 , TPS82674 , TPS826745 , TPS82675 , TPS82676 , TPS826765 , TPS82677 , TPS8268090 , TPS8268105 , TPS8268120 , TPS8268150 , TPS8268180 , TPS82692 , TPS82693 , TPS82695 , TPS826951 , TPS82697 , TPS82698 , TPS82740A , TPS82740B , TPSM82810 , TPSM82813 , TPSM82816 , TPSM82821 , TPSM82821A , TPSM82822 , TPSM82822A , TPSM82823 , TPSM82823A

-

Manufacturing and Rework Design Guide for MicroSiP Power Modules

Manufacturing and Rework Design Guide for MicroSiP Power Modules

1 Introduction

As the marketplace continues to demand size reductions in electronic products, the need for smaller packaging and smaller subsystem packaging becomes paramount. To address these rapidly evolving customer requirements, TI has developed MicroSiP™ power modules, an innovation in System-in-Package (SiP) technology to integrate both the IC and passive components into a single device.

With this technology, TI reaches the smallest solution size and highest levels of integration. This enables an easy-to-use power module for achieving the shortest time-to-market. As with any device package, attention must be given to the printed circuit board (PCB) layout, surface mount (SMT) assembly flow, and rework process. This white paper provides guidelines on each of these aspects, and these guidelines are achievable through normal manufacturing and rework flows.

2 MicroSiP Package

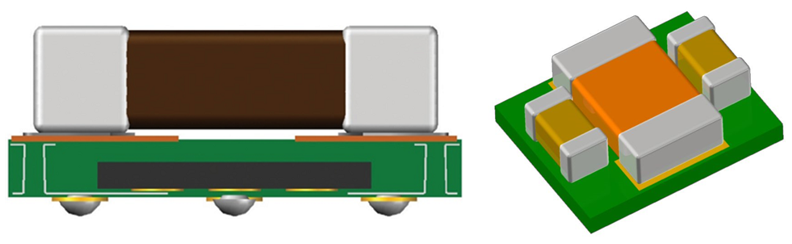

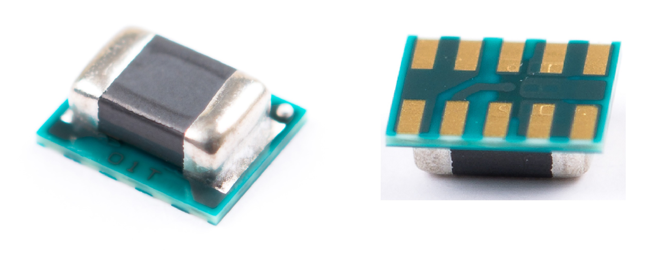

Within the MicroSiP family, there are two variations: MicroSiP (µSiP) and MicroSiL (µSiL). MicroSiP devices contain both the power inductor and one or more capacitors and typically use ball grid array (BGA) pins. MicroSiL devices contain just the power inductor and typically use land grid array (LGA) pins. The pin type difference creates different land pattern recommendations, but the SMT and rework guidelines remain the same for both packages. Figure 2-1 shows a typical MicroSiP with BGA pins, while Figure 2-2 shows a typical MicroSiL with LGA pins.

Figure 2-1 MicroSiP™ Package Integrates the Power Inductor and Two Capacitors and Uses BGA Pins

Figure 2-2 MicroSiL Package Integrates the Power Inductor and Uses LGA Pins

3 PCB Layout

3.1 MicroSiP With BGA Pins

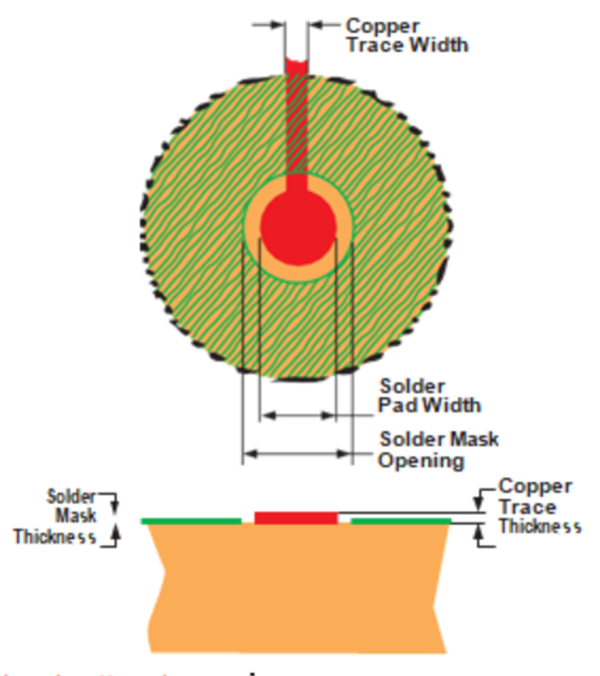

When designing the pads for MicroSiP devices with BGA pins, it is recommended that the layout use a non-solder mask defined (NSMD) pad. With this method, the solder mask opening is made larger than the desired land area, and the resulting copper size is defined solely by the size of the land pad of the device. Table 3-1 shows the appropriate pad design for MicroSiP™ devices with BGA pins. Specific recommendations are listed here and shown in Figure 3-1:

- Circuit traces from the NSMD PCB pads should be 75-µm to 100-µm wide in the exposed area inside the solder mask opening. Wider trace widths reduce device standoff, which worsens board level reliability (BLR).

- Best BLR results are achieved when the PCB laminate glass transition temperature is above the operating range of the application

- Recommended solder paste is Type 3 or Type 4

- For a PCB using a Ni/Au surface finish, the gold thickness should be less than 0.5 µm to avoid a reduction in thermal fatigue performance

- Solder mask thickness should be less than 20 µm on top of the copper circuit pattern, to increase device standoff and improve BLR

- Best solder stencil performance is achieved using laser cut stencils with electro-polishing. Use of chemically etched stencils gives inferior solder paste volume control.

| Land Pattern Dimensions | |||||

|---|---|---|---|---|---|

| Solder Pad Type | Land Pad Width | Solder Mask Opening | Copper Thickness | Stencil Opening | Stencil Thickness |

| Non-solder mask defined (NSMD) | 0.30 mm | 0.360 mm | 1 oz max (0.032 mm) | 0.34 mm diameter | 0.1 mm |

Figure 3-1 Recommended Pad Design for MicroSiP™ Devices With BGA Pins

See the device data sheet for specific recommendations.

3.2 MicroSiL With LGA Pins

When designing the pads for the MicroSiL devices with LGA pins, SMD pads are usually recommended over NSMD pads. With a power module, some pins (such as VIN, VOUT, and GND) are typically connected to large copper planes to carry the current and heat away from the device. Such copper planes grow the pad size of a NSMD pad, which then thins the solder paste thickness. Using SMD pads keeps each pad the same size and avoids solder pulling the device during reflow. See the device data sheet for specific recommendations.