ZHCSG16A January 2017 – May 2017 LMK61E0M

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics - Power Supply

- 6.6 3.3-V LVCMOS Output Characteristics

- 6.7 OE Input Characteristics

- 6.8 ADD Input Characteristics

- 6.9 Frequency Tolerance Characteristics

- 6.10 Frequency Margining Characteristics

- 6.11 Power-On/Reset Characteristics (VDD)

- 6.12 I2C-Compatible Interface Characteristics (SDA, SCL)

- 6.13 Other Characteristics

- 6.14 PLL Clock Output Jitter Characteristics

- 6.15 Additional Reliability and Qualification

- 6.16 Typical Characteristics

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Device Block-Level Description

- 8.3.2 Device Configuration Control

- 8.3.3 Register File Reference Convention

- 8.3.4 Configuring the PLL

- 8.3.5 Integrated Oscillator

- 8.3.6 Reference Divider and Doubler

- 8.3.7 Phase Frequency Detector

- 8.3.8 Feedback Divider (N)

- 8.3.9 Fractional Engine

- 8.3.10 Charge Pump

- 8.3.11 Loop Filter

- 8.3.12 VCO Calibration

- 8.3.13 High-Speed Output Divider

- 8.3.14 High-Speed Clock Output

- 8.3.15 Device Status

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Maps

- 8.6.1

Register Descriptions

- 8.6.1.1 VNDRID_BY1 Register; R0

- 8.6.1.2 VNDRID_BY0 Register; R1

- 8.6.1.3 PRODID Register; R2

- 8.6.1.4 REVID Register; R3

- 8.6.1.5 SLAVEADR Register; R8

- 8.6.1.6 EEREV Register; R9

- 8.6.1.7 DEV_CTL Register; R10

- 8.6.1.8 XO_CAPCTRL_BY1 Register; R16

- 8.6.1.9 XO_CAPCTRL_BY0 Register; R17

- 8.6.1.10 CMOSCTL Register; R20

- 8.6.1.11 DIFFCTL Register; R21

- 8.6.1.12 OUTDIV_BY1 Register; R22

- 8.6.1.13 OUTDIV_BY0 Register; R23

- 8.6.1.14 RDIVCMOSCTL Register; R24

- 8.6.1.15 PLL_NDIV_BY1 Register; R25

- 8.6.1.16 PLL_NDIV_BY0 Register; R26

- 8.6.1.17 PLL_FRACNUM_BY2 Register; R27

- 8.6.1.18 PLL_FRACNUM_BY1 Register; R28

- 8.6.1.19 PLL_FRACNUM_BY0 Register; R29

- 8.6.1.20 PLL_FRACDEN_BY2 Register; R30

- 8.6.1.21 PLL_FRACDEN_BY1 Register; R31

- 8.6.1.22 PLL_FRACDEN_BY0 Register; R32

- 8.6.1.23 PLL_MASHCTRL Register; R33

- 8.6.1.24 PLL_CTRL0 Register; R34

- 8.6.1.25 PLL_CTRL1 Register; R35

- 8.6.1.26 PLL_LF_R2 Register; R36

- 8.6.1.27 PLL_LF_C1 Register; R37

- 8.6.1.28 PLL_LF_R3 Register; R38

- 8.6.1.29 PLL_LF_C3 Register; R39

- 8.6.1.30 PLL_CALCTRL Register; R42

- 8.6.1.31 NVMSCRC Register; R47

- 8.6.1.32 NVMCNT Register; R48

- 8.6.1.33 NVMCTL Register; R49

- 8.6.1.34 MEMADR Register; R51

- 8.6.1.35 NVMDAT Register; R52

- 8.6.1.36 RAMDAT Register; R53

- 8.6.1.37 NVMUNLK Register; R56

- 8.6.1.38 INT_LIVE Register; R66

- 8.6.1.39 SWRST Register; R72

- 8.6.1

Register Descriptions

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| VDD | Device supply voltage | –0.3 | 3.6 | V |

| VIN | Input voltage range for logic inputs | –0.3 | VDD + 0.3 | V |

| VOUT | Output voltage range for clock outputs | –0.3 | VDD + 0.3 | V |

| TJ | Junction temperature | 150 | °C | |

| TSTG | Storage temperature | –40 | 125 | °C |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | |||

(1) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| VDD | Device supply voltage | 3.135 | 3.3 | 3.465 | V |

| TA | Ambient temperature | –40 | 25 | 85 | °C |

| TJ | Junction temperature | 115 | °C | ||

| tRAMP | VDD power-up ramp time | 0.1 | 100 | ms | |

6.4 Thermal Information

| THERMAL METRIC(1) | LMK61E0 (2) (3) (4) | UNIT | |||

|---|---|---|---|---|---|

| SIA (QFM) | |||||

| 8 PINS | |||||

| Airflow (LFM) 0 | Airflow (LFM) 200 | Airflow (LFM) 400 | |||

| RθJA | Junction-to-ambient thermal resistance | 54 | 44 | 41.2 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 34 | n/a | n/a | °C/W |

| RθJB | Junction-to-board thermal resistance | 36.7 | n/a | n/a | °C/W |

| ψJT | Junction-to-top characterization parameter | 11.2 | 16.9 | 21.9 | °C/W |

| ψJB | Junction-to-board characterization parameter | 36.7 | 37.8 | 38.9 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | n/a | n/a | n/a | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) The package thermal resistance is calculated on a 4-layer JEDEC board.

(3) Connected to GND with 3 thermal vias (0.3-mm diameter).

(4) ψJB (junction-to-board) is used when the main heat flow is from the junction to the GND pad. See Layout Guidelines for more information on ensuring good system reliability and quality.

6.5 Electrical Characteristics - Power Supply(1)

VDD = 3.3 V ± 5%, TA = –40°C to 85°C| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| IDD | Device current consumption | LVCMOS | 140 | 180 | mA | |

| IDD-PD | Device current consumption when output is disabled | OE = GND | 120 | mA | ||

(1) Refer to Parameter Measurement Information for relevant test conditions.

6.6 3.3-V LVCMOS Output Characteristics(1)

VDD = 3.3 V ± 5%, TA = –40°C to 85°C, outputs loaded with 2 pF to GND| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| fOUT | Output frequency | Fast mode, R22[7:6] = 0x0 | 50 | 200 | MHz | |

| VOH | Output high voltage | IOH = 1 mA | 2.5 | V | ||

| VOL | Output low voltage | IOL = 1 mA | 0.6 | V | ||

| IOH | Output high current | –33 | mA | |||

| IOL | Output low current | 33 | mA | |||

| tR/tF(2) | Output rise/fall time | 20% to 80%, R22[7:6] = 0x2 | 1.1 | ns | ||

| 20% to 80%, R22[7:6] = 0x0 | 0.2 | ns | ||||

| PN-Floor | Output phase noise floor (fOFFSET > 10 MHz) | 70.656 MHz | –150 | dBc/Hz | ||

| ODC(2) | Output duty cycle | Fast mode, R22[7:6] = 0x0 | 45% | 55% | ||

| ROUT | Output impedance | 50 | Ω | |||

(1) Refer to Parameter Measurement Information for relevant test conditions.

(2) Ensured by characterization.

6.7 OE Input Characteristics

VDD = 3.3 V ± 5%, TA = –40°C to 85°C| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VIH | Input high voltage | 1.4 | V | |||

| VIL | Input low voltage | 0.6 | V | |||

| IIH | Input high current | VIH = VDD | –40 | 40 | µA | |

| IIL | Input low current | VIL = GND | –40 | 40 | µA | |

| CIN | Input capacitance | 2 | pF | |||

6.8 ADD Input Characteristics

VDD = 3.3 V ± 5%, TA = –40°C to 85°C| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VIH | Input high voltage | 1.4 | V | |||

| VIL | Input low voltage | 0.4 | V | |||

| IIH | Input high current | VIH = VDD | –40 | 40 | µA | |

| IIL | Input low current | VIL = GND | –40 | 40 | µA | |

| CIN | Input capacitance | 2 | pF | |||

6.9 Frequency Tolerance Characteristics(1)

VDD = 3.3 V ± 5%, TA = –40°C to 85°C

(1) Ensured by characterization.

6.10 Frequency Margining Characteristics

VDD = 3.3 V ± 5%, TA = –40°C to 85°C| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| fT | Frequency margining range from nominal | –1000 | 1000 | ppm | ||

6.11 Power-On/Reset Characteristics (VDD)

VDD = 3.3 V ± 5%, TA = –40°C to 85°C| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VTHRESH | Threshold voltage(1) | 2.72 | 2.95 | V | ||

| VDROOP | Allowable voltage droop(2) | 0.1 | V | |||

| tSTARTUP | Start-up time(1) | Time elapsed from VDD at 3.135 V to output enabled | 10 | ms | ||

| tOE-EN | Output enable time(2) | Time elapsed from OE at VIH to output enabled | 50 | µs | ||

| tOE-DIS | Output disable time(2) | Time elapsed from OE at VIL to output disabled | 50 | µs | ||

(1) Ensured by characterization.

(2) Ensured by design.

6.12 I2C-Compatible Interface Characteristics (SDA, SCL)(1)(2)

VDD = 3.3 V ± 5%, TA = –40°C to 85°C| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VIH | Input high voltage | 1.2 | V | |||

| VIL | Input low voltage | 0.6 | V | |||

| IIH | Input leakage | –40 | 40 | µA | ||

| CIN | Input capacitance | 2 | pF | |||

| COUT | Input capacitance | 400 | pF | |||

| VOL | Output low voltage | IOL = 3 mA | 0.6 | V | ||

| fSCL | I2C clock rate | 100 | 1000 | kHz | ||

| tSU_STA | START condition setup time | SCL high before SDA low | 0.6 | µs | ||

| tH_STA | START condition hold time | SCL low after SDA low | 0.6 | µs | ||

| tPH_SCL | SCL pulse width high | 0.6 | µs | |||

| tPL_SCL | SCL pulse width low | 1.3 | µs | |||

| tH_SDA | SDA hold time | SDA valid after SCL low | 0 | 0.9 | µs | |

| tSU_SDA | SDA setup time | 115 | ns | |||

| tR_IN / tF_IN | SCL/SDA input rise and fall time | 300 | ns | |||

| tF_OUT | SDA output fall time | CBUS = 10 pF to 400 pF | 250 | ns | ||

| tSU_STOP | STOP condition setup time | 0.6 | µs | |||

| tBUS | Bus free time between STOP and START | 1.3 | µs | |||

(1) Total capacitive load for each bus line ≤ 400 pF.

(2) Ensured by design.

6.13 Other Characteristics

VDD = 3.3 V ± 5%, TA = –40°C to 85°C| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| fVCO | VCO frequency range | 4.6 | 5.6 | GHz | ||

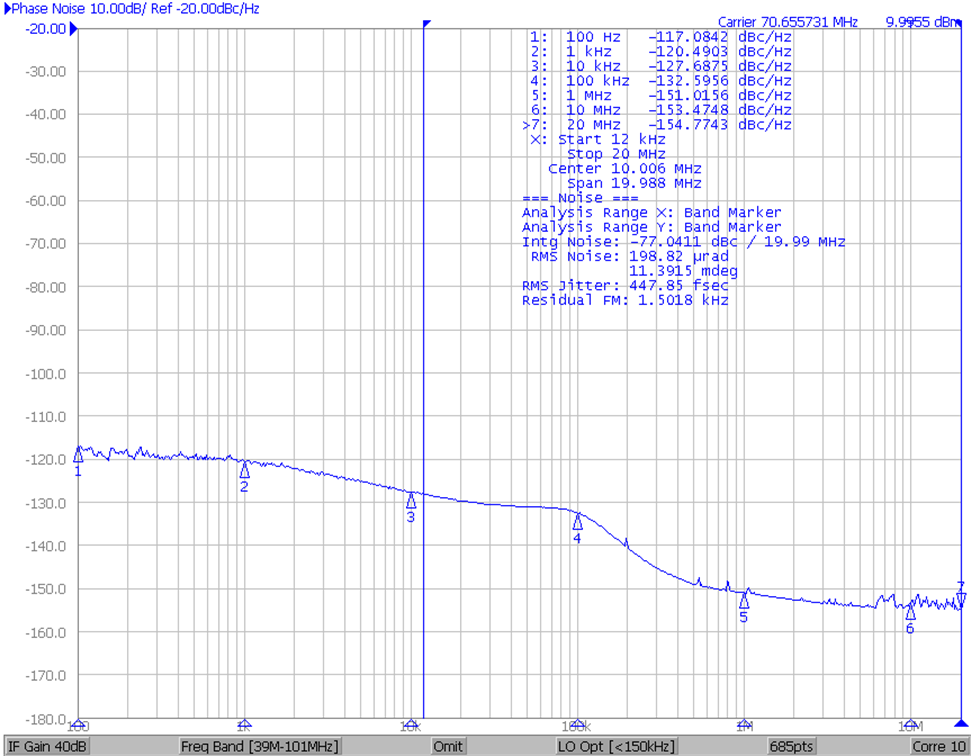

6.14 PLL Clock Output Jitter Characteristics(1)(3)

VDD = 3.3 V ± 5%, TA = –40°C to 85°C| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| RJ | RMS phase jitter(2)

(12 kHz – 20 MHz) |

fOUT ≥ 50 MHz, Fractional-N PLL, LVCMOS output | 500 | 1000 | fs RMS | |

(1) Refer to Parameter Measurement Information for relevant test conditions.

(2) Ensured by characterization.

(3) Phase jitter measured with Agilent E5052 signal source analyzer.

6.15 Additional Reliability and Qualification

| PARAMETER | CONDITION / TEST METHOD |

|---|---|

| Mechanical Shock | MIL-STD-202, Method 213 |

| Mechanical Vibration | MIL-STD-202, Method 204 |

| Moisture Sensitivity Level | J-STD-020, MSL3 |

6.16 Typical Characteristics

Figure 1. Typical Phase Noise of LVCMOS Output at 70.656 MHz

Figure 1. Typical Phase Noise of LVCMOS Output at 70.656 MHz