SLAS564G August 2007 – October 2016 CDCE937 , CDCEL937

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

9 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

9.1 Application Information

The CDCEx937 device is an easy-to-use, high-performance, programmable CMOS clock synthesizer. It can be used as a crystal buffer, clock synthesizer with separate output supply pin. The CDCEx937 features an on-chip loop filter and spread-spectrum modulation. Programming can be done through SPI, pin-mode, or using on-chip EEPROM. The following section shows some examples of using CDCEx937 in various applications.

9.2 Typical Application

Figure 14 shows the use of the CDCEx937 devices for replacement of crystals and crystal oscillators on a Gigabit Ethernet Switch application.

Figure 14. Crystal and Oscillator Replacement Example

Figure 14. Crystal and Oscillator Replacement Example

9.2.1 Design Requirements

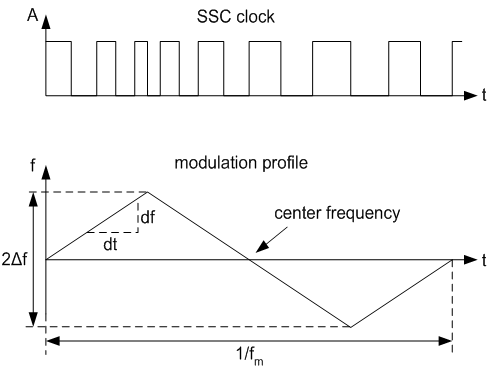

CDCEx937 supports spread-spectrum clocking (SSC) with multiple control parameters:

- Modulation amount (%)

- Modulation frequency (>20 kHz)

- Modulation shape (triangular)

- Center spread / down spread (± or –)

Figure 15. Modulation Frequency (fm) and Modulation Amount

Figure 15. Modulation Frequency (fm) and Modulation Amount

9.2.2 Detailed Design Procedure

9.2.2.1 Spread Spectrum Clock (SSC)

Spread-spectrum modulation is a method to spread emitted energy over a larger bandwidth. In clocking, spread spectrum can reduce Electromagnetic Interference (EMI) by reducing the level of emission from clock distribution network.

9.2.2.2 PLL Frequency Planning

At a given input frequency (ƒIN), the output frequency (ƒOUT) of the CDCEx913 are calculated with Equation 1.

where

- M (1 to 511) and N (1 to 4095) are the multiplier/divide values of the PLL

- Pdiv (1 to 127) is the output divider

The target VCO frequency (ƒVCO) of each PLL is calculated with Equation 2.

The PLL internally operates as fractional divider and needs the following multiplier/divider settings:

- N

- P = 4 – int(log2N/M; if P < 0 then P = 0

- Q = int(N'/M)

- R = N′ – M × Q

where

N′ = N × 2P

N ≥ M;

16 ≤ Q ≤ 63

0 ≤ P ≤ 4

0 ≤ R ≤ 51

The values for P, Q, R, and N’ are automatically calculated when using TI Pro-Clock™ software.

9.2.2.3 Crystal Oscillator Start-Up

When the CDCEx937 is used as a crystal buffer, crystal oscillator start-up dominates the start-up time compared to the internal PLL lock time. Figure 17 shows the oscillator start-up sequence for a 27-MHz crystal input with an 8-pF load. The start-up time for the crystal is in the order of approximately 250 µs compared to approximately 10 µs of lock time. In general, lock time will be an order of magnitude less compared to the crystal start-up time.

Figure 17. Crystal Oscillator Start-Up vs PLL Lock Time

Figure 17. Crystal Oscillator Start-Up vs PLL Lock Time

9.2.2.4 Frequency Adjustment With Crystal Oscillator Pulling

The frequency for the CDCEx937 is adjusted for media and other applications with the VCXO control input Vctrl. If a PWM modulated signal is used as a control signal for the VCXO, an external filter is needed.

Figure 18. Frequency Adjustment Using PWM Input to the VCXO Control

Figure 18. Frequency Adjustment Using PWM Input to the VCXO Control

9.2.2.5 Unused Inputs and Outputs

If VCXO pulling functionality is not required, Vctrl should be left floating. All other unused inputs should be set to GND. Unused outputs should be left floating.

If one output block is not used, TI recommends disabling it. However, TI always recommends providing the supply for the second output block even if it is disabled.

9.2.2.6 Switching Between XO and VCXO Mode

When the CDCEx937 is in crystal oscillator or in VCXO configuration, the internal capacitors require different internal capacitance. The following steps are recommended to switch to VCXO mode when the configuration for the on-chip capacitor is still set for XO mode. To center the output frequency to 0 ppm:

- While in XO mode, put Vctrl = Vdd / 2

- Switch from XO mode to VCXO mode

- Program the internal capacitors in order to obtain 0 ppm at the output

9.2.3 Application Curves

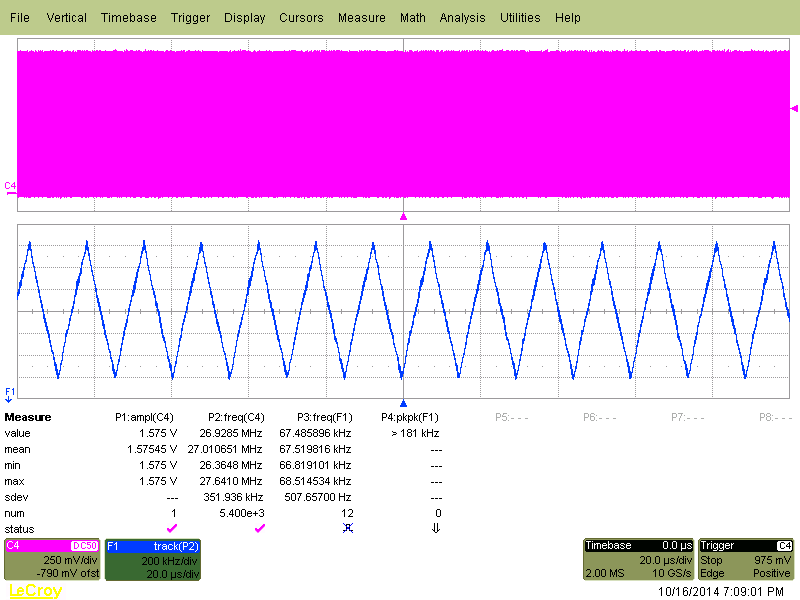

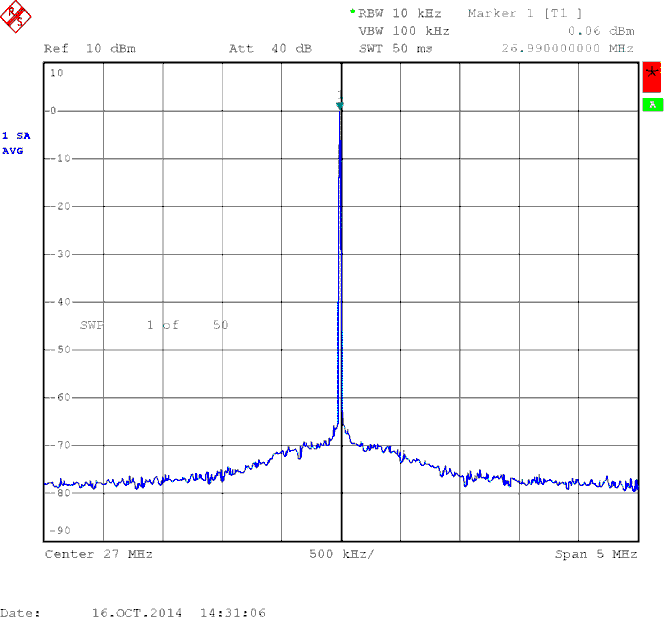

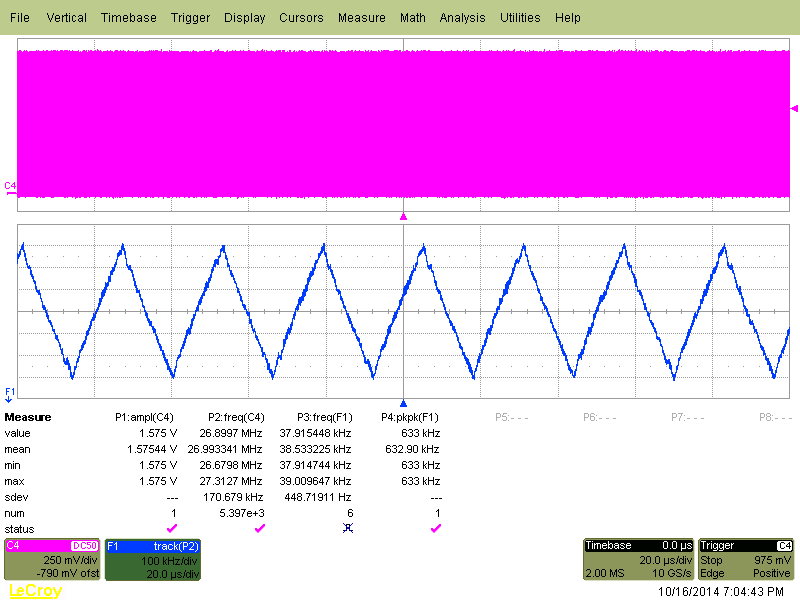

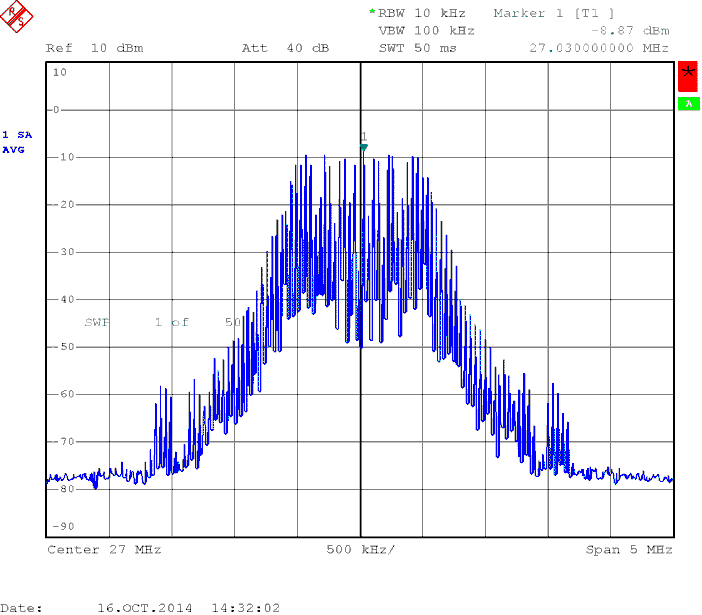

Figure 19, Figure 20, Figure 21, and Figure 22 show CDCEx937 measurements with the SSC feature enabled. Device configuration: 27-MHz input, 27-MHz output.

Figure 19. fout = 27 MHz, VCO frequency < 125 MHz, SSC (2% center)

Figure 19. fout = 27 MHz, VCO frequency < 125 MHz, SSC (2% center)

Figure 21. Output Spectrum With SSC Off

Figure 21. Output Spectrum With SSC Off

Figure 20. fout = 27 MHz, VCO frequency > 175 MHz, SSC (1%, center)

Figure 20. fout = 27 MHz, VCO frequency > 175 MHz, SSC (1%, center)

Figure 22. Output Spectrum With SSC On, 2% Center

Figure 22. Output Spectrum With SSC On, 2% Center