# MSPM33C32xx Microcontrollers

#### **ABSTRACT**

This document describes the known exceptions to the functional specifications (advisories).

## **Table of Contents**

| 1 Functional Advisories                              | 1 |

|------------------------------------------------------|---|

| 2 Preprogrammed Software Advisories                  | 1 |

| 3 Debug Only Advisories                              |   |

| 4 Fixed by Compiler Advisories                       | 1 |

| 5 Device Nomenclature                                |   |

| 5.1 Device Symbolization and Revision Identification | 2 |

| 6 Advisory Descriptions                              | 3 |

| 7 Trademarks                                         |   |

| 8 Revision History                                   |   |

### 1 Functional Advisories

Advisories that affect the device operation, function, or parametrics.

✓ The check mark indicates that the issue is present in the specified revision.

| Errata Number   | Rev A    |

|-----------------|----------|

| AES_ERR_01      | ✓        |

| GPIO_ERR_05     | ✓        |

| GPIO_ERR_06     | ✓        |

| KEYSTORE_ERR_01 | ✓        |

| SYSCTL_ERR_01   | <b>✓</b> |

| SYSPLL_ERR_01   | ✓        |

| TIMER_ERR_04    | ✓        |

| TIMER_ERR_06    | ✓        |

| TIMER_ERR_07    | ✓        |

## 2 Preprogrammed Software Advisories

Advisories that affect factory-programmed software.

✓ The check mark indicates that the issue is present in the specified revision.

## 3 Debug Only Advisories

Advisories that affect only debug operation.

✓ The check mark indicates that the issue is present in the specified revision.

## 4 Fixed by Compiler Advisories

Advisories that are resolved by compiler workaround. Refer to each advisory for the IDE and compiler versions with a workaround.

✓ The check mark indicates that the issue is present in the specified revision.

## **5 Device Nomenclature**

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all MSP MCU devices. Each MSP MCU commercial family member has one of two prefixes: MSP or XMS. These prefixes represent evolutionary stages of product development from engineering prototypes (XMS) through fully qualified production devices (MSP).

XMS – Experimental device that is not necessarily representative of the final device's electrical specifications

MSP - Fully qualified production device

Support tool naming prefixes:

**X**: Development-support product that has not yet completed Texas Instruments internal qualification testing. **null**: Fully-qualified development-support product.

XMS devices and X development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

MSP devices have been characterized fully, and the quality and reliability of the device have been demonstrated fully. Tl's standard warranty applies.

Predictions show that prototype devices (XMS) have a greater failure rate than the standard production devices. TI recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

TI device nomenclature also includes a suffix with the device family name. This suffix indicates the temperature range, package type, and distribution format.

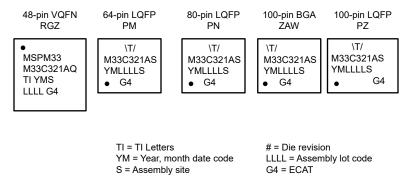

## 5.1 Device Symbolization and Revision Identification

The package diagrams below indicate the package symbolization scheme, and Table 5-1 defines the device revision to version ID mapping.

Figure 5-1. Package Symbolization

Table 5-1. Die Revisions

| Revision Letter | Version (in the device factory constants memory) |

|-----------------|--------------------------------------------------|

| A               | 1                                                |

The revision letter indicates the product hardware revision. Advisories in this document are marked as applicable or not applicable for a given device based on the revision letter. This letter maps to an integer stored in the memory of the device, which can be used to look up the revision using application software or a connected debug probe.

## **6 Advisory Descriptions**

AES\_ERR\_01 AES Module

Category Functional

Function

AES Saved Context Ready interrupt is not generating as expected

**Description**Saved Context Ready interrupt is not getting generated. The interrupt is generated if an

access (read or write) is made to any AES register.

Workaround

Use polling based mechanism to check the status bit for Saved Context Ready in CTRL

register instead of interrupt.

GPIO\_ERR\_05 GPIO Module

**Category** Functional

Function

Writing to GPIO DOUTTGL registers might get missed when a DMA transfer is ongoing

**Description**The GPIO DMAMASK register information is mistakenly applied to a CPU write to the

DOUTTGL register when a concurrent DMA transfer is in progress.

Workaround

In the application code, ensure that the GPIO DMAMASK bit is set to 1 for the

corresponding bit in the DOUTTGL register, before a CPU write access to the DOUTTGL register is issued. If no DMA transfer to any of the GPIO registers is required, the GPIO DMAMASK can be configured as 0xFFFFFFFF during the IO initialization step. This will solve the conflict of this errata. If the application also requires DMA write transfers to the GPIO registers, it is recommended that the application not use both DMA and CPU to write to the DOUTTGL register of the same GPIO module in the device. If the device has multiple GPIO modules, the DMA and the CPU can simultaneously write to the DOUTTGL register of different GPIO modules (while still requiring that the GPIO DMAMASK be

configured for the GPIO module the CPU is writing to).

GPIO ERR 06 GPIO Module

Category Functional

Function

Writing to GPIO DOUT, DOUTSET and DOUTCLR registers might get missed when a

DMA transfer is ongoing

Description

The GPIO DOUT, DOUTSET and DOUTCLR registers cannot be accessed by the DMA.

Due to mistake in the implementation, the CPU access to the GPIO DOUT, DOUTSET and DOUTCLR will be also be blocked when a concurrent DMA transfer is in progress.

## **GPIO ERR 06**

(continued)

#### **GPIO Module**

#### Workaround

In the application code, instead of writing to the DOUT, DOUTSET, and DOUTCLR registers, software should perform equivalent writes to the DOUTTGL register (see workaround GPIO\_ERR\_05 for restrictions on CPU writes to the DOUTTGL register).

In the pseudo code below, "pins" denotes the bit vector of pins in the GPIO module to be configured.

```

DL_GPIO_setPins(GPIO_Regs* gpio, uint32_t pins) {

gpio->DOUTTGL31_0 = ~(gpio->DOUT31_0) & pins;

}

DL_GPIO_clearPins(GPIO_Regs* gpio, uint32_t pins) {

gpio->DOUTTGL31_0 = gpio->DOUT31_0 & pins;

}

DL_GPIO_writePins(GPIO_Regs* gpio, uint32_t pins) {

gpio->DOUTTGL31_0 = ~(gpio->DOUT31_0) & pins;

gpio->DOUTTGL31_0 = gpio->DOUT31_0 & (~pins);

}

DL_GPIO_writePinsVal(GPIO_Regs* gpio, uint32_t pinsMask, uint32_t pinsVal) {

uint32_t doutVal = gpio->DOUT31_0;

doutVal &= ~pinsMask;

doutVal |= (pinsVal & pinsMask);

gpio->DOUTTGL31_0 = ~(gpio->DOUT31_0) & doutVal;

gpio->DOUTTGL31_0 = gpio->DOUT31_0 & (~doutVal);

}

```

## KEYSTORE\_ERR\_

01

#### KEYSTORE Module

Category

**Functional**

**Function**

STATUS.STAT value can be 0 or 1 without key access

Description

STATUS.STAT has a reset value of 1 and turns to 0 under these conditions: 1. After reset, debugger access via the register window returns 0x00. 2. After reset, the first CPU read returns 0x01, while subsequent CPU reads return 0x00. 3) After reset, first reading any other KEYSTORE register and then reading STATUS.STAT return 0x00.

Workaround

STATUS.STAT=0x0 means "No Error" . For checking if a slot is valid or not (Whether key is present), check STATUS.VALID.

## SYSCTL\_ERR\_01 SYSCTL Module

Category

**Functional**

**Function**

SW-POR functionality is combined with HW-POR

Description

When a user writes to the LFSSRST register with the correct key to generate a software-triggered POR, the RSTCAUSE register will display 0x2 (indicating an NRST-triggered POR) instead of the expected 0x3 (Software-Triggered POR). This occurs because the SW-POR functionality is combined with the HW-POR path.

Workaround

No

## SYSPLL ERR 01 SYSPLL Module

Category

**Functional**

**Function**

SYSPLL Frequency may not lock to correct frequency when enabled.

Description

When setting the SYSPLLEN bit to 1 in SYSCTL HSCLKEN register, the SYSPLL will run the phase locked loop search. The search can potentially fail where the frequency will not be set to the correct value, instead the resultant frequency will be drastically different than the configured frequency.

### Workaround

Check the frequency output of the SYSPLL using the Frequency Clock Counter (FCC) anytime the SYSPLLEN bit is set to 1. Once the frequency is correct it will maintain the correct value until disabled and reenabled (SYSPLLEN set to 0 then 1), once reenabled the PLL will re-run the search and the SYSPLL output will need to be rechecked.

Workaround 1: Set FCC with SYSPLLCLK0 as the CLK input and LFCLK as the Trigger source. Run the FCC and check the value for the configured SYSPLL frequency with reference to the LFCLK; for example, with SYSPLL = 80MHz and LFCLK = 32kHz, the resultant FCC count should be 80,000,000/32,768= ~2441. The count will vary depending on the combined clock accuracies, so it is recommended to add a +-5% to allowed range. Estimated time for FCC is 30us.

FCC Settings: SYSCTL.GENCLKCFG.FCCTRIGCNT = 0, SYSCTL.GENCLKCFG.FCCTRIGSRC = 1, SYSCTL.GENCLKCFG.FCCSELCLK = 4;

If the FCC value is incorrect, disable and reenable the SYSPLL by setting SYSPLLEN to 0 then 1. Rerun the FCC check.

Workaround 2: Output SYSOSC/2 from the CLK\_OUT pin and route the signal into FCC\_IN. Use the SYSPLLCLK0 as the FCC CLK and the FCC\_IN for the trigger source. Run the FCC for 16 Clock cycles, and check the value for the configured SYSPLL frequency with reference to the SYSOSC; for example, with SYSPLL = 80MHz and SYSOSC/2 = 16MHz, the resultant FCC count should be 80,000,000/16,000,000 \* 16 = ~80. The count will vary depending on the combined clock accuracies, so it is recommended to add a +-5% to allowed range. Estimated time for FCC is 1us.

## SYSPLL\_ERR\_01

(continued)

#### SYSPLL Module

FCC Settings: SYSCTL.GENCLKCFG.FCCTRIGCNT = 0x0F,

SYSCTL.GENCLKCFG.FCCTRIGSRC = 0, SYSCTL.GENCLKCFG.FCCSELCLK = 4;

If the FCC value is incorrect, disable and reenable the SYSPLL by setting SYSPLLEN to  $\boldsymbol{0}$

then 1. Rerun the FCC check.

TIMER ERR 04

TIMER Module

Category

**Functional**

**Function**

TIMER re-enable may be missed if done close to zero event

**Description**

When using a TIMER in one shot mode, TIMER re-enable may be missed if done close to zero event. The HW update to the timer enable bit will take a single functional clock cycle. For example, if the timer's clock source is 32.768kHz and clock divider of 3, then it will take ~100us to have the enable bit set to 0 properly.

Workaround

Wait 1 functional clock cycle before re-enabling the timer OR the timer can be disabled

first before re-enabling.

Disable the counter with CTRCTL.EN = 0, then re-enable with CTRCTL.EN = 1

TIMER\_ERR\_06

TIMG Module

Category

**Functional**

**Function**

Writing 0 to CLKEN bit does not disable counter

Description

Writing 0 to the Counter Clock Control Register(CCLKCTL) Clock Enable bit(CLKEN)

does not stop the timer.

Workaround

Stop the timer by writing 0 to the Counter Control(CTRCTL) Enable(EN) bit.

TIMER\_ERR\_07

Initial repeat counter has 1 less period than next repeats Module

Category

**Functional**

**Function**

**TIMER**

Description

When using the timer repeat counter mode, the first repeat will have 1 less count than the subsequent repeats because the following repeat counters will include the transition www.ti.com Trademarks

## TIMER\_ERR\_07

(continued)

### Initial repeat counter has 1 less period than next repeats Module

between 0 and the load value. For example if the TIMx.RCLD = 0x3 then 3 observable zero events would appear on the first repeat counter and 4 observable zero events would appear on the following repeat counter sequences.

#### Workaround

Set the initial RCLD value to 1 more than the expected RCLD, then in the ISR for the Repeat Counter Zero Event (REPC), set the RCLD to the intended RCLD value. For example, if intending to have 4 repeats, set the initial RCLD value to RCLD = 0x5, then in the timer ISR for the REPC interrupt, set RCLD = 0x4. Now all timer repeats will have the same number of zero/load events.

### 7 Trademarks

All trademarks are the property of their respective owners.

## **8 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2025 | *        | Initial Release |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025