**OPA2277-EP**

SBOS700 - DECEMBER 2014

# **OPA2277-EP High-Precision, Low-Noise Operational Amplifier**

#### **Features**

Ultra-Low Offset Voltage: 10 µV High Open-Loop Gain: 134 dB

High Common-Mode Rejection: 140 dB High Power Supply Rejection: 130 dB

Low Bias Current: 1-nA Maximum Wide Supply Range: ±2 to ±18 V

Low Quiescent Current: 800 µA/Amplifier

Supports Defense, Aerospace, and Medical Applications

Controlled Baseline

One Assembly and Test Site

One Fabrication Site

Available in Military (-55°C to 125°C) Temperature Range (1)

Extended Product Life Cycle

**Extended Product-Change Notification**

Product Traceability

## **Applications**

Transducer Amplifier

**Bridge Amplifier**

Temperature Measurements

Strain Gage Amplifier

Precision Integrator

**Battery-Powered Instruments**

Test Equipment

Additional temperature ranges available - contact factory

## 3 Description

OPA2277 precision operational replaces the industry standard OP-177. It offers improved noise, wider output voltage swing, and is twice as fast with half the quiescent current. Features include ultra-low offset voltage and drift, low bias current, high common-mode rejection, and high power supply rejection.

OPA2277 operates from ±2-V to ±18-V supplies with excellent performance. Unlike most operational amplifiers, which are specified at only one supply voltage, the OPA2277 is specified for real-world applications; a single limit applies over the ±5-V to ±15-V supply range. High performance is maintained as the amplifiers swing to their specified limit. Because the initial offset voltage (±20 µV max) is so low, user adjustment is usually not required.

OPA2277 is easy to use and free from phase inversion and overload problems found in some operational amplifiers. It is stable in unity gain and provides excellent dynamic behavior over a wide of load conditions. OPA2277 features completely independent circuitry for lowest crosstalk and freedom from interaction, even when overdriven or overloaded. Dual versions are available in DIP-8, SO-8. OPA2277 is fully specified and operates from -55°C to 125°C.

#### Device Information<sup>(1)</sup>

| ORDER NUMBER | PACKAGE  | BODY SIZE (NOM)   |  |  |

|--------------|----------|-------------------|--|--|

| OPA2277MDTEP | SOIC (8) | 3.91 mm × 4.90 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

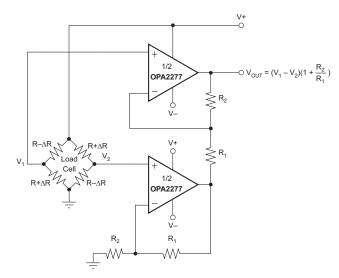

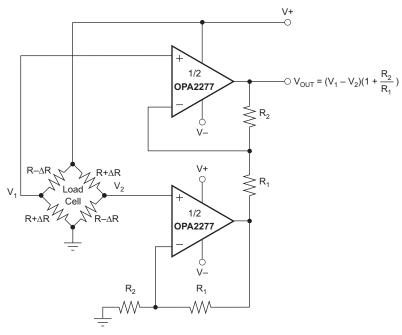

# **Load Cell Amplifier Schematic**

# **Table of Contents**

| 1 | Features 1                           |    | 8.2 Functional Block Diagram                     |    |

|---|--------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                       |    | 8.3 Feature Description                          | 1° |

| 3 | Description 1                        | 9  | Application and Implementation                   | 12 |

| 4 | Load Cell Amplifier Schematic 1      |    | 9.1 Application Information                      | 12 |

| 5 | Revision History2                    |    | 9.2 Typical Application                          | 12 |

| 6 | Pin Configuration and Functions      | 10 | Power Supply Recommendations                     | 1  |

| 7 | Specifications4                      | 11 | Layout                                           | 18 |

| • | 7.1 Absolute Maximum Ratings         |    | 11.1 Layout Guidelines                           | 1  |

|   | 7.2 ESD Ratings                      |    | 11.2 Layout Example                              | 19 |

|   | 7.3 Recommended Operating Conditions | 12 | Device and Documentation Support                 | 17 |

|   | 7.4 Thermal Information              |    | 12.1 Trademarks                                  | 1  |

|   | 7.5 Electrical Characteristics       |    | 12.2 Electrostatic Discharge Caution             | 1  |

|   | 7.6 Typical Characteristics 7        |    | 12.3 Glossary                                    | 1  |

| 8 | Detailed Description                 | 13 | Mechanical, Packaging, and Orderable Information | 1  |

|   |                                      |    |                                                  |    |

# **5** Revision History

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| December 2014 | *        | Initial release. |

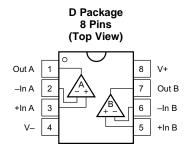

# 6 Pin Configuration and Functions

### **Pin Functions**

| PIN   |     | 1/0 | DESCRIPTION                           |

|-------|-----|-----|---------------------------------------|

| NAME  | NO. | 1/0 | DESCRIFTION                           |

| OUT A | 1   | 0   | Amplifier output A                    |

| −IN A | 2   | - 1 | Inverting amplifier input A           |

| +IN A | 3   | - 1 | Non-inverting amplifier input A       |

| V-    | 4   | - 1 | Negative amplifier power supply input |

| +IN B | 5   | - 1 | Non-inverting amplifier input B       |

| –IN B | 6   | - 1 | Inverting amplifier input B           |

| OUT B | 7   | 0   | Amplifier output B                    |

| V+    | 8   | - 1 | Positive amplifier power supply input |

## 7 Specifications

## 7.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature (unless otherwise noted)

|                              |                                      | MIN        | MAX        | UNIT |

|------------------------------|--------------------------------------|------------|------------|------|

| Supply volta                 | nge .                                |            | 36         | V    |

| Input voltag                 | е                                    | (V-) - 0.7 | (V+) + 0.7 | V    |

| Output shor                  | t-circuit (to ground) <sup>(2)</sup> | Contir     | Continuous |      |

| Operating to                 | emperature                           | -55        | 125        | °C   |

| Junction ten                 | nperature                            |            | 150        | °C   |

| Lead tempe                   | rature (soldering, 10 s)             |            | 300        | °C   |

| T <sub>stg</sub> Storage tem | perature range                       | -55        | 125        | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                              |                 |                                                                             | VALUE | UNIT |

|------------------------------|-----------------|-----------------------------------------------------------------------------|-------|------|

| \/                           | , Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±2000 | \/   |

| V <sub>(ESD)</sub> discharge | discharge       | Machine model (MM)                                                          | ±100  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|       |                                | MIN | NOM I | MAX | UNIT |

|-------|--------------------------------|-----|-------|-----|------|

| Vs    | Specified voltage range        | ±5  |       | ±15 | V    |

|       | Operating voltage range        | ±2  |       | ±18 | V    |

| $T_J$ | Operating junction temperature | -55 |       | 125 | °C   |

#### 7.4 Thermal Information

|                       |                                              | OPA2277 |       |

|-----------------------|----------------------------------------------|---------|-------|

|                       | THERMAL METRIC <sup>(1)</sup>                | D       | UNIT  |

|                       |                                              | 8 PINS  |       |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 91.9    |       |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 39.9    |       |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 40.6    | 9C/M/ |

| ΨЈТ                   | Junction-to-top characterization parameter   | 3.9     | °C/W  |

| ΨЈВ                   | Junction-to-board characterization parameter | 39.6    |       |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A     |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> One channel per package.

# 7.5 Electrical Characteristics

At  $T_A$  = 25°C,  $V_S$  = ±5 V to ±15 V,  $R_L$  = 2 k $\Omega$  (unless otherwise noted).

|                 | PARAMETER                                            |                       | TEST CONDITIONS                                                                      | MIN      | TYP N  | IAX | UNIT       |  |

|-----------------|------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------|----------|--------|-----|------------|--|

| OFFSE           | T VOLTAGE                                            |                       |                                                                                      |          |        | _   |            |  |

| Vos             | Input offset voltage                                 |                       |                                                                                      |          | ±20    | ±65 | μV         |  |

|                 | vs temperature, $T_J = -55$ °C                       | to 125°C              |                                                                                      |          | ±      | 150 | μV         |  |

|                 | vs temperature (dV <sub>OS</sub> /dT), T<br>125°C    | J = -55°C to          |                                                                                      | ±        | 0.15   |     | μV/°C      |  |

|                 | vs power supply (PSRR)                               |                       | $V_S = \pm 2 \text{ V to } \pm 18 \text{ V}$                                         |          | ±0.3   | ±1  | μV/V       |  |

|                 | $T_J = -55$ °C to 125°C                              |                       | $V_S = \pm 2 \text{ V to } \pm 18 \text{ V}$                                         |          |        | ±1  | μν/ν       |  |

|                 | vs time                                              |                       |                                                                                      |          | 0.2    |     | μV/mo      |  |

|                 | Channel separation (dual)                            |                       | dc                                                                                   |          | 0.1    |     | μV/V       |  |

| INPUT           | BIAS CURRENT                                         |                       |                                                                                      |          |        |     |            |  |

|                 | Input bias current                                   |                       |                                                                                      |          | ±0.5   | 2.8 | <b>~</b> ^ |  |

| I <sub>B</sub>  | $T_J = -55$ °C to 125°C                              |                       |                                                                                      |          |        | ±7  | nA         |  |

|                 | Input offset current                                 | ·                     |                                                                                      |          | ±0.5 : | 2.8 | r.Λ        |  |

| los             | $T_J = -55$ °C to 125°C                              |                       |                                                                                      |          |        | ±7  | nA         |  |

| NOISE           |                                                      |                       |                                                                                      |          |        |     |            |  |

|                 | Innut voltage noise f 0.1 to                         | 1011-                 |                                                                                      |          | 0.22   |     | μVpp       |  |

|                 | Input voltage noise, $f = 0.1$ to                    | ) 10 112              |                                                                                      | 0        | .035   |     | μVrms      |  |

|                 | Input voltage noise density                          | f = 10  Hz<br>f = 100 |                                                                                      |          | 12     |     |            |  |

| e <sub>n</sub>  |                                                      | ) = 100<br>Hz         |                                                                                      |          | 8      |     | nV/√Hz     |  |

|                 |                                                      | f = 1 Hz              |                                                                                      |          | 8      |     | ,          |  |

|                 |                                                      | f = 10 Hz             |                                                                                      |          | 8      |     |            |  |

| in              | Current noise density                                | f = 1  kHz            |                                                                                      |          | 0.2    |     | pA/√Hz     |  |

| INPUT           | VOLTAGE RANGE                                        | •                     |                                                                                      |          |        | i i |            |  |

| $V_{CM}$        | Common-mode voltage range                            | )                     |                                                                                      | (V-) + 2 | (V+)   | -2  | V          |  |

|                 | Common-mode rejection                                |                       | $V_{CM} = (V-) + 2 V \text{ to } (V+) - 2 V$                                         | 115      | 140    |     | dB         |  |

| CMRR            | $T_J = -55$ °C to 125°C                              |                       | V <sub>CM</sub> = (V-) + 2 V to (V+) - 2 V                                           | 115      |        |     | dB         |  |

| INPUT           | IMPEDANCE                                            |                       |                                                                                      |          |        |     |            |  |

|                 | Differential                                         |                       |                                                                                      | 100      | 0    3 |     | MΩ    pF   |  |

|                 | Common-mode                                          |                       | $V_{CM} = (V-) + 2 V \text{ to } (V+) - 2 V$                                         | 250      | 0    3 |     | GΩ    pF   |  |

| OPEN-           | LOOP GAIN                                            |                       |                                                                                      |          |        |     |            |  |

|                 |                                                      |                       | $V_O = (V-) + 0.5 \text{ V to } (V+) - 1.2 \text{ V},$<br>$R_L = 10 \text{ k}\Omega$ |          | 140    |     |            |  |

| A <sub>OL</sub> | Open-loop voltage gain $T_J = -55^{\circ}C$ to 125°C |                       | $V_O = (V-) + 1.5 \text{ V to } (V+) - 1.5 \text{ V},$<br>$R_L = 2 \text{ k}\Omega$  | 126      | 134    |     | dB         |  |

|                 | •                                                    |                       | $V_{O} = (V-) + 1.5 \text{ V to } (V+) - 1.5 \text{ V},$<br>$R_{L} = 2 \Omega$       | 126      |        |     |            |  |

| FREQU           | JENCY RESPONSE                                       |                       |                                                                                      |          |        |     |            |  |

| GBW             | Gain bandwidth product                               |                       |                                                                                      |          | 1      |     | MHz        |  |

| SR              | Slew rate                                            |                       |                                                                                      |          | 0.8    |     | V/µs       |  |

|                 | Cattling time                                        | 0.1%                  | V <sub>S</sub> = ±15 V, G = 1, 10-V step                                             |          | 14     |     | μs         |  |

|                 | Settling time                                        | 0.01%                 | V <sub>S</sub> = ±15 V, G = 1, 10-V step                                             |          | 16     |     | μs         |  |

|                 | Overload recovery time                               |                       | V <sub>IN</sub> x G = V <sub>S</sub>                                                 |          | 3      |     | μs         |  |

|                 | Total harmonic distortion + no (THD + N)             | oise                  | f = 1 kHz, G = 1, V <sub>O</sub> = 3.5 Vrms                                          | 0.0      | 02%    |     |            |  |

## **Electrical Characteristics (continued)**

At T<sub>A</sub> = 25°C, V<sub>S</sub> =  $\pm 5$  V to  $\pm 15$  V, R<sub>L</sub> = 2 k $\Omega$  (unless otherwise noted).

|                                       | PARAMETER                         | TEST CONDITIONS                                                                       | MIN        | TYP MAX    | UNIT |

|---------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------|------------|------------|------|

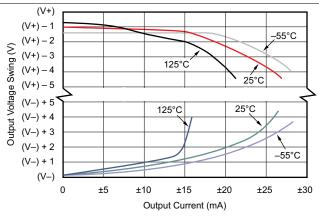

| OUTPU                                 | JT                                |                                                                                       |            |            |      |

|                                       | Valtage autout                    | $R_L = 10 \text{ k}\Omega$                                                            | (V-) + 0.5 | (V+) - 1.2 |      |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |                                   | $R_L = 10 \text{ k}\Omega, T_J = -55^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ | (V-) + 0.5 | (V+) - 1.2 | V    |

| Vo                                    | Voltage output                    | $R_L = 2 k\Omega$                                                                     | (V-) + 1.5 | (V+) - 1.5 | V    |

|                                       |                                   | $R_L = 2 k\Omega$ , $T_J = -55$ °C to 125°C                                           | (V-) + 1.5 | (V+) - 1.5 |      |

| I <sub>SC</sub>                       | Short-circuit current             |                                                                                       |            | ±35        | mA   |

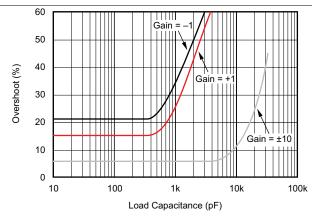

| $C_{LOAD}$                            | Capacitive load drive             |                                                                                       | See Typica |            |      |

|                                       | R SUPPLY                          |                                                                                       | •          |            |      |

| Vs                                    | Specified voltage range           |                                                                                       | ±5         | ±15        | V    |

|                                       | Operating voltage range           |                                                                                       | ±2         | ±18        | V    |

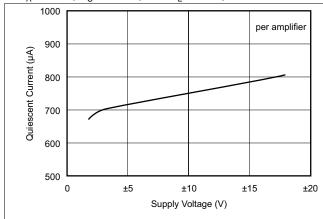

|                                       | Quiescent current (per amplifier) | I <sub>O</sub> = 0 A                                                                  |            | ±790 ±825  | μΑ   |

| IQ                                    | $T_J = -55$ °C to 125°C           | I <sub>O</sub> = 0 A                                                                  |            | ±900       | μΑ   |

| TEMPE                                 | RATURE RANGE                      |                                                                                       | •          |            |      |

|                                       | Specified temperature range       |                                                                                       | -55        | 125        | °C   |

|                                       | Operating temperature range       |                                                                                       | -55        | 125        | °C   |

| T <sub>stg</sub>                      | Storage temperature range         |                                                                                       | -55        | 125        | °C   |

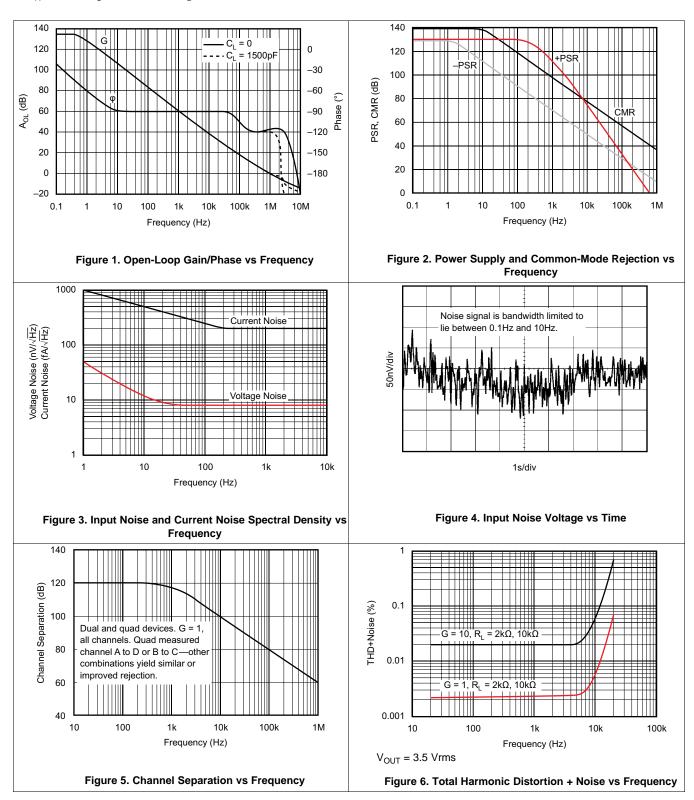

## 7.6 Typical Characteristics

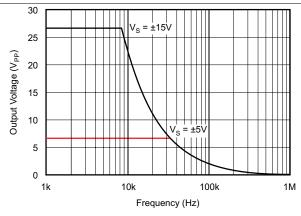

At  $T_A$  = 25°C,  $V_S$  = ±15 V, and  $R_L$  = 2 k $\Omega$ , unless otherwise noted.

## TEXAS INSTRUMENTS

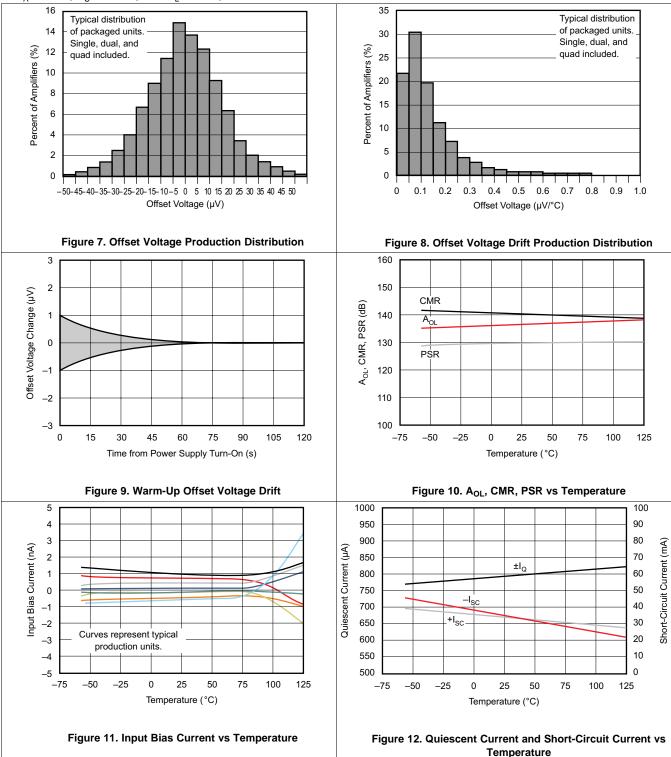

## **Typical Characteristics (continued)**

At  $T_A = 25$ °C,  $V_S = \pm 15$  V, and  $R_L = 2$  k $\Omega$ , unless otherwise noted.

## **Typical Characteristics (continued)**

At  $T_A = 25$ °C,  $V_S = \pm 15$  V, and  $R_L = 2$  k $\Omega$ , unless otherwise noted.

Figure 13. Quiescent Current vs Supply Voltage

Figure 14. Settling Time vs Closed-Loop Gain

Figure 15. Maximum Output Voltage vs Frequency

Figure 16. Output Voltage Swing vs Output Current

Figure 17. Small-Signal Overshoot vs Load Capacitance

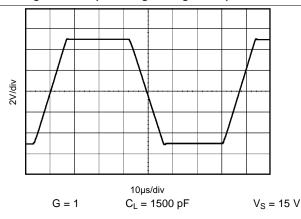

Figure 18. Large-Signal Step Response

## **Typical Characteristics (continued)**

At  $T_A$  = 25°C,  $V_S$  = ±15 V, and  $R_L$  = 2 k $\Omega$ , unless otherwise noted.

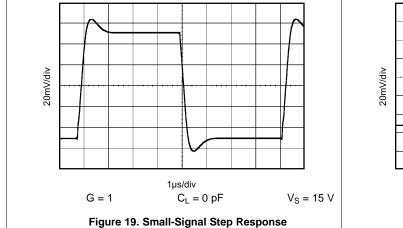

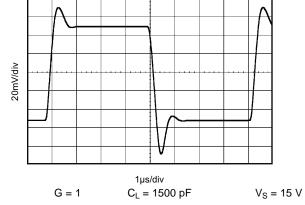

Figure 20. Small-Signal Step Response

www.ti.com SBOS700 – DEC

## 8 Detailed Description

#### 8.1 Overview

The OPA2277 is a unity-gain stable, high-precision, and low-noise operational amplifier. OPA2277 operates from ±2- to ±18-V supplies with excellent performance. Unlike most operational amplifiers which are specified at only one supply voltage, the OPA2277 is specified for real-world applications; a single limit applies over the ±5- to ±15-V supply range. High performance is maintained as the amplifiers swing to their specified limit. Because the initial offset voltage (±50-µV max) is so low, user adjustment is usually not required.

#### 8.2 Functional Block Diagram

$$V_{ln+} \circ V_{out}$$

### 8.3 Feature Description

The OPA2277 precision operational amplifier replaces the industry standard OP-177. It offers improved noise, wider output voltage swing, and is twice as fast with half the quiescent current. Features include ultra-low offset voltage and drift, low bias current, high common-mode rejection, and high power-supply rejection.

OPA2277 is easy to use and free from phase inversion and overload problems found in some operational amplifiers. It is stable in unity gain and provides excellent dynamic behavior over a wide range of load conditions. OPA2277 features completely independent circuitry for lowest crosstalk and freedom from interaction, even when overdriven or overloaded.

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

The OPA2277 is unity-gain stable and free from unexpected output phase reversal, making it easy to use in a wide range of applications. Applications with noisy or high-impedance power supplies may require decoupling capacitors close to the device pins. In most cases, 0.1-µF capacitors are adequate.

### 9.2 Typical Application

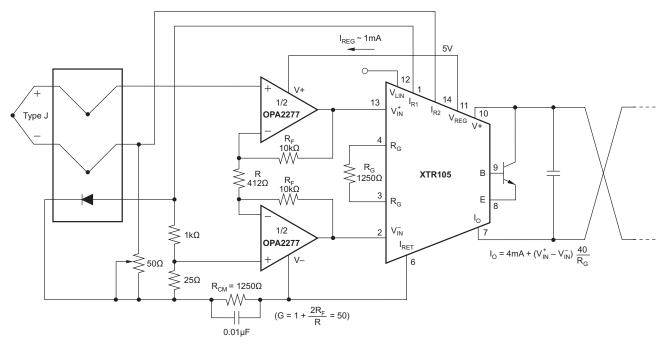

Figure 21. Thermocouple Low-Offset, Low-Drift Loop Measurement With Diode Cold Junction Compensation

### 9.2.1 Design Requirements

For the thermocouple low-offset, low-drift loop measurement with diode cold junction compensation (see Figure 21), Table 1 lists the design parameters needed with gain = 50.

$$G = 1 + \frac{2R_F}{R} = 50 \tag{1}$$

**Table 1. Design Parameters**

| DESIGN PARAMETER | EXAMPLE VALUE |

|------------------|---------------|

| R <sub>F</sub>   | 10 kΩ         |

| R                | 412 Ω         |

## 9.2.2 Detailed Design Procedure

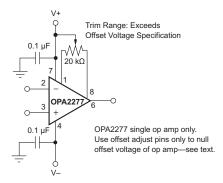

#### 9.2.2.1 Offset Voltage Adjustment

The OPA2277 is laser-trimmed for very-low offset voltage and drift so most circuits do not require external adjustment. However, offset voltage trim connections are provided on pins 1 and 8. Offset voltage can be adjusted by connecting a potentiometer as shown in Figure 22. Only use this adjustment to null the offset of the operational amplifier. Do not use this adjustment to compensate for offsets created elsewhere in a system because this can introduce additional temperature drift.

Figure 22. OPA2277 Offset Voltage Trim Circuit

#### 9.2.2.2 Input Protection

The inputs of the OPA2277 are protected with  $1-k\Omega$  series input resistors and diode clamps. The inputs can withstand  $\pm 30$ -V differential inputs without damage. The protection diodes conduct current when the inputs are overdriven. This may disturb the slewing behavior of unity-gain follower applications, but does not damage the operational amplifier.

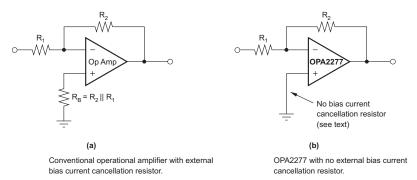

#### 9.2.2.3 Input Bias Current Cancellation

The input stage base current of the OPA2277 is internally compensated with an equal and opposite cancellation circuit. The resulting input bias current is the difference between the input stage base current and the cancellation current. This residual input bias current can be positive or negative.

When the bias current is canceled in this manner, the input bias current and input offset current are approximately the same magnitude. As a result, it is not necessary to use a bias current cancellation resistor as is often done with other operational amplifiers (see Figure 23). A resistor added to cancel input bias current errors may actually increase offset voltage and noise.

Figure 23. Input Bias Current Cancellation

For integrated solution see: INA126, INA2126 (dual), INA125 (on-board reference), or INA122 (single-supply).

Figure 24. Load Cell Amplifier

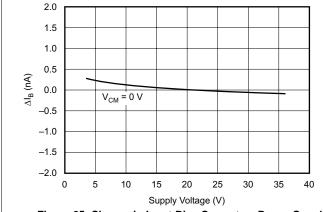

### 9.2.3 Application Curves

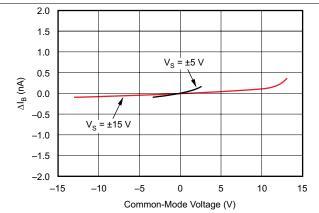

At  $T_J=25^{\circ}\text{C}$ ,  $V_S=\pm15$  V, and  $R_L=2$  k $\Omega$ . Figure 25 shows Change in input bias current versus power supply voltage. Curve shows normalized change in bias current with respect to  $V_S=\pm10$  V (+20 V). Typical IB may range from -0.5 to 0.5 nA at  $V_S=\pm10$  V. Figure 26 shows change in input bias current versus common-mode voltage. Curve shows normalized change in bias current with respect to  $V_{CM}=0$  V. Typical IB may range from -0.5 to 0.5 nA at  $V_{CM}=0$  V.

Figure 25. Change in Input Bias Current vs Power Supply Voltage

Figure 26. Change in Input Bias Current vs Common-Mode Voltage

# 10 Power Supply Recommendations

The OPA2277 operational amplifier operates from ±2.5- to ±18-V supplies with excellent performance. Unlike most operational amplifiers which are specified at only one supply voltage, the OPA2277 is specified for real-world applications. A single set of specifications applies over the ±5- to ±15-V supply range. Specifications are ensured for applications between ±5- and ±15-V power supplies. Some applications do not require equal positive and negative output voltage swing. Power supply voltages do not need to be equal. The OPA2277 can operate with as little as 5 V between the supplies and with up to 36 V between the supplies. For example, the positive supply could be set to 25 V with the negative supply at –5 V, or vice-versa. In addition, key parameters are ensured over the specified temperature range, –55°C to 125°C. The *Typical Characteristics* show parameters which vary significantly with operating voltage or temperature.

### 11 Layout

#### 11.1 Layout Guidelines

Solder the lead-frame die pad to a thermal pad on the PCB. Mechanical drawings in *Mechanical, Packaging, and Orderable Information* show the physical dimensions for the package and pad.

Soldering the exposed pad significantly improves board-level reliability during temperature cycling, key push, package shear, and similar board-level tests. Even with applications that have low-power dissipation, the exposed pad must be soldered to the PCB to provide structural integrity and long-term reliability.

The OPA2277 has very-low offset voltage and drift. To achieve highest performance, optimize circuit layout and mechanical conditions. Offset voltage and drift can be degraded by small thermoelectric potentials at the operational amplifier inputs. Connections of dissimilar metals generate thermal potential which can degrade the ultimate performance of the OPA2277. These thermal potentials can be made to cancel by assuring that they are equal in both input terminals.

- Keep thermal mass of the connections made to the two input terminals similar.

- Locate heat sources as far as possible from the critical input circuitry.

- Shield operational amplifier and input circuitry from air currents such as cooling fans.

#### 11.2 Layout Example

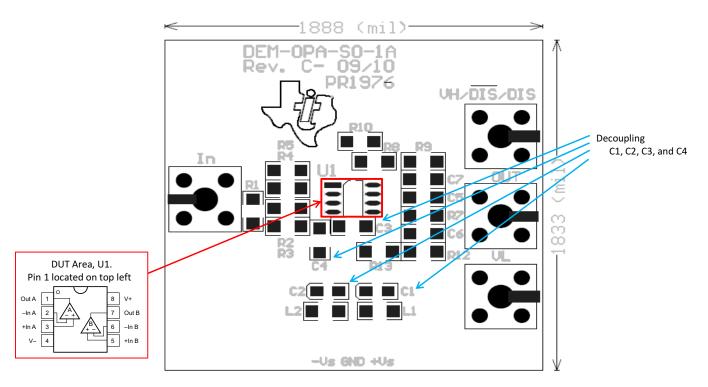

#### 11.2.1 Board Layout

This demonstration fixture is a two-layer PCB. It uses a ground plane on the bottom, and signal and power traces on the top. The ground plane has been opened up around Op Amp pins sensitive to capacitive loading. Power-supply traces are laid out to keep current loop areas to a minimum. The SMA (or SMB) connectors may be mounted either vertically or horizontally.

The location and type of capacitors used for power-supply bypassing are crucial to high-frequency amplifiers. The tantalum capacitors,  $C_1$  and  $C_2$ , do not need to be as close to pins 7 and 4 on your PCB, and may be shared with other amplifiers.

#### 11.2.2 Measurement Tips

This demonstration fixture and the component values shown are designed to operate in a  $50\Omega$  environment. Most data sheet plots are obtained in this manner. Change the component values for different input and output impedance levels.

Do not use high-impedance probes; they represent a heavy capacitive load to the Op Amps, and will alter the amplifier response. Instead, use low impedance ( $\leq 500\Omega$ ) probes with adequate bandwidth. The probe input capacitance and resistance set an upper limit on the measurement bandwidth. If a high-impedance probe must be used, place a  $100\Omega$  resistor on the probe tip to isolate its capacitance from the circuit.

## **Layout Example (continued)**

Figure 27. Decoupling Capacitors and DUT Area

## 12 Device and Documentation Support

#### 12.1 Trademarks

All trademarks are the property of their respective owners.

#### 12.2 Electrostatic Discharge Caution

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 12.3 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 10-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                |                       |      | (4)                           | (5)                        |              |                  |

| OPA2277MDTEP          | Active | Production    | SOIC (D)   8   | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -55 to 125   | OPA<br>2277E     |

| OPA2277MDTEP.A        | Active | Production    | SOIC (D)   8   | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -55 to 125   | OPA<br>2277E     |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF OPA2277-EP:

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 10-Nov-2025

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 30-Dec-2025

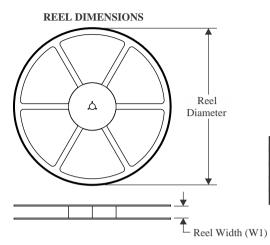

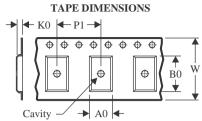

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

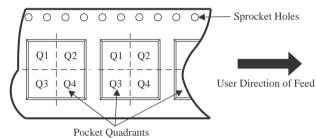

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | _    | Package<br>Drawing |   | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------|--------------------|---|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA2277MDTEP | SOIC | D                  | 8 | 250 | 180.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 30-Dec-2025

#### \*All dimensions are nominal

| Г | Device       | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |  |

|---|--------------|--------------|-----------------|------|-----|-------------|------------|-------------|--|

| Г | OPA2277MDTEP | SOIC         | D               | 8    | 250 | 213.0       | 191.0      | 35.0        |  |

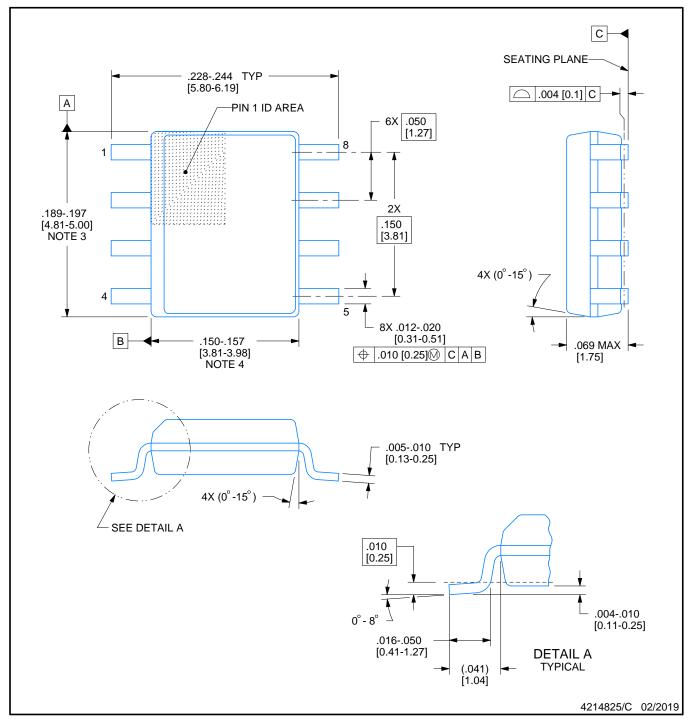

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

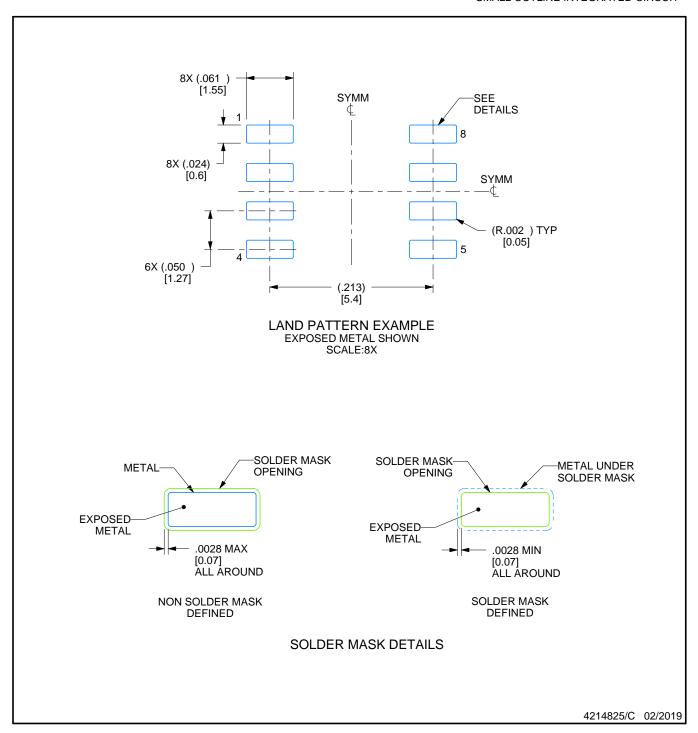

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

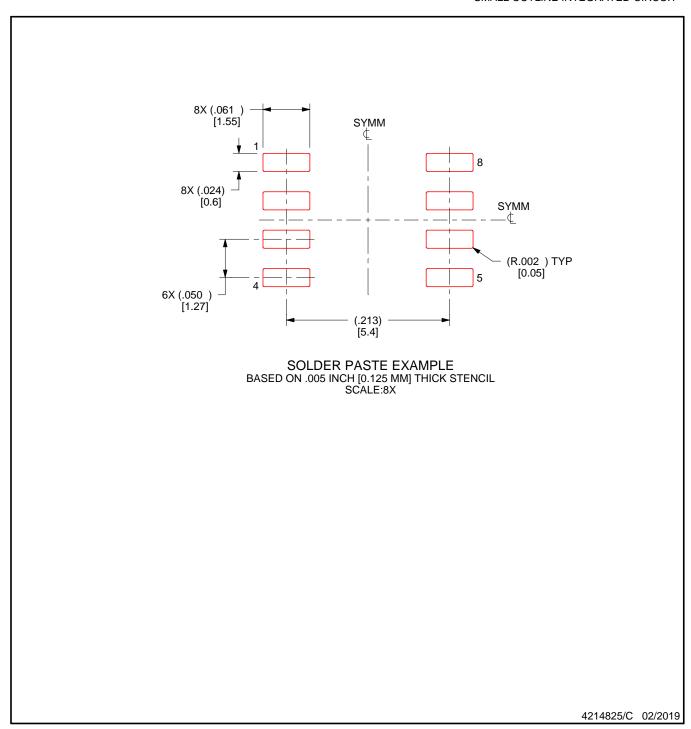

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025