TSW14J50EVM 的特性

- 使用 TI High Speed Data Converter Pro 软件快速评估 JESD204B DAC 和 ADC 性能

- 使用 FMC 标准连接器直接连接至所有 TI JESD204B 高速数据转换器 EVM

- 四分之一速率 DDR3 控制器 - 支持高达 667MHz 的 DDR3 操作

- JESD RX 和 TX IP 内核,带有 8 个既定收发器通道

- FPGA 和 FMC 连接器之间有许多可用的通用 IO(状态信号、SPI 接口等)

- 通过 SPI/JTAG 可重新配置的 JESD 核心参数:L、M、K、F、HD、S 等

- 支持子类 0 和 1 操作

- 可使用 HSDC Pro 软件动态重新配置收发器数据速率

- 工作范围为 0.611Gbps 至 6.5Gbps

- 4Gb DDR3 SDRAM。采集或发送高达 256M 16 位样本

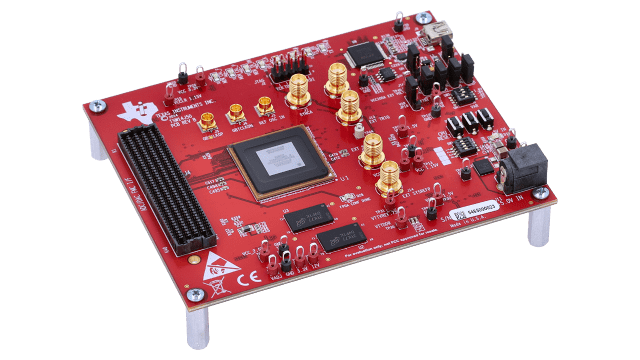

TSW14J50EVM 的说明

德州仪器 (TI) TSW14J50 评估模块 (EVM) 是下一代图形发生器兼数据采集卡,用于评估德州仪器 (TI) JESD204B 系列高速模数转换器 (ADC) 与数模转换器 (DAC) 的性能。

TSW14J50 组装了一个低成本 Altera Arria V GX 器件并采用 Altera 的 JESD204B IP 解决方案,可通过动态配置在 1 到 8 个通道实现 600Mbps 到 6.5Gbps 的速率,并支持多个转换器以及每帧多个八位字节。

结合附带的 High Speed Data Converter Pro 图形用户界面 (HSDC Pro GUI),这套完整的系统从 ADC EVM 采集数据样本并进行评估,然后生成所需的测试图形并发送至 DAC EVM。

有关 12.5Gbps JESD204B 和 8Gb DDR3 SDRAM,请参阅 TSW14J56EVM。