CDCE18005EVM 的特性

通用输入缓冲器可接受 LVPECL、LVDS 或 LVCMOS 电平信令

- 完全可配置的输出包括频率、输出格式和输出偏移

- 用作时钟的多路复用器在三个参考输入和输出之间进行切换

- 通过 AT 截面晶体生成时钟

- 集成 EEPROM 会确定加电时的器件配置

- 低附加抖动性能

- 通用输出块支持高达 5 通道差动、10 通道单端或差动与单端的组合:

- 低附加抖动

- 输出频率高达 1.5GHz

- LVPECL、LVDS、LVCMOS 和专用高速

- 输出摆幅模式

- 独立输出分压器支持 1-80 的分频比

- 对所有输出进行独立限制粗偏移控制

- 灵活输入:

- 两个通用差动输入可接受高达 1500MHz (LVPECL)、800MHz (LVDS) 或 250MHz (LVCMOS) 的频率

- 单个辅助输入可接受单端时钟源或晶振;辅助输入可接受频率范围为 2MHz 至 42MHz 的晶振,或高达 75MHz 的 LVCMOS 输入。

- 时钟发生器模式使用晶振输入。

- 典型电源消耗:在 3.3V 时为 1.0W

- 集成 EEPROM 会存储默认设置;因此,器件可以在已知的预定义状态下加电。

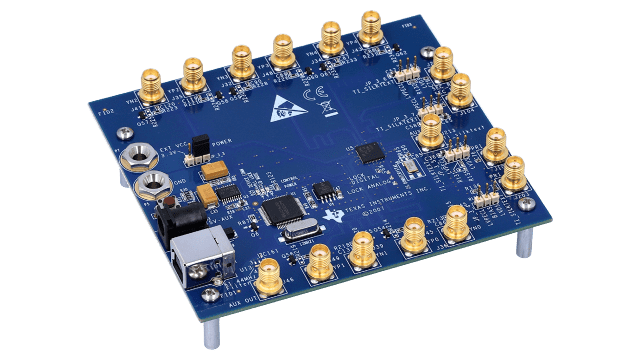

- 采用 QFN-48 封装,图 1 CDCE18005 应用示例

- ESD 保护超过 2kV HBM

- 工业温度范围:-40°C 至 85°C

CDCE18005EVM 的说明

CDCE18005 是高性能时钟发生器和分配器,它具有高度可配置性(通过 SPI 接口进行配置)和由片上 EEPROM 确定的可编程启动模式。专为数据转换器和高速数字信号的缓冲时钟而设计,CDCE18005 实现了 50 fs 范围以内的低附加抖动。时钟分配块包含 5 个独立的可编程输出,它们可以配置成提供不同的输出格式组合(LVPECL、LVDS、LVCMOS)。也可以通过可编程延迟块将每个输出编程为独特的输出频率(高达 1.5GHzGHz)和偏移关系。如果所有输出都采用单端模式(例如 LVCMOS)进行配置,则 CDCE18005 可支持多达 10 路输出。每个输出都可以选择 3 个时钟输入源中的一个。输入块包含两个通用差动输入,它们支持高达 1500MHz 的频率和辅助单端输入,该单端输入可以连接到 CMOS 级时钟或配置为通过板载振荡器块连接到外部晶振。